# Technical Support Center: Overcoming Challenges in GeAs on Silicon Heteroepitaxy

Author: BenchChem Technical Support Team. Date: December 2025

| Compound of Interest |                    |           |

|----------------------|--------------------|-----------|

| Compound Name:       | Germanium arsenide |           |

| Cat. No.:            | B076424            | Get Quote |

This technical support center provides troubleshooting guidance and frequently asked questions (FAQs) to assist researchers, scientists, and drug development professionals in overcoming common challenges encountered during the heteroepitaxy of Gallium Arsenide (GeAs) on Silicon (Si) substrates.

## Frequently Asked Questions (FAQs) & Troubleshooting Guide

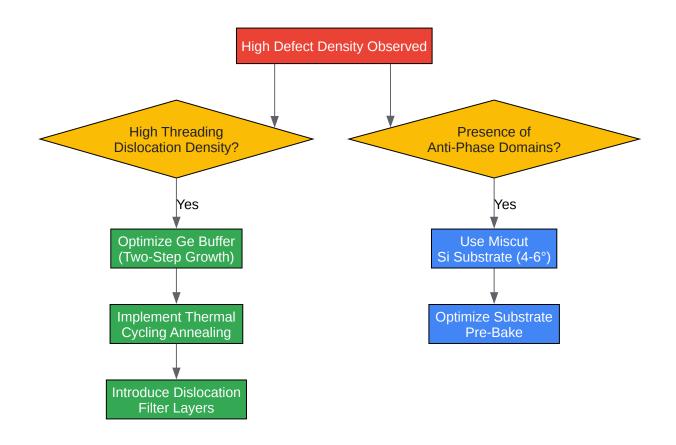

Issue 1: High Density of Threading Dislocations

Q: My GeAs on Si film shows a high threading dislocation density (TDD). What are the primary causes and how can I reduce it?

A: High TDD in GeAs on Si is a common issue primarily arising from the significant lattice mismatch (~4%) and the difference in thermal expansion coefficients between GeAs and Si.[1] Threading dislocations are defects that propagate from the heterointerface into the epitaxial layer, degrading device performance.

#### **Troubleshooting Steps:**

• Optimize the Germanium (Ge) Buffer Layer: A high-quality, fully relaxed Ge buffer layer is crucial for bridging the lattice mismatch between GeAs and Si.

- Two-Step Growth: Employ a two-step growth process for the Ge buffer. This involves a low-temperature (LT) nucleation layer (e.g., 400-450°C) to ensure 2D growth, followed by a high-temperature (HT) growth (e.g., 650°C) to improve crystalline quality.[2][3]

- Buffer Thickness: Ensure the Ge buffer layer is sufficiently thick (e.g., >50 nm for the LT layer and a total thickness of around 1.4 μm) to effectively relax the strain.[4]

- Implement Thermal Cycling Annealing (TCA): TCA is a highly effective method for reducing TDD. The process involves cycling the wafer between a high annealing temperature and a lower temperature multiple times. This promotes dislocation glide and annihilation.

- A typical TCA cycle for a GaAs layer on a Ge buffer involves annealing at 750°C for 5 minutes, followed by cooling to 350°C, repeated for five cycles.[2]

- For Ge buffer layers, annealing at temperatures up to 850°C can be effective.[2][3]

- Introduce Dislocation Filter Layers (DFLs): Strained-layer superlattices (SLSs), such as InGaAs/GaAs, can be grown between the Ge buffer and the GeAs active layer. These layers create strain fields that bend and terminate propagating threading dislocations.

- Optimize Growth Temperature: The growth temperature of the GeAs layer itself can influence defect formation. A multi-temperature growth scheme for GaAs on a Ge buffer has been shown to be effective. This involves a low-temperature (LT) nucleation layer at ~460°C, an intermediate-temperature (IT) layer at ~600°C, and a high-temperature (HT) layer at ~670°C.

Issue 2: Presence of Anti-Phase Domains (APDs)

Q: I am observing anti-phase domains in my GeAs film. What causes them and how can they be eliminated?

A: Anti-phase domains (APDs) are planar defects that form when a polar semiconductor (like GeAs) is grown on a non-polar substrate (like Si).[6] They arise from the presence of single-atom-high steps on the Si surface, leading to a disruption in the sublattice ordering of the GeAs crystal.[7][8]

**Troubleshooting Steps:**

## Troubleshooting & Optimization

- Use Miscut Si Substrates: Employing Si (001) substrates with a miscut angle of 4-6° towards

the <110> direction is a widely accepted method to suppress APDs.[7][8] The miscut

promotes the formation of double-atomic steps on the Si surface during high-temperature

annealing, which prevents the formation of APDs.

- Optimize Substrate Preparation: A thorough pre-growth cleaning and annealing of the Si substrate is critical. High-temperature annealing (e.g., >900°C) in a hydrogen atmosphere helps to form the desired double-stepped surface structure.

- Control Initial Nucleation: The initial nucleation of GeAs on the Si or Ge surface is critical. A two-step growth process, starting with a low-temperature nucleation layer, can help to establish a single-domain growth front.

Issue 3: Poor Surface Morphology (Hazy or Rough Surface)

Q: The surface of my grown GeAs film appears hazy and rough. What are the likely causes and solutions?

A: A hazy or rough surface morphology can be caused by several factors, including threedimensional (3D) island growth, surface contamination, and suboptimal growth parameters.

#### **Troubleshooting Steps:**

- Verify Substrate Cleanliness: Ensure the Si substrate is meticulously cleaned before growth to remove any organic or particulate contamination. Inadequate cleaning can lead to 3D nucleation.

- Optimize V/III Ratio: The ratio of the group V (As) to group III (Ge) precursor flow rates (V/III ratio) significantly impacts surface morphology.

- For MOCVD growth of similar III-V materials, a V/III ratio that is too low can lead to the formation of metallic droplets, while a ratio that is too high can inhibit surface migration and lead to rougher surfaces. The optimal V/III ratio is material and system-dependent and needs to be determined experimentally.[9]

- Control Growth Temperature: The growth temperature affects the surface mobility of adatoms. A temperature that is too low can result in a rough, amorphous-like surface, while a

temperature that is too high can lead to islanding. A multi-temperature growth approach can help to achieve a smooth surface.[5]

Check for Leaks in the Growth System: Leaks in the MOCVD or MBE system can introduce contaminants that degrade surface morphology.

Issue 4: Wafer Bowing

Q: My GeAs on Si wafer is significantly bowed after growth. What is the cause and how can I minimize it?

A: Wafer bowing is primarily caused by the stress resulting from the mismatch in the coefficient of thermal expansion (CTE) between the GeAs/Ge layers and the Si substrate upon cooling from the growth temperature.[10]

**Troubleshooting Steps:**

- Strain Engineering: Introduce layers with tailored strain to counteract the tensile stress from the CTE mismatch. For example, growing a slightly compressively strained layer can help to compensate for the tensile stress upon cooling.

- Optimize Film Thickness: Thicker epitaxial layers generally lead to greater wafer bow. If possible, reduce the total thickness of the epitaxial stack while still meeting device requirements.

- Control Cooling Rate: A slower and more controlled cooling rate after growth can sometimes help to reduce the build-up of thermal stress.

- Use Thicker Substrates: While not always feasible, using a thicker Si substrate can provide

greater mechanical rigidity and reduce the degree of bowing for a given epitaxial layer

thickness.

### **Data Presentation**

Table 1: Material Properties of Si, Ge, and GaAs

| Property                                            | Silicon (Si) | Germanium (Ge) | Gallium Arsenide<br>(GaAs) |

|-----------------------------------------------------|--------------|----------------|----------------------------|

| Lattice Constant (Å)                                | 5.431        | 5.658          | 5.653                      |

| Thermal Expansion Coefficient (10 <sup>-6</sup> /K) | 2.6          | 5.8            | 6.86                       |

Table 2: Typical MOCVD Growth Parameters for High-Quality GeAs on Si with a Ge Buffer

| Parameter                            | Value                                    | Purpose                                      |

|--------------------------------------|------------------------------------------|----------------------------------------------|

| Si Substrate Miscut                  | 4-6° towards <110>                       | Suppress Anti-Phase Domains (APDs)           |

| Ge Buffer LT Growth Temperature      | 400 - 450°C                              | Promote 2D nucleation of Ge                  |

| Ge Buffer HT Growth Temperature      | 650°C                                    | Improve crystalline quality of Ge            |

| Ge Buffer Thickness                  | ~1.4 μm                                  | Strain relaxation                            |

| Ge Buffer Annealing Temperature      | 850°C                                    | Reduce Threading Dislocation Density (TDD)   |

| GaAs LT Nucleation Temperature       | ~460°C                                   | Initiate smooth GaAs growth                  |

| GaAs IT Growth Temperature           | ~600°C                                   | Transition layer                             |

| GaAs HT Growth Temperature           | ~670°C                                   | High-quality GaAs growth                     |

| Thermal Cycling Annealing (for GaAs) | 5 cycles of 750°C (5 min) and 350°C      | Further reduce TDD in the GaAs layer         |

| V/III Ratio                          | Optimized experimentally (typically >10) | Control surface morphology and stoichiometry |

| Resulting TDD                        | ~2.9 x 10 <sup>7</sup> cm <sup>-2</sup>  | High-quality epitaxial layer                 |

| Resulting Surface Roughness (RMS)    | ~1.01 nm                                 | Smooth surface for device fabrication        |

## **Experimental Protocols**

1. Silicon Substrate Cleaning (RCA Clean)

The RCA clean is a standard procedure to remove organic and inorganic contaminants from the silicon wafer surface before epitaxial growth.[5][11]

- Step 1: SC-1 (Standard Clean 1) Organic and Particle Removal

- Prepare a solution of deionized (DI) water, ammonium hydroxide (NH<sub>4</sub>OH), and hydrogen peroxide (H<sub>2</sub>O<sub>2</sub>) in a 5:1:1 ratio.

- Heat the solution to 75-80°C.

- Immerse the silicon wafers in the heated solution for 10 minutes. This step removes organic residues and particles.

- Rinse the wafers thoroughly with DI water.

- Step 2: HF Dip (Optional) Oxide Strip

- Prepare a dilute solution of hydrofluoric acid (HF) in DI water (e.g., 1:50 or 1:100).

- Immerse the wafers in the HF solution for 15-30 seconds to remove the thin chemical oxide formed during the SC-1 step.

- Rinse the wafers thoroughly with DI water.

- Step 3: SC-2 (Standard Clean 2) Ionic Contaminant Removal

- Prepare a solution of DI water, hydrochloric acid (HCl), and hydrogen peroxide (H<sub>2</sub>O<sub>2</sub>) in a

6:1:1 ratio.

- Heat the solution to 75-80°C.

- Immerse the wafers in the heated solution for 10 minutes to remove metallic (ionic) contaminants.

- o Rinse the wafers thoroughly with DI water.

- Step 4: Drying

- Dry the wafers using a spin-rinse dryer or by blowing with high-purity nitrogen gas.

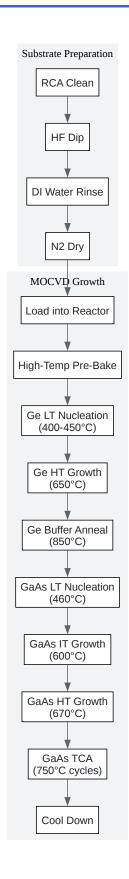

- 2. MOCVD Growth of GeAs on Si with a Ge Buffer

This protocol describes a typical three-step growth process for achieving high-quality GeAs on Si.[2][5]

- Substrate Loading and Pre-Bake: Load the cleaned Si substrate into the MOCVD reactor. Perform a high-temperature bake in a hydrogen (H<sub>2</sub>) atmosphere (e.g., at 1050°C for 10 minutes) to desorb any remaining surface oxide.

- Ge Buffer Layer Growth (Two-Step):

- Low-Temperature (LT) Nucleation: Grow a thin Ge nucleation layer (e.g., 50 nm) at a low temperature of 400-450°C.

- High-Temperature (HT) Growth: Increase the temperature to 650°C and grow the main Ge buffer layer to the desired thickness (e.g., ~1.4 μm).

- Ge Buffer Annealing: Perform in-situ thermal cycling annealing on the Ge buffer layer by ramping the temperature up to 850°C and back down, repeating for several cycles to reduce TDD.[2][3]

- GeAs Layer Growth (Three-Step):

- Low-Temperature (LT) Nucleation: Grow an 18 nm GaAs nucleation layer at 460°C.

- Intermediate-Temperature (IT) Growth: Grow a 120 nm GaAs layer at 600°C.

- High-Temperature (HT) Growth: Grow the final GaAs layer to the desired thickness at 670°C.

- GeAs Layer Annealing: Perform thermal cycling annealing on the GaAs layer (e.g., 5 cycles between 750°C and 350°C) to further reduce the TDD.[2]

- Cool Down: Cool the wafer down to room temperature in a controlled manner.

- 3. Molecular Beam Epitaxy (MBE) Growth of GeAs on Si

MBE offers precise control over the growth process at the atomic level.

- Substrate Preparation: After an ex-situ chemical clean (e.g., RCA clean), load the Si substrate into the MBE system's load-lock chamber.

- In-Situ Cleaning: Transfer the substrate to the growth chamber and perform a hightemperature "flash" anneal (e.g., to ~1200°C for a short duration) to desorb the native oxide and create a clean, reconstructed Si surface.

- Ge Buffer Layer Growth:

- Cool the substrate to the desired growth temperature for Ge (typically in the range of 300-700°C).

- Open the shutter for the Ge effusion cell to begin deposition. A two-step growth process similar to MOCVD can be employed.

- GeAs Layer Growth:

- Set the substrate temperature for GeAs growth (typically 580-620°C).

- Open the shutters for the Ge and As effusion cells simultaneously. The As source is typically a valved cracker cell to provide As<sub>2</sub> or As<sub>4</sub> species.

- Monitor the surface reconstruction in real-time using Reflection High-Energy Electron

Diffraction (RHEED) to ensure proper growth conditions.

- In-Situ Annealing: After growth, the wafer can be annealed in the growth chamber under an As overpressure to improve crystal quality.

- Cool Down and Unloading: Cool the substrate down and transfer it out of the MBE system.

### **Visualizations**

Click to download full resolution via product page

Caption: MOCVD workflow for GeAs on Si heteroepitaxy.

Click to download full resolution via product page

Caption: Troubleshooting decision tree for high defect density.

#### **Need Custom Synthesis?**

BenchChem offers custom synthesis for rare earth carbides and specific isotopiclabeling.

Email: info@benchchem.com or Request Quote Online.

#### References

1. Reduced Dislocation of GaAs Layer Grown on Ge-Buffered Si (001) Substrate Using Dislocation Filter Layers for an O-Band InAs/GaAs Quantum Dot Narrow-Ridge Laser - PMC

[pmc.ncbi.nlm.nih.gov]

- 2. researchgate.net [researchgate.net]

- 3. diva-portal.org [diva-portal.org]

- 4. RCA clean Wikipedia [en.wikipedia.org]

- 5. Review of Highly Mismatched III-V Heteroepitaxy Growth on (001) Silicon PMC [pmc.ncbi.nlm.nih.gov]

- 6. ptc.home.ece.ust.hk [ptc.home.ece.ust.hk]

- 7. matec-conferences.org [matec-conferences.org]

- 8. semiconcleantech.com [semiconcleantech.com]

- 9. inrf.uci.edu [inrf.uci.edu]

- 10. dspace.mit.edu [dspace.mit.edu]

- 11. [PDF] Simultaneous interfacial misfit array formation and antiphase domain suppression on miscut silicon substrate | Semantic Scholar [semanticscholar.org]

- To cite this document: BenchChem. [Technical Support Center: Overcoming Challenges in GeAs on Silicon Heteroepitaxy]. BenchChem, [2025]. [Online PDF]. Available at: [https://www.benchchem.com/product/b076424#overcoming-challenges-in-geas-on-silicon-heteroepitaxy]

#### **Disclaimer & Data Validity:**

The information provided in this document is for Research Use Only (RUO) and is strictly not intended for diagnostic or therapeutic procedures. While BenchChem strives to provide accurate protocols, we make no warranties, express or implied, regarding the fitness of this product for every specific experimental setup.

**Technical Support:**The protocols provided are for reference purposes. Unsure if this reagent suits your experiment? [Contact our Ph.D. Support Team for a compatibility check]

Need Industrial/Bulk Grade? Request Custom Synthesis Quote

## BenchChem

Our mission is to be the trusted global source of essential and advanced chemicals, empowering scientists and researchers to drive progress in science and industry. Contact

Address: 3281 E Guasti Rd

Ontario, CA 91761, United States

Phone: (601) 213-4426

Email: info@benchchem.com