# Technical Support Center: Optimizing ZrSe2-Based Devices

Author: BenchChem Technical Support Team. Date: December 2025

| Compound of Interest |                    |           |

|----------------------|--------------------|-----------|

| Compound Name:       | Zirconium selenide |           |

| Cat. No.:            | B077680            | Get Quote |

This technical support center provides researchers, scientists, and drug development professionals with troubleshooting guides and frequently asked questions (FAQs) to address common challenges encountered during the experimental fabrication and characterization of Zirconium Diselenide (ZrSe2)-based devices, with a focus on reducing interface traps.

## Frequently Asked Questions (FAQs)

Q1: What are interface traps and how do they affect my ZrSe2 device performance?

A1: Interface traps are electronically active defects located at the interface between the ZrSe2 channel and the gate dielectric. These defects can trap and release charge carriers, leading to a degradation of device performance in several ways:

- Reduced Carrier Mobility: Trapped charges can scatter mobile carriers in the channel, reducing their velocity and thus the overall device mobility.

- Increased Subthreshold Swing (SS): A higher density of interface traps leads to a larger subthreshold swing, which means a higher gate voltage is required to switch the transistor from the "off" to the "on" state, resulting in increased power consumption.[1][2]

- Threshold Voltage Instability: Trapping and de-trapping of charges can cause shifts in the threshold voltage, leading to unstable and unreliable device operation.

### Troubleshooting & Optimization

Hysteresis in Transfer Characteristics: The slow trapping and de-trapping of charges can cause a difference in the current-voltage (I-V) curves when sweeping the gate voltage in forward and reverse directions, a phenomenon known as hysteresis.

Q2: What are the common sources of interface traps in ZrSe2 devices?

A2: Interface traps in ZrSe2 devices can originate from several sources:

- ZrSe2 Material Defects: Intrinsic defects in the ZrSe2 crystal lattice, such as selenium (Se) or zirconium (Zr) vacancies, can act as trap states.[3] Chalcogen vacancies are often the most likely type of defect due to their relatively low formation enthalpy.[4]

- Surface Contamination and Residues: Residues from fabrication processes, such as photoresist, solvents, or atmospheric adsorbates on the ZrSe2 surface, can introduce a high density of traps.

- Poor Dielectric Interface: A non-ideal interface between the ZrSe2 and the gate dielectric, often due to dangling bonds, chemical reactions, or lattice mismatch, is a primary source of interface traps.

- Damage during Deposition: High-energy deposition processes for the gate dielectric or metal contacts can induce damage to the atomically thin ZrSe2 lattice, creating defect sites.

Q3: What are the most promising gate dielectrics for ZrSe2-based transistors?

A3: While research is ongoing, high-k dielectrics are favored for their ability to enable strong gate control with a physically thicker film, reducing leakage current. Promising candidates include:

- Zirconium Oxide (ZrO2): As the native oxide of one of the constituent elements of the channel material, ZrO2 is a promising candidate.[4] It has a high dielectric constant and good thermodynamic stability.[4][5]

- Hafnium Oxide (HfO2): HfO2 is another widely used high-k dielectric in the semiconductor industry and has shown good performance with other 2D materials.[6][7]

Aluminum Oxide (Al2O3): Al2O3 is known for its excellent insulating properties and its ability to passivate surfaces by reducing defect densities.[8][9]

Q4: How can I measure the interface trap density (Dit) in my ZrSe2 devices?

A4: Several electrical characterization techniques can be used to quantify the interface trap density:

- Capacitance-Voltage (C-V) Method: The high-frequency/low-frequency (or quasi-static) C-V

method is a widely used technique to extract the energy distribution of interface traps.[10]

- Conductance Method: This is a sensitive technique that measures the loss mechanism at the interface due to trapping and de-trapping of carriers.[11]

- Subthreshold Swing Analysis: The subthreshold swing (SS) is directly related to the interface trap density. While not providing an energy distribution, it offers a quick and straightforward way to estimate the average Dit.

## **Troubleshooting Guides**

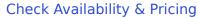

Issue 1: High Subthreshold Swing (SS > 100 mV/dec) and Low On/Off Ratio

| Possible Cause                                                                                                                                        | Troubleshooting Step                                                                                                                                                            | Rationale                                                                                 |

|-------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------|

| High Density of Interface Traps                                                                                                                       | 1. Annealing: Perform post-<br>fabrication annealing in a<br>controlled environment (e.g.,<br>vacuum or N2) at moderate<br>temperatures (e.g., 200-<br>300°C).[12][13]          | Annealing can repair lattice defects and improve the quality of the dielectric interface. |

| 2. Surface Passivation: Deposit a thin passivation layer (e.g., Al2O3) using Atomic Layer Deposition (ALD) prior to gate dielectric deposition.[8][9] | Passivation can saturate dangling bonds and reduce surface defects.                                                                                                             |                                                                                           |

| Poor Quality Dielectric                                                                                                                               | 1. Optimize Deposition: Optimize the deposition parameters of your gate dielectric (e.g., temperature, precursors for ALD).                                                     | A high-quality dielectric with low bulk trap density is crucial for a good interface.     |

| 2. Use a Seeding Layer: A thin seeding layer can sometimes improve the nucleation and quality of the subsequently deposited high-k dielectric.        | This can lead to a more uniform and defect-free dielectric film.                                                                                                                |                                                                                           |

| Contaminated ZrSe2 Surface                                                                                                                            | 1. Pre-deposition Cleaning: Implement a gentle in-situ cleaning step before dielectric deposition, such as a low- power argon plasma treatment or thermal desorption in vacuum. | This removes surface adsorbates and contaminants that can act as traps.                   |

Issue 2: Large Hysteresis in the Transfer Characteristics

# Troubleshooting & Optimization

Check Availability & Pricing

| Possible Cause                                                                                                                                                          | Troubleshooting Step                                                                                                  | Rationale                                                                                                    |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------|

| Slow Trap States                                                                                                                                                        | 1. Annealing: Similar to addressing high SS, annealing can help in reducing the density of slow trap states.[12] [13] | Thermal energy can help in releasing trapped charges and restructuring the interface.                        |

| 2. Dielectric Choice: Experiment with different gate dielectrics. Some dielectrics are known to have a higher density of bulk traps which can contribute to hysteresis. | The choice of dielectric material and its deposition method significantly impacts the interface quality.              |                                                                                                              |

| Moisture/Adsorbates                                                                                                                                                     | Vacuum Measurement:     Perform electrical     measurements in a high-     vacuum environment.                        | This eliminates the influence of atmospheric adsorbates like water and oxygen which can act as charge traps. |

| 2. Encapsulation: Encapsulate the device with a suitable material like h-BN or a high-quality dielectric.                                                               | Encapsulation protects the ZrSe2 channel from the environment.                                                        |                                                                                                              |

Issue 3: High Contact Resistance

| Possible Cause                                                                                                                                                    | Troubleshooting Step                                                                                                                                                      | Rationale                                                                                                               |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------|

| Schottky Barrier at Metal-<br>ZrSe2 Interface                                                                                                                     | 1. Work Function Engineering: Select contact metals with work functions that align well with the band structure of ZrSe2 to minimize the Schottky barrier height.         | A lower Schottky barrier facilitates more efficient charge injection.                                                   |

| 2. Contact Doping: Introduce a thin, highly doped layer at the contact regions to facilitate tunneling.                                                           | This can effectively reduce the contact resistance.                                                                                                                       |                                                                                                                         |

| Interface Contamination                                                                                                                                           | In-situ Contact Deposition:     Deposit contact metals     immediately after ZrSe2     exfoliation or growth in a     vacuum environment without     breaking the vacuum. | This prevents the formation of<br>a resistive oxide layer or<br>adsorption of contaminants at<br>the contact interface. |

| 2. Contact Annealing: Perform annealing after metal deposition at a suitable temperature to promote better adhesion and intermixing at the contact interface.[14] | This can lead to the formation of a more ohmic contact.                                                                                                                   |                                                                                                                         |

## **Quantitative Data Summary**

The following tables summarize the impact of different interface engineering strategies on the performance of 2D material-based field-effect transistors (FETs). Note: Data for ZrSe2 is limited; therefore, data from other relevant 2D materials like MoS2 and WSe2 are included for reference and to suggest promising research directions.

Table 1: Effect of Annealing on Device Performance

| Material | Annealing<br>Conditions | Change in<br>Mobility   | Change in<br>Subthreshold<br>Swing (SS) | Reference |

|----------|-------------------------|-------------------------|-----------------------------------------|-----------|

| MoS2     | 300°C in Ar             | ~10x increase           | ~80% reduction                          | [14]      |

| WSe2     | 350 K in N2             | ~3x increase            | -                                       | [13]      |

| SnO2     | 450°C                   | Increase to 0.19 cm²/Vs | -                                       | [15]      |

Table 2: Impact of Dielectric Choice and Passivation on Interface Trap Density (Dit)

| Material                 | Dielectric/Pass<br>ivation | Dit (cm-2eV-1)                               | Method                  | Reference |

|--------------------------|----------------------------|----------------------------------------------|-------------------------|-----------|

| Si                       | Al2O3                      | Low Dit                                      | C-V                     | [16]      |

| SiC                      | HfO2                       | -                                            | C-V, G-V                | [17]      |

| Organic<br>Semiconductor | Cytop                      | ~2 orders of<br>magnitude lower<br>than SiO2 | Electrical<br>Transport | [18]      |

# **Experimental Protocols**

Protocol 1: Fabrication of a Top-Gated ZrSe2 FET with ALD-Grown Al2O3 Passivation

- Substrate Preparation: Start with a heavily doped Si substrate with a thermally grown SiO2 layer (e.g., 300 nm) to be used as a back gate.

- ZrSe2 Exfoliation and Transfer: Mechanically exfoliate few-layer ZrSe2 flakes from a bulk crystal onto the SiO2/Si substrate.

- Contact Patterning and Deposition:

- Use electron-beam lithography (EBL) to define the source and drain contact areas.

- Deposit contact metals (e.g., Ti/Au, 5 nm/50 nm) using electron-beam evaporation.

- o Perform lift-off in a suitable solvent.

- Al2O3 Passivation:

- Transfer the sample to an Atomic Layer Deposition (ALD) chamber.

- Deposit a thin layer of Al2O3 (e.g., 1-2 nm) at a relatively low temperature (e.g., 150-200°C) to act as a passivation layer.

- Gate Dielectric Deposition:

- Without breaking vacuum if possible, continue with the ALD deposition of the main gate dielectric (e.g., 20-30 nm of HfO2 or ZrO2).

- Top Gate Definition:

- Use EBL to define the top gate electrode.

- Deposit the top gate metal (e.g., Ni/Au, 10 nm/50 nm) via e-beam evaporation.

- Perform lift-off.

- Post-Fabrication Annealing:

- Anneal the device in a high-vacuum or nitrogen environment at 200-300°C for 1-2 hours.

Protocol 2: Characterization of Interface Trap Density using the C-V Method

- Device Structure: A Metal-Oxide-Semiconductor Capacitor (MOSCAP) structure is ideal for this measurement. This can be a large area top-gated structure on your ZrSe2 flake.

- Measurement Setup: Use a precision LCR meter connected to a probe station.

- Quasi-Static C-V (QSCV) Measurement:

- Apply a slow sweeping DC voltage to the gate and measure the resulting current to determine the quasi-static capacitance (Cqs).

- High-Frequency C-V (HFCV) Measurement:

Apply a DC gate bias with a superimposed small AC signal (typically 1 MHz) and measure the capacitance (Chf).

#### • Dit Extraction:

- The interface trap capacitance (Cit) can be calculated from the difference between the low-frequency and high-frequency capacitance.

- The interface trap density (Dit) is then calculated using the formula: Dit = Cit / qA, where q is the elementary charge and A is the area of the capacitor.

### **Visualizations**

Click to download full resolution via product page

Caption: Experimental workflow for fabricating a passivated ZrSe2 FET.

Click to download full resolution via product page

Caption: Troubleshooting logic for high subthreshold swing in ZrSe2 devices.

#### **Need Custom Synthesis?**

BenchChem offers custom synthesis for rare earth carbides and specific isotopiclabeling.

Email: info@benchchem.com or Request Quote Online.

### References

### Troubleshooting & Optimization

- 1. taylorfrancis.com [taylorfrancis.com]

- 2. ciqm.harvard.edu [ciqm.harvard.edu]

- 3. poplab.stanford.edu [poplab.stanford.edu]

- 4. mdpi.com [mdpi.com]

- 5. Molecular sieves assisted chemical vapor deposition preparation of high-<i>κ</i> dielectric m-ZrO<sub>2</sub> nanosheets [jos.ac.cn]

- 6. researchgate.net [researchgate.net]

- 7. mdpi.com [mdpi.com]

- 8. Design of Grating Al2O3 Passivation Structure Optimized for High-Efficiency Cu(In,Ga)Se2 Solar Cells - PMC [pmc.ncbi.nlm.nih.gov]

- 9. researchgate.net [researchgate.net]

- 10. researchgate.net [researchgate.net]

- 11. engineering.purdue.edu [engineering.purdue.edu]

- 12. researchgate.net [researchgate.net]

- 13. High-Temperature Annealing Effects on Atomically Thin Tungsten Diselenide Field-Effect Transistor [mdpi.com]

- 14. Reducing MoS2 FET contact resistance by stepped annealing to optimize device performance Journal of Materials Chemistry C (RSC Publishing) [pubs.rsc.org]

- 15. Effect of Annealing Temperature on the Performance of SnO2 Thin Film Transistors Prepared by Spray Pyrolysis PubMed [pubmed.ncbi.nlm.nih.gov]

- 16. researchgate.net [researchgate.net]

- 17. pdfs.semanticscholar.org [pdfs.semanticscholar.org]

- 18. uknowledge.uky.edu [uknowledge.uky.edu]

- To cite this document: BenchChem. [Technical Support Center: Optimizing ZrSe2-Based Devices]. BenchChem, [2025]. [Online PDF]. Available at: [https://www.benchchem.com/product/b077680#reducing-interface-traps-in-zrse2-based-devices]

#### **Disclaimer & Data Validity:**

The information provided in this document is for Research Use Only (RUO) and is strictly not intended for diagnostic or therapeutic procedures. While BenchChem strives to provide

accurate protocols, we make no warranties, express or implied, regarding the fitness of this product for every specific experimental setup.

**Technical Support:** The protocols provided are for reference purposes. Unsure if this reagent suits your experiment? [Contact our Ph.D. Support Team for a compatibility check]

Need Industrial/Bulk Grade? Request Custom Synthesis Quote

# BenchChem

Our mission is to be the trusted global source of essential and advanced chemicals, empowering scientists and researchers to drive progress in science and industry. Contact

Address: 3281 E Guasti Rd

Ontario, CA 91761, United States

Phone: (601) 213-4426

Email: info@benchchem.com