# Technical Support Center: Optimizing Ultrathin Gallium Arsenide (GaAs) Transistor Performance

Author: BenchChem Technical Support Team. Date: December 2025

| Compound of Interest |                  |           |

|----------------------|------------------|-----------|

| Compound Name:       | Gallium arsenide |           |

| Cat. No.:            | B074776          | Get Quote |

This technical support center provides troubleshooting guidance and frequently asked questions (FAQs) to assist researchers, scientists, and drug development professionals in optimizing the performance of ultrathin **gallium arsenide** (GaAs) transistors during their experiments.

## Frequently Asked Questions (FAQs)

Q1: What are the most common causes of poor performance in ultrathin GaAs transistors?

A1: The primary factors leading to suboptimal performance in ultrathin GaAs transistors include high contact resistance, poor surface passivation leading to a high density of surface states, inherent crystal defects in the GaAs material, and degradation due to metal-semiconductor interdiffusion.[1][2] Low thermal conductivity of GaAs can also lead to heat-related performance issues.[2]

Q2: How does surface passivation affect transistor performance?

A2: Unpassivated GaAs surfaces typically have a high density of surface states which can pin the Fermi level and lead to high non-radiative recombination rates.[3] Effective surface passivation reduces these surface states, which in turn can decrease surface recombination velocity, increase carrier lifetime, and improve the overall stability and electrical properties of the transistor.[4]

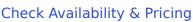

Q3: What is the "gate-first" process and why is it used?

A3: The "gate-first" process is a fabrication sequence where the gate metal is deposited and defined before the source and drain contacts are formed.[5] This approach is often used in self-aligned processes. A key consideration in this process is that the subsequent high-temperature annealing required to form low-resistance ohmic source and drain contacts can potentially damage the gate if the gate metal is not thermally stable.[5]

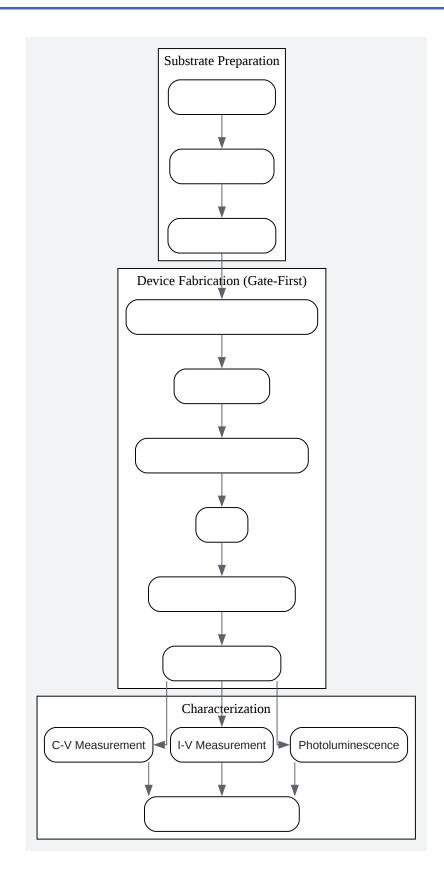

Q4: What are the typical I-V characteristic changes observed in degraded GaAs transistors?

A4: Degraded GaAs transistors can exhibit several changes in their current-voltage (I-V) characteristics. These may include a negative shift in the threshold voltage (VT), an increase in gate leakage current, and a decrease in the saturated drain-source current.[6] In some cases of high-field stress, hot electrons can generate traps, leading to an increase in the depletion region between the gate and drain, which manifests as an increased drain resistance.[6]

# **Troubleshooting Guides Issue 1: High Contact Resistance**

Symptom: The measured resistance between the metal contacts and the semiconductor channel is excessively high, leading to poor device performance.

Possible Causes and Solutions:

| Cause                         | Suggested Solution                                                                                                                                                                                                                                                                                                        |

|-------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Improper Annealing Conditions | The annealing temperature and duration are critical for forming low-resistance ohmic contacts. For AuGe/Ni/Au contacts, the specific contact resistivity is highly dependent on these parameters. An annealing temperature around 420°C for 60-80 seconds has been shown to yield low specific contact resistivity.[7][8] |

| Surface Contamination         | The GaAs surface must be thoroughly cleaned before metal deposition to ensure a good metal-semiconductor interface. Any residual oxides or contaminants can significantly increase contact resistance.                                                                                                                    |

| Incorrect Metal Stack         | The choice and thickness of metals in the contact stack are crucial. A common and effective combination for n-type GaAs is an AuGe/Ni/Au multilayer.[9]                                                                                                                                                                   |

## **Issue 2: Low Electron Mobility**

Symptom: The measured electron mobility in the transistor channel is significantly lower than theoretical values, limiting the device's switching speed and on-current.

Possible Causes and Solutions:

| Cause                          | Suggested Solution                                                                                                                                                                                              |

|--------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| High Density of Surface States | A poorly passivated GaAs surface will have a high density of states that can scatter electrons and reduce mobility. Employing a suitable surface passivation technique is essential.                            |

| Crystal Defects                | Inherent defects in the GaAs crystal lattice, such as dislocations and point defects, act as scattering centers for electrons.[2] The quality of the initial GaAs wafer is therefore critical.                  |

| Interface Roughness            | A rough interface between the GaAs channel and the gate dielectric can increase electron scattering. Optimization of the deposition process for the dielectric layer is necessary to ensure a smooth interface. |

# **Quantitative Data Summary**

Table 1: Effect of Annealing Temperature on Specific Contact Resistivity of Ni/Ge/Ni/Au Ohmic Contacts on n-GaAs

| Annealing Temperature (°C) | Annealing Time (s) | Specific Contact<br>Resistivity (Ω·cm²) |

|----------------------------|--------------------|-----------------------------------------|

| 370                        | -                  | Schottky contact behavior               |

| >380                       | -                  | Ohmic contact behavior                  |

| 420                        | 80                 | 3.3 x 10 <sup>-5</sup>                  |

| 420                        | 60                 | 2.76 x 10 <sup>-6</sup>                 |

Data synthesized from multiple sources indicating the trend of contact behavior and optimal values found in specific experiments.[7][8]

# **Experimental Protocols**

### Protocol 1: AuGe/Ni/Au Ohmic Contact Formation

Objective: To create low-resistance ohmic contacts on n-type GaAs.

#### Methodology:

- Surface Preparation:

- Thoroughly clean the GaAs substrate using a standard solvent cleaning process (e.g., acetone, isopropanol, deionized water).

- Perform a native oxide etch using a solution such as dilute HCl or NH₄OH.

- Immediately transfer the substrate to a high-vacuum deposition chamber.

- Metal Deposition:

- Sequentially deposit the following metal layers using electron-beam evaporation:

- Nickel (Ni): ~5 nm

- Gold-Germanium (AuGe) eutectic alloy (88/12 wt%): ~100 nm

- Nickel (Ni): ~25 nm

- Gold (Au): ~200 nm

- Lift-off:

- Perform a lift-off process to define the contact pads.

- Annealing:

- Anneal the sample using rapid thermal annealing (RTA).

- A typical annealing condition is 420°C for 60-80 seconds in a nitrogen or hydrogen atmosphere.[7][8]

### **Protocol 2: Plasma-Based Surface Passivation**

Objective: To passivate the GaAs surface to reduce surface states.

#### Methodology:

- Sample Loading:

- Place the GaAs sample into a plasma-enhanced chemical vapor deposition (PECVD) or inductively coupled plasma (ICP) chamber.

- Hydrogen Plasma Treatment:

- Introduce hydrogen gas into the chamber.

- Apply an ICP power of around 300 W and an RF power of 20 W at a pressure of approximately 50 mTorr.[3]

- This step removes native oxides and surface arsenic, creating a Ga-rich surface.

- Nitridation Step:

- Without breaking vacuum, introduce nitrogen gas.

- Apply a nitrogen plasma to form a thin, passivating gallium nitride (GaN) layer.

- Dielectric Deposition (Optional but Recommended):

- Deposit a layer of silicon nitride (SiNx) or silicon dioxide (SiO2) using PECVD to provide a robust encapsulation of the passivated surface.[4][10]

## Protocol 3: Capacitance-Voltage (C-V) Measurement

Objective: To characterize the quality of the gate dielectric and the semiconductor-dielectric interface.

#### Methodology:

• Device Preparation:

- Fabricate Metal-Oxide-Semiconductor (MOS) capacitors on the GaAs substrate. This

involves depositing the gate dielectric followed by a metal gate electrode.

- Measurement Setup:

- Use a parameter analyzer with a C-V measurement unit.

- Connect the high potential terminal to the metal gate and the low potential terminal to the backside of the GaAs substrate.[11]

- Measurement Procedure:

- Apply a DC voltage sweep across the MOS capacitor while superimposing a small AC voltage signal (typically in the millivolt range).[11]

- Measure the resulting capacitance at various DC bias points.

- For GaAs, it may be necessary to perform measurements at elevated temperatures (e.g., 150°C) to characterize slow mid-gap trapping states.[12]

- Data Analysis:

- Plot the measured capacitance as a function of the applied DC voltage.

- From the C-V curve, parameters such as oxide thickness, doping concentration, flatband voltage, and interface state density can be extracted.[11]

## **Visualizations**

Click to download full resolution via product page

#### **Need Custom Synthesis?**

BenchChem offers custom synthesis for rare earth carbides and specific isotopiclabeling.

Email: info@benchchem.com or Request Quote Online.

## References

- 1. scispace.com [scispace.com]

- 2. Low temperature photoluminescence study of GaAs defect states [cpb.iphy.ac.cn]

- 3. acris.aalto.fi [acris.aalto.fi]

- 4. fastercapital.com [fastercapital.com]

- 5. m.youtube.com [m.youtube.com]

- 6. Degradation Mechanisms for GaN and GaAs High Speed Transistors | MDPI [mdpi.com]

- 7. researchgate.net [researchgate.net]

- 8. researchgate.net [researchgate.net]

- 9. files01.core.ac.uk [files01.core.ac.uk]

- 10. pubs.acs.org [pubs.acs.org]

- 11. download.tek.com [download.tek.com]

- 12. docs.lib.purdue.edu [docs.lib.purdue.edu]

- To cite this document: BenchChem. [Technical Support Center: Optimizing Ultrathin Gallium Arsenide (GaAs) Transistor Performance]. BenchChem, [2025]. [Online PDF]. Available at: [https://www.benchchem.com/product/b074776#optimizing-the-performance-of-ultrathingallium-arsenide-transistors]

#### **Disclaimer & Data Validity:**

The information provided in this document is for Research Use Only (RUO) and is strictly not intended for diagnostic or therapeutic procedures. While BenchChem strives to provide accurate protocols, we make no warranties, express or implied, regarding the fitness of this product for every specific experimental setup.

**Technical Support:** The protocols provided are for reference purposes. Unsure if this reagent suits your experiment? [Contact our Ph.D. Support Team for a compatibility check]

Need Industrial/Bulk Grade? Request Custom Synthesis Quote

## BenchChem

Our mission is to be the trusted global source of essential and advanced chemicals, empowering scientists and researchers to drive progress in science and industry. Contact

Address: 3281 E Guasti Rd

Ontario, CA 91761, United States

Phone: (601) 213-4426

Email: info@benchchem.com