# Technical Support Center: Optimizing TIPS-TAP Transistor Performance

Author: BenchChem Technical Support Team. Date: December 2025

| Compound of Interest |           |           |

|----------------------|-----------|-----------|

| Compound Name:       | Tips-tap  |           |

| Cat. No.:            | B14037076 | Get Quote |

This technical support center provides troubleshooting guides and frequently asked questions (FAQs) to assist researchers, scientists, and drug development professionals in improving the on/off ratio of 6,13-Bis(triisopropylsilylethynyl)-5,7,12,14-tetraazapentacene (**TIPS-TAP**) transistors. While specific literature on **TIPS-TAP** is limited, we will draw upon established findings from the closely related and well-studied compound, TIPS-Pentacene, to provide actionable guidance.

## Frequently Asked Questions (FAQs)

Q1: What is a typical on/off ratio for solution-processed organic thin-film transistors (OTFTs), and what should I target for **TIPS-TAP**?

A high on/off ratio is crucial for the proper functioning of a transistor as a switch, ensuring a clear distinction between its "on" and "off" states. For solution-processed OTFTs, on/off ratios can vary widely depending on the material, fabrication process, and device architecture. While a ratio of 10^5 is often considered good, high-performance devices can achieve ratios greater than 10^7.[1][2] For your **TIPS-TAP** transistors, a target on/off ratio of at least 10^5 is a good starting point for most applications.

Q2: How does the choice of solvent impact the on/off ratio of my TIPS-TAP transistors?

The solvent used to deposit the **TIPS-TAP** active layer significantly influences the film morphology, crystallinity, and ultimately, the transistor's performance. Solvents with higher boiling points tend to evaporate more slowly, allowing more time for the organic semiconductor

molecules to self-assemble into well-ordered crystalline domains. This improved crystallinity generally leads to higher charge carrier mobility and a better on/off ratio.[3][4]

Q3: What is the role of thermal annealing in improving the on/off ratio?

Thermal annealing is a post-deposition heat treatment that can improve the crystallinity and reduce defects in the semiconductor film. For TIPS-Pentacene, annealing has been shown to enhance molecular ordering and improve electrical performance.[5][6] It is highly probable that a similar thermal annealing step will be beneficial for improving the on/off ratio of your **TIPS-TAP** transistors by reducing the off-current.

Q4: Can the gate dielectric material affect the on/off ratio?

Yes, the gate dielectric plays a critical role. A high-quality dielectric with low leakage current is essential for achieving a low off-current and consequently a high on/off ratio. The interface between the dielectric and the semiconductor is also crucial. A smooth, defect-free interface facilitates efficient charge transport in the "on" state and minimizes charge trapping that can contribute to leakage current in the "off" state.

## **Troubleshooting Guide**

This guide addresses common issues encountered during the fabrication and testing of **TIPS-TAP** transistors that can lead to a poor on/off ratio.

# Troubleshooting & Optimization

Check Availability & Pricing

| Problem          | Potential Causes                                                                                                                                                                                                                                                                                                                  | Troubleshooting Steps & Solutions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| High OFF-Current | 1. Poor Film Morphology: Disordered or amorphous film structure leading to leakage pathways. 2. Gate Dielectric Leakage: Defects or poor quality of the insulating layer. 3. Interface Traps: Charge trapping states at the semiconductor-dielectric interface. 4. Residual Solvent/Impurities: Contaminants in the active layer. | 1. Optimize Solvent and Deposition: Use a high-boiling- point solvent (e.g., chlorobenzene, p-xylene) to slow down crystallization and improve film order.[3][4] Experiment with different deposition techniques like spin-coating speed or dip- coating withdrawal speed. 2. Improve Dielectric Quality: Ensure a pinhole-free dielectric layer. Consider using a cross- linked polymer dielectric like PVP for better insulating properties.[1] 3. Surface Treatment: Treat the dielectric surface with a self-assembled monolayer (SAM) like HMDS to improve the interface quality and reduce traps. 4. Optimize Annealing: Implement a post- deposition annealing step. Experiment with different temperatures and durations to remove residual solvent and improve crystallinity.[5][6] |

| Low ON-Current   | 1. Poor Crystallinity: Small grain size and numerous grain boundaries hindering charge transport. 2. High Contact Resistance: A large energy barrier between the source/drain electrodes and                                                                                                                                      | 1. Enhance Crystallinity: As with high off-current, optimize the solvent and annealing process to promote the growth of larger, well-connected crystalline domains.[3][5] 2. Select Appropriate Electrode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

## Troubleshooting & Optimization

Check Availability & Pricing

the TIPS-TAP semiconductor.

3. Sub-optimal Film Thickness:

The active layer may be too

thin or too thick for efficient

charge transport.

Material: Use high work function metals (e.g., Gold) for p-type semiconductors to facilitate hole injection.

Consider treating the electrode surface to reduce the injection barrier. 3. Optimize Film

Thickness: Systematically vary the concentration of the TIPS-TAP solution or the deposition parameters to find the optimal film thickness for your device architecture.

Inconsistent Results Between Devices

1. Non-uniform Film

Deposition: Variations in film

thickness and morphology

across the substrate. 2.

Inconsistent Annealing:

Temperature gradients across

the hotplate. 3. Variations in

Electrode Deposition:

Inconsistent shadow mask

contact or evaporation rates.

1. Refine Deposition Technique: Ensure a clean and vibration-free environment. For spin-coating, optimize acceleration and spin speed for uniform coverage. 2. Ensure Uniform Heating: Use a calibrated hotplate with uniform temperature distribution. Consider annealing in a vacuum oven for better temperature control. 3. Control Electrode Deposition: Ensure the shadow mask is in intimate contact with the substrate. Monitor the deposition rate and thickness using a quartz crystal microbalance.

# **Quantitative Data Summary**

The following tables summarize key performance parameters for TIPS-Pentacene transistors fabricated under different conditions. This data can serve as a valuable reference for optimizing your **TIPS-TAP** devices.

Table 1: Effect of Solvent on TIPS-Pentacene Transistor Performance

| Solvent       | Boiling Point<br>(°C) | Field-Effect<br>Mobility<br>(cm²/V·s) | On/Off Ratio          | Threshold<br>Voltage (V) |

|---------------|-----------------------|---------------------------------------|-----------------------|--------------------------|

| Chlorobenzene | 132                   | 1.0 x 10 <sup>-2</sup>                | 4.3 x 10 <sup>3</sup> | 5.5                      |

| p-Xylene      | 138                   | -                                     | -                     | -                        |

| Toluene       | 111                   | -                                     | -                     | -                        |

| Chloroform    | 61                    | 5.8 x 10 <sup>-7</sup>                | 1.1 x 10 <sup>2</sup> | 1.7                      |

Data extracted from a study on TIPS-Pentacene OTFTs. The trend suggests that higher boiling point solvents lead to better performance.[3][4]

Table 2: Effect of Annealing Temperature on TIPS-Pentacene Transistor Performance (Solvent: Toluene)

| Annealing Temperature (°C) | Field-Effect Mobility (cm²/V·s) |  |

|----------------------------|---------------------------------|--|

| No Annealing               | -                               |  |

| 120                        | -                               |  |

| 150                        | $4.5 \times 10^{-3}$            |  |

Data from a study on the optimization of TIPS-Pentacene transistors. The highest mobility for toluene was achieved at 150°C.[5]

# **Experimental Protocols**

Protocol 1: Fabrication of a Bottom-Gate, Top-Contact TIPS-TAP OTFT

## Troubleshooting & Optimization

This protocol is adapted from a standard procedure for fabricating solution-processed organic transistors.

#### Substrate Cleaning:

- Thoroughly clean a heavily doped n-type silicon wafer with a thermally grown SiO<sub>2</sub> layer (gate dielectric).

- Sonication in a sequence of detergent, deionized water, acetone, and isopropanol (15 minutes each).

- Dry the substrate with a stream of nitrogen gas.

- Treat the substrate with UV-Ozone for 15 minutes to remove organic residues.

- Dielectric Surface Treatment (Optional but Recommended):

- Apply a self-assembled monolayer (SAM) of hexamethyldisilazane (HMDS) to the SiO<sub>2</sub> surface to improve the film adhesion and interface quality. This can be done by spin-coating or vapor deposition.

#### • TIPS-TAP Solution Preparation:

- Prepare a solution of TIPS-TAP in a high-boiling-point solvent (e.g., chlorobenzene, toluene, or p-xylene) at a concentration of 5-10 mg/mL.

- Stir the solution on a hotplate at a slightly elevated temperature (e.g., 40-60°C) for several hours to ensure complete dissolution.

- Before use, filter the solution through a 0.2 μm PTFE syringe filter.

#### TIPS-TAP Film Deposition:

- Deposit the TIPS-TAP solution onto the substrate using a technique such as spin-coating or dip-coating.

- Spin-Coating Example: Dispense the solution onto the center of the substrate and spin at 1000-3000 rpm for 30-60 seconds.

- Allow the film to dry at room temperature.

- · Thermal Annealing:

- Anneal the substrate on a hotplate in a nitrogen-filled glovebox or a vacuum oven.

- Typical annealing temperatures for similar organic semiconductors are in the range of 100-150°C for 10-30 minutes. The optimal conditions for TIPS-TAP should be determined experimentally.

- Source-Drain Electrode Deposition:

- Deposit Gold (Au) source and drain electrodes (typically 50-100 nm thick) through a shadow mask using thermal evaporation.

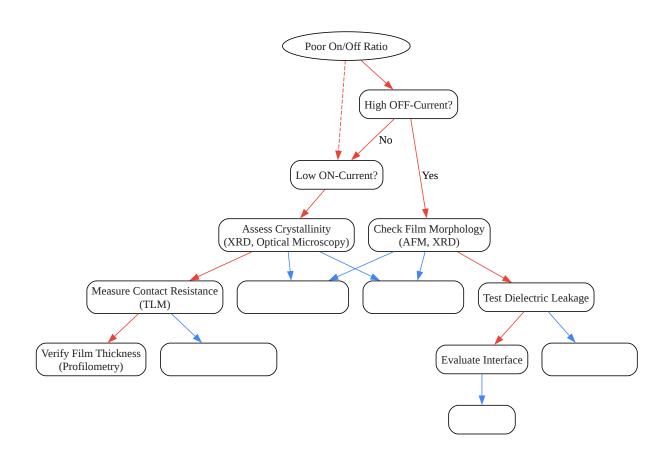

## **Diagrams**

Click to download full resolution via product page

Caption: Experimental workflow for **TIPS-TAP** transistor fabrication.

Click to download full resolution via product page

Caption: Troubleshooting logic for a low on/off ratio.

#### **Need Custom Synthesis?**

BenchChem offers custom synthesis for rare earth carbides and specific isotopiclabeling.

Email: info@benchchem.com or Request Quote Online.

### References

- 1. researchgate.net [researchgate.net]

- 2. researchgate.net [researchgate.net]

- 3. researchgate.net [researchgate.net]

- 4. researchgate.net [researchgate.net]

- 5. Optimization of 6,13Bis(triisopropylsilylethynyl)pentacene (TIPS-Pentacene) Organic Field Effect Transistor: Annealing Temperature and Solvent Effects - Materials Sciences and Applications - SCIRP [scirp.org]

- 6. indico.cern.ch [indico.cern.ch]

- To cite this document: BenchChem. [Technical Support Center: Optimizing TIPS-TAP Transistor Performance]. BenchChem, [2025]. [Online PDF]. Available at: [https://www.benchchem.com/product/b14037076#how-to-improve-the-on-off-ratio-of-tips-tap-transistors]

#### **Disclaimer & Data Validity:**

The information provided in this document is for Research Use Only (RUO) and is strictly not intended for diagnostic or therapeutic procedures. While BenchChem strives to provide accurate protocols, we make no warranties, express or implied, regarding the fitness of this product for every specific experimental setup.

**Technical Support:**The protocols provided are for reference purposes. Unsure if this reagent suits your experiment? [Contact our Ph.D. Support Team for a compatibility check]

Need Industrial/Bulk Grade? Request Custom Synthesis Quote

## BenchChem

Our mission is to be the trusted global source of essential and advanced chemicals, empowering scientists and researchers to drive progress in science and industry. Contact

Address: 3281 E Guasti Rd

Ontario, CA 91761, United States

Phone: (601) 213-4426

Email: info@benchchem.com

© 2025 BenchChem. All rights reserved.