# Technical Support Center: Optimizing Silicon Wafer Manufacturing for Higher Yield

Author: BenchChem Technical Support Team. Date: December 2025

| Compound of Interest |          |           |

|----------------------|----------|-----------|

| Compound Name:       | Silicon  |           |

| Cat. No.:            | B1239273 | Get Quote |

This technical support center provides troubleshooting guides and frequently asked questions (FAQs) to assist researchers, scientists, and drug development professionals in optimizing process parameters for **silicon** wafer manufacturing. The following sections address common issues encountered during key fabrication steps, offering solutions and detailed experimental protocols to enhance process yield.

## **Troubleshooting Guides & FAQs**

This section is organized by common manufacturing processes. Each Q&A directly addresses specific issues and provides actionable solutions.

### **Photolithography**

Q1: What are the common causes of photoresist adhesion failure and how can they be prevented?

A1: Photoresist adhesion failure, leading to pattern lifting or distortion, is a frequent issue. Key causes include moisture on the wafer surface, improper surface preparation, and incorrect application of adhesion promoters.

#### **Troubleshooting Steps:**

Dehydration Bake: Ensure the wafer is properly dehydrated by baking it on a hot plate before applying the adhesion promoter. A common practice is to bake at 150°C for at least 30 minutes.

- Adhesion Promoter Application: Use an appropriate adhesion promoter, such as Hexamethyldisilazane (HMDS). Apply it in a controlled environment, ensuring uniform coverage.

- Surface Contamination: Clean the wafer surface thoroughly to remove any organic or particulate contamination before the dehydration bake.

Q2: How can I optimize exposure dose to improve pattern resolution and reduce defects?

A2: Incorrect exposure dose is a primary cause of critical dimension (CD) variations and pattern defects.[1][2] Over-exposure can lead to pattern thinning, while under-exposure can result in incomplete development.

#### Optimization Strategy:

- Dose Test Matrix: Perform a dose matrix experiment, varying the exposure energy across a wafer.

- CD Measurement: Measure the resulting feature sizes using a scanning electron microscope (SEM).

- Process Window Analysis: Plot the CD variation against the exposure dose to determine the

optimal process window where the desired CD is achieved with the lowest sensitivity to dose

variations. Lowering the post-exposure bake (PEB) temperature can also help in reducing

stress-related defects like resist cracks.[3]

## **Plasma Etching**

Q1: My plasma etch process is showing poor anisotropy, resulting in undercut features. How can I improve the directionality of the etch?

A1: Poor anisotropy is often due to excessive chemical etching relative to physical bombardment or improper passivation of sidewalls.

#### **Corrective Actions:**

Increase Ion Bombardment: Increase the RF bias power to enhance the directionality of ion bombardment. This physically removes material in the vertical direction more effectively than

in the lateral direction.

- Adjust Gas Chemistry: Introduce a passivating gas (e.g., a fluorocarbon gas in silicon etching) to protect the feature sidewalls from lateral etching.

- Lower Pressure: Reducing the chamber pressure increases the mean free path of ions, leading to more directional bombardment.

Q2: What causes etch residue or "grass" on the wafer surface after plasma etching, and how can it be removed?

A2: Etch residue can be caused by micromasking from contaminants, redeposition of sputtered material, or the formation of non-volatile etch byproducts.

#### Mitigation and Removal:

- Pre-Etch Clean: Ensure the wafer surface is free of particles and contaminants before etching.

- Optimize Etch Parameters: Adjust the gas chemistry and plasma power to ensure that all etch byproducts are volatile and can be effectively pumped out of the chamber.[4]

- Post-Etch Clean: Implement a post-etch cleaning step, which can be a wet chemical clean or a downstream plasma ash, to remove any remaining residues.

## **Chemical-Mechanical Planarization (CMP)**

Q1: I am observing a high number of micro-scratches on my wafers after CMP. What are the likely causes and solutions?

A1: Micro-scratches are a common CMP defect, often caused by large abrasive particles in the slurry, agglomeration of slurry particles, or debris from the polishing pad.

#### **Troubleshooting Measures:**

• Slurry Filtration: Implement point-of-use filtration for the slurry to remove oversized particles before they reach the wafer.

- Pad Conditioning: Optimize the pad conditioning process to remove embedded particles and maintain a consistent pad surface.

- Slurry Chemistry: Ensure the slurry chemistry is stable to prevent particle agglomeration. The pH of the slurry can significantly impact the removal rate and defectivity.[5]

Q2: How can I control the material removal rate (MRR) and improve planarity during CMP?

A2: The MRR and planarity are influenced by a combination of mechanical and chemical factors in the CMP process.[6]

#### **Process Optimization:**

- Preston's Equation: The MRR is generally proportional to the applied pressure and the relative velocity between the wafer and the pad. Adjusting these parameters is the primary way to control the removal rate.

- Slurry Composition: The chemical composition of the slurry, including the type and concentration of abrasives and chemical additives, plays a crucial role in the removal mechanism.[7]

- Pad Properties: The hardness and design of the polishing pad also affect the planarity and defectivity.

## **Thin Film Deposition**

Q1: My deposited thin films have poor adhesion and are peeling off. What steps can I take to improve adhesion?

A1: Poor adhesion is often due to a contaminated substrate surface, improper substrate temperature, or high residual stress in the film.[8]

#### Solutions:

Substrate Cleaning: A thorough pre-deposition cleaning process is critical to remove any surface contaminants that can interfere with film adhesion. This can include solvent cleaning, ultrasonic cleaning, and in-situ plasma cleaning.[8][9]

- Substrate Heating: Heating the substrate during deposition can increase the mobility of adatoms, leading to a denser film with better adhesion.

- Stress Control: High intrinsic stress in the film can cause it to peel. Optimizing deposition parameters such as pressure, temperature, and deposition rate can help to minimize stress.

[9]

Q2: The thickness of my deposited film is not uniform across the wafer. How can I achieve better uniformity?

A2: Film thickness non-uniformity can be caused by the geometry of the deposition system, shadowing effects, or non-uniform distribution of the deposition flux.

#### Improvement Strategies:

- Substrate Rotation: Rotating the substrate during deposition is a common and effective method to average out variations in the deposition flux and improve uniformity.

- Source-to-Substrate Distance: Adjusting the distance between the deposition source and the substrate can impact the uniformity.

- Process Parameters: Optimizing parameters like pressure and gas flow can influence the distribution of the plasma and the deposition species, thereby affecting uniformity.

## **Quantitative Data Summary**

The following tables summarize the qualitative impact of key process parameters on common defects. Obtaining precise quantitative data often requires extensive experimentation on specific toolsets and processes.

Table 1: Chemical-Mechanical Planarization (CMP) Parameter Effects

| Parameter              | Effect on Micro-scratches                    | Effect on Removal Rate             |

|------------------------|----------------------------------------------|------------------------------------|

| Downforce/Pressure     | Higher pressure can increase scratch density | Increases                          |

| Platen/Carrier Speed   | Higher speeds can increase scratch risk      | Increases                          |

| Slurry Flow Rate       | Insufficient flow can lead to scratching     | Can influence                      |

| Abrasive Particle Size | Larger particles increase scratch risk       | Larger particles can increase rate |

| Pad Hardness           | Harder pads can increase scratch risk        | Can influence                      |

Table 2: Plasma Etching Parameter Effects

| Parameter             | Effect on Undercut<br>(Anisotropy)         | Effect on Residue                  |

|-----------------------|--------------------------------------------|------------------------------------|

| RF Power              | Higher power can improve anisotropy        | Can help remove residues           |

| Chamber Pressure      | Lower pressure improves anisotropy         | Can affect residue formation       |

| Gas Flow Rates        | Affects sidewall passivation and etch rate | Can influence byproduct volatility |

| Substrate Temperature | Can influence etch rate and selectivity    | Can affect byproduct volatility    |

## **Experimental Protocols Detailed Protocol for Photolithography Optimization**

This protocol outlines a standard procedure for optimizing a photolithography process to achieve a target critical dimension (CD) with high uniformity.

- 1. Wafer Preparation: a. Start with a clean, dry **silicon** wafer. b. Perform a dehydration bake on a hotplate at 150°C for 30 minutes to remove any adsorbed moisture. c. Allow the wafer to cool to room temperature.

- 2. Adhesion Promotion: a. Apply Hexamethyldisilazane (HMDS) to the wafer surface. This can be done in a vapor prime oven or by spin-coating. b. If spin-coating, dispense a small amount of HMDS onto the center of the wafer and spin at 3000 rpm for 30 seconds.

- 3. Photoresist Coating: a. Dispense the photoresist onto the center of the wafer. b. Spin the wafer at a pre-determined speed (e.g., 4000 rpm for 45 seconds) to achieve the desired thickness. c. Perform a soft bake on a hotplate at the temperature and time specified by the photoresist manufacturer (e.g., 95°C for 60 seconds) to drive off solvents.

- 4. Exposure: a. Place the wafer in the lithography tool (e.g., a stepper or contact aligner). b. Align the photomask to the wafer. c. Expose the wafer with the appropriate wavelength of UV light. To optimize the dose, perform a dose matrix experiment by varying the exposure time or energy across different fields on the wafer.

- 5. Post-Exposure Bake (PEB): a. For chemically amplified resists, a PEB is required. Bake the wafer on a hotplate at the recommended temperature and time (e.g., 110°C for 60 seconds).

- 6. Development: a. Immerse the wafer in a developer solution (e.g., a TMAH-based developer) for the specified time (e.g., 60 seconds). b. Rinse the wafer thoroughly with deionized (DI) water. c. Dry the wafer using a nitrogen gun.

- 7. Inspection and Metrology: a. Inspect the patterned photoresist under an optical microscope for large defects. b. Use a scanning electron microscope (SEM) to measure the critical dimensions of the features in each field of the dose matrix. c. Analyze the CD data to determine the optimal exposure dose that provides the target CD with the largest process latitude.

## **General Protocol for Plasma Etching**

This protocol provides a general workflow for a plasma etching process.

- 1. Wafer Loading: a. Load the patterned wafer into the plasma etch chamber.

- 2. Chamber Pump-Down: a. Evacuate the chamber to the desired base pressure.

- 3. Gas Flow Stabilization: a. Introduce the process gases at the specified flow rates and allow the pressure to stabilize.

- 4. Plasma Ignition and Etching: a. Apply RF power to ignite the plasma and begin the etching process. b. The etching is typically timed or controlled by an endpoint detection system.

- 5. Plasma Extinguishing and Purge: a. Turn off the RF power to extinguish the plasma. b. Purge the chamber with an inert gas (e.g., Nitrogen) to remove residual process gases.

- 6. Wafer Unloading: a. Vent the chamber to atmospheric pressure and unload the wafer.

- 7. Post-Etch Processing: a. Perform a post-etch clean to remove any residues. b. Inspect the wafer for etch quality and measure the etched feature dimensions.

## General Protocol for Chemical-Mechanical Planarization (CMP)

This protocol outlines the basic steps for a CMP process.

- 1. Wafer Mounting: a. Mount the wafer onto a carrier head.

- 2. Slurry Dispensing: a. Dispense the CMP slurry onto the polishing pad.

- 3. Polishing: a. Bring the wafer carrier into contact with the rotating polishing pad. b. Apply the specified downforce and set the desired rotation speeds for the carrier and the platen. c. Polish for a predetermined amount of time or until an endpoint is detected.

- 4. Post-CMP Cleaning: a. Transfer the wafer to a post-CMP cleaning module. b. The cleaning process typically involves brush scrubbing with cleaning solutions and megasonic cleaning to remove slurry particles and chemical residues.

- 5. Wafer Drying: a. Dry the wafer using a spin-rinse-dry (SRD) or an IPA vapor dryer.

- 6. Inspection: a. Inspect the wafer for defects and measure the final film thickness and topography.

## **Visualizations**

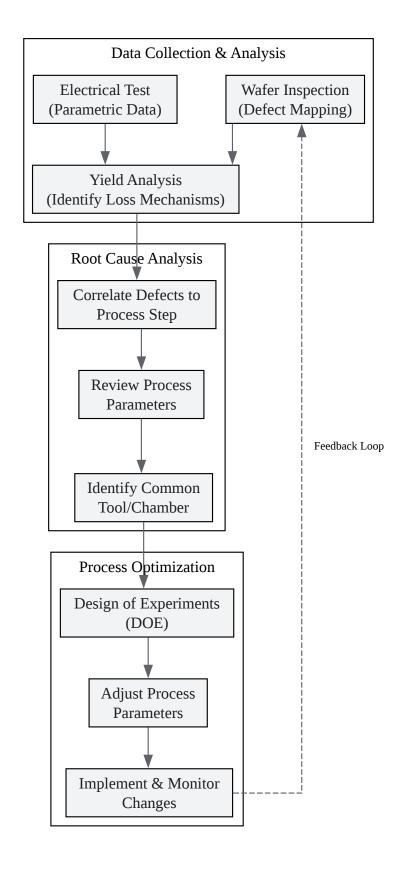

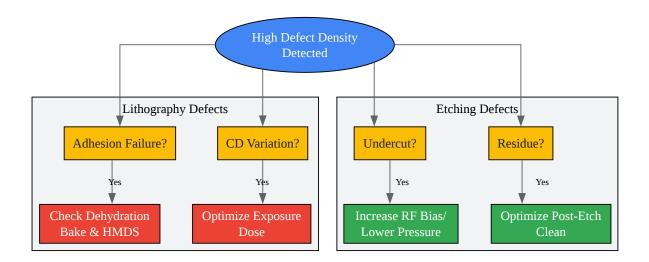

The following diagrams illustrate key relationships and workflows in **silicon** wafer manufacturing.

#### Click to download full resolution via product page

Caption: A logical workflow for systematic yield improvement in **silicon** wafer manufacturing.

#### Click to download full resolution via product page

Caption: A simplified troubleshooting decision tree for common wafer fabrication defects.

#### **Need Custom Synthesis?**

BenchChem offers custom synthesis for rare earth carbides and specific isotopiclabeling.

Email: info@benchchem.com or Request Quote Online.

### References

- 1. skyworksinc.com [skyworksinc.com]

- 2. researchgate.net [researchgate.net]

- 3. ijmerr.com [ijmerr.com]

- 4. universitywafer.com [universitywafer.com]

- 5. researchgate.net [researchgate.net]

- 6. jamt.utem.edu.my [jamt.utem.edu.my]

- 7. The Planarization Process for Semiconductor Manufacturing | Advanced PCB Design Blog

| Cadence [resources.pcb.cadence.com]

- 8. 5 Challenges in Thin Film Manufacturing and How to Overcome Them Denton Vacuum [dentonvacuum.com]

- 9. svc.org [svc.org]

- To cite this document: BenchChem. [Technical Support Center: Optimizing Silicon Wafer Manufacturing for Higher Yield]. BenchChem, [2025]. [Online PDF]. Available at: [https://www.benchchem.com/product/b1239273#optimizing-process-parameters-in-silicon-wafer-manufacturing-for-higher-yield]

#### **Disclaimer & Data Validity:**

The information provided in this document is for Research Use Only (RUO) and is strictly not intended for diagnostic or therapeutic procedures. While BenchChem strives to provide accurate protocols, we make no warranties, express or implied, regarding the fitness of this product for every specific experimental setup.

**Technical Support:** The protocols provided are for reference purposes. Unsure if this reagent suits your experiment? [Contact our Ph.D. Support Team for a compatibility check]

Need Industrial/Bulk Grade? Request Custom Synthesis Quote

## BenchChem

Our mission is to be the trusted global source of essential and advanced chemicals, empowering scientists and researchers to drive progress in science and industry. Contact

Address: 3281 E Guasti Rd

Ontario, CA 91761, United States

Phone: (601) 213-4426

Email: info@benchchem.com