# Technical Support Center: Optimizing SiC Epitaxial Growth

Author: BenchChem Technical Support Team. Date: December 2025

| Compound of Interest |                 |           |

|----------------------|-----------------|-----------|

| Compound Name:       | Silicon carbide |           |

| Cat. No.:            | B1214593        | Get Quote |

This guide provides researchers, scientists, and development professionals with detailed troubleshooting information and frequently asked questions (FAQs) to address common challenges encountered during the **Silicon Carbide** (SiC) epitaxial growth process.

# Frequently Asked Questions (FAQs) Q1: What are the most common types of defects in 4H-SiC epitaxial layers and their primary causes?

The quality of SiC epitaxial layers is primarily challenged by the presence of various defects that can degrade device performance and reliability.[1][2] These defects are broadly categorized into crystallographic (or structural) defects and surface morphology defects.[1][3]

- Crystallographic Defects: These defects originate mainly from the SiC substrate and propagate into the epitaxial layer.[3] They include:

- Dislocations: Threading Screw Dislocations (TSDs), Threading Edge Dislocations (TEDs), and Basal Plane Dislocations (BPDs). BPDs are particularly detrimental as they can lead to the formation of stacking faults that degrade bipolar device performance.[4][5]

- Stacking Faults (SFs): These are disruptions in the stacking sequence of atomic planes.

They can be inherited from the substrate or form during growth from the transformation of other defects like BPDs.[3][6]

- Micropipes: Hollow tube defects that extend through the crystal.

- Surface Morphology Defects: These are macroscopic defects often visible with an optical microscope. Their formation is typically linked to substrate imperfections, contaminants, or non-optimal growth process parameters.[3][7] Key examples include:

- Triangular Defects: Often 3C-SiC polytype inclusions that form due to particles on the surface or instabilities in the step-flow growth, such as 2D nucleation on terraces.[3][8]

- Carrot Defects: Elongated defects that can increase reverse leakage current in diodes.[8]

- Step-Bunching: The formation of large terraces (macro-steps) instead of a uniform stepflow, which can roughen the surface and affect device performance.[3][8]

- Pits, Downfall, and Particles: Surface imperfections caused by issues like incomplete removal of polishing damage, contaminants in the reactor, or gas phase nucleation.[3][8]

The origins of these defects are complex and often interrelated, stemming from substrate quality, growth temperature, reactor chamber design, and process chemistry.[2][9]

# Q2: How does the Carbon-to-Silicon (C/Si) ratio critically influence the quality of the grown epilayer?

The C/Si ratio is one of the most critical parameters in the Chemical Vapor Deposition (CVD) process for SiC epitaxy, as it directly influences surface morphology, defect density, and even doping efficiency.[2][10] The primary effect is on the surface chemistry and adatom mobility, which dictates the growth mode.

- Under C-rich conditions (higher C/Si ratio): The surface can become rough due to enhanced 2D nucleation on the terraces, which disrupts the ideal step-flow growth mode and can lead to the formation of triangular defects.[8]

- Under Si-rich conditions (lower C/Si ratio): Step-bunching can be reduced, leading to smoother surfaces.[10] However, excessively Si-rich conditions can lead to the formation of silicon droplets on the surface.[11]

Finding the optimal C/Si ratio is crucial for minimizing defect density and achieving a smooth surface. Systematic experiments have shown that an optimal ratio exists where defect density is minimized.[2]

Table 1: Effect of C/Si Ratio on Defect Density and Surface Roughness

| C/Si Ratio | Defect Density (Median,<br>cm <sup>-2</sup> ) | Surface Roughness (Ra,<br>nm) |

|------------|-----------------------------------------------|-------------------------------|

| 0.52       | ~4.5                                          | ~0.22                         |

| 0.72       | ~1.5                                          | ~0.15                         |

| 0.80       | ~2.5                                          | ~0.18                         |

| 1.00       | ~3.8                                          | ~0.21                         |

Data synthesized from experimental findings reported in reference[2]. The optimal C/Si ratio was found to be approximately 0.72 in this specific study.

# **Troubleshooting Guides**

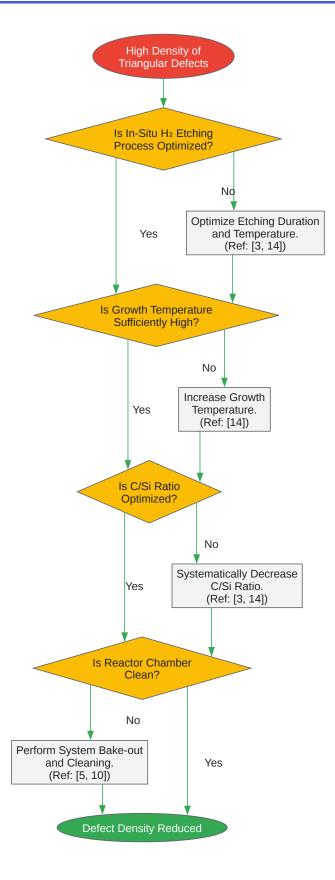

# Issue 1: High Density of Triangular Defects Observed on the Epilayer

Question: My 4H-SiC epilayer shows a high density of triangular defects. What are the potential causes and how can I solve this?

Answer: Triangular defects are one of the most destructive surface defects and are often associated with 3C-SiC polytype inclusions.[1][6] Their formation is generally attributed to a disruption of the step-flow growth mode.[8] The troubleshooting process should investigate substrate preparation, growth parameters, and potential contamination.

#### **Troubleshooting Steps:**

- Evaluate Substrate and Pre-Growth Etching:

- Cause: Subsurface damage from polishing or foreign particles on the substrate can act as nucleation sites for these defects.[3]

## Troubleshooting & Optimization

- Solution: Optimize the in-situ H<sub>2</sub> etching process before growth. A proper etch removes surface damage and creates a uniform step structure, which is critical for stable step-flow growth.[8] Be cautious, as excessive etching can expose substrate defects.[2]

- Optimize Growth Temperature:

- Cause: Low growth temperatures reduce the surface migration rate of adatoms, increasing the likelihood of 2D nucleation on terraces, which leads to triangular defects.[8]

- Solution: Increase the growth temperature. Higher temperatures enhance adatom mobility, promoting step-flow growth and suppressing 2D nucleation.[8]

- Adjust C/Si Ratio:

- Cause: A high C/Si ratio can also promote 2D nucleation.[8]

- Solution: Systematically lower the C/Si ratio. This enhances Si surface coverage and can stabilize the step-flow growth front. An optimal C/Si ratio around 0.72 has been shown to minimize defect density.[2]

- Check for System Contamination:

- Cause: Particles falling from the reactor ceiling or walls ("downfall") can land on the wafer surface and nucleate triangular defects.[3][6]

- Solution: Ensure proper cleaning and handling of the susceptor and reactor chamber before the growth run.[4]

Click to download full resolution via product page

Caption: Troubleshooting Flowchart for Triangular Defects.

### Issue 2: Severe Step-Bunching on the Epilayer Surface

Question: My epilayer surface is very rough due to step-bunching. What causes this and how can it be minimized?

Answer: Step-bunching is a surface morphology defect where atomic steps coalesce to form larger "macro-steps," leading to a rough surface.[3][8] This phenomenon is often attributed to differences in growth rates along different crystallographic orientations on the surface.[8] The key to minimizing step-bunching is to carefully control the surface chemistry and growth kinetics.

#### **Troubleshooting Steps:**

- Control Growth Temperature:

- Cause: The kinetics of step-bunching are highly temperature-dependent. High temperatures can sometimes exacerbate the issue.[8]

- Solution: Carefully control and potentially lower the growth temperature. The goal is to find a temperature where the growth rates in different directions are more balanced, thus preventing the formation of macro-steps.[8]

- Optimize C/Si Ratio:

- Cause: The C/Si ratio directly affects the surface energy and adatom diffusion, which are key factors in step dynamics.

- Solution: Experiment with the C/Si ratio. Lowering the C/Si ratio has been shown to reduce step-bunching on both 4° and 8° off-cut substrates.[10]

- Verify Substrate Off-Cut Angle:

- Cause: While step-flow growth relies on an off-axis substrate, the specific angle and its uniformity can influence step dynamics.

- Solution: Ensure you are using a high-quality substrate with a consistent and appropriate off-cut angle. While this is not a process parameter you can change during a run, it is a critical initial condition.

- · Consider Post-Growth Polishing:

- Solution: If step-bunching is unavoidable due to other process constraints (e.g., for certain device structures), Chemical Mechanical Polishing (CMP) can be used after growth to replanarize the surface and achieve a low roughness.[12]

### **Issue 3: Poor Doping and Thickness Uniformity**

Question: I am observing significant variations in doping concentration and epilayer thickness across my 150 mm wafer. What are the likely causes and solutions?

Answer: Achieving uniform doping and thickness, especially on large-diameter wafers, is a significant challenge related to the complex interplay of gas flow dynamics and temperature distribution within the CVD reactor.[11]

#### **Troubleshooting Steps:**

- Analyze Temperature Distribution:

- Cause: Non-uniform temperature across the wafer is a primary cause of variations. The

growth rate and doping incorporation efficiency are both highly sensitive to temperature.

[11]

- Solution: Profile the temperature across your susceptor. Adjust heating element power or reactor design to achieve a more uniform temperature profile. As shown in Table 2, even a slight change in temperature can significantly alter both thickness and doping concentration.[11]

- Optimize Gas Flow Dynamics:

- Cause: The flow of precursor and carrier gases can create depletion zones or areas of higher concentration, leading to non-uniformity. The hydrogen (H<sub>2</sub>) carrier gas flow is a major factor.[11]

- Solution: Adjust the H<sub>2</sub> carrier gas flow ratio between the central and side injectors (if your system allows). This can alter the distribution of Si and C source species across the wafer,

improving uniformity. An optimal H<sub>2</sub> flow ratio can yield thickness uniformity better than 1%.[11]

- Adjust Wafer Rotation Speed:

- Cause: Insufficient or improper wafer rotation speed can fail to average out asymmetries in temperature and gas flow.

- Solution: Ensure the wafer holder is rotating at a stable and sufficient speed (e.g., ~50 rpm) to mitigate stationary non-uniformities in the reactor environment.[11]

Table 2: Influence of Growth Temperature on Epilayer Thickness and Doping

| Growth Temperature (°C) | Epilayer<br>Thickness<br>(µm) | Thickness<br>Uniformity (%) | N₂ Doping<br>Concentration<br>(x10¹⁵ cm⁻³) | Doping<br>Uniformity (%) |

|-------------------------|-------------------------------|-----------------------------|--------------------------------------------|--------------------------|

| 1610                    | 15.10                         | 2.51                        | 2.15                                       | 10.21                    |

| 1630                    | 14.85                         | 1.95                        | 2.80                                       | 8.55                     |

| 1660                    | 14.51                         | 2.88                        | 3.95                                       | 11.34                    |

| 1680                    | 14.16                         | 4.01                        | 5.20                                       | 13.98                    |

Data synthesized from experiments on 150 mm wafers reported in reference[11]. Note the trade-offs: while doping efficiency increases with temperature, the growth rate slightly decreases and uniformity can be affected.

# **Experimental Protocols**

# **Protocol 1: Optimization of In-Situ Hydrogen Etching**

This protocol outlines a systematic approach to determine the optimal in-situ hydrogen (H<sub>2</sub>) etching conditions to prepare the substrate surface for high-quality epitaxial growth.

Objective: To remove subsurface polishing damage and achieve a regular atomic step structure without excessively exposing substrate defects.

#### Methodology:

- Substrate Preparation: Use a set of identical 4H-SiC substrates for the experimental series.

- Establish Baseline: Perform a standard epitaxial growth run with a minimal or no H<sub>2</sub> etch to serve as a baseline for defect density.

- Vary Etching Duration:

- Fix the etching temperature (e.g., 1600 °C) and H<sub>2</sub> flow rate (e.g., 100 slm).[2][13]

- Create a series of experiments where only the etching duration is varied. For example: 2 min, 4 min, 6 min, 8 min, and 10 min.[2]

- After etching, grow a standard, thin epilayer on each substrate under identical conditions.

#### Characterization:

- Use an optical microscope (with Nomarski interference contrast) to map and count the density of major surface defects (e.g., triangular defects, pits).

- Use Atomic Force Microscopy (AFM) to analyze the surface morphology, step structure, and root mean square (RMS) roughness.[14]

#### Data Analysis:

- Plot the defect density as a function of etching time.

- Identify the duration that results in the lowest defect density while maintaining a smooth surface morphology. Studies have shown that an optimal window exists (e.g., 2-6 minutes), after which defect density may increase again due to the unmasking of substrate defects.[2]

- (Optional) Vary Etching Temperature: Repeat the most promising durations at slightly different temperatures (e.g., 1580 °C, 1620 °C) to further refine the process.[13]

#### Table 3: Example Data for H<sub>2</sub> Etching Optimization

| H₂ Etching Duration (min) | Resulting Defect Density (Relative Units) |

|---------------------------|-------------------------------------------|

| 0 (No Etch)               | High                                      |

| 2                         | Low                                       |

| 4                         | Lowest                                    |

| 6                         | Low                                       |

| 8                         | Increasing                                |

| 10                        | High                                      |

Illustrative data based on trends described in reference[2].

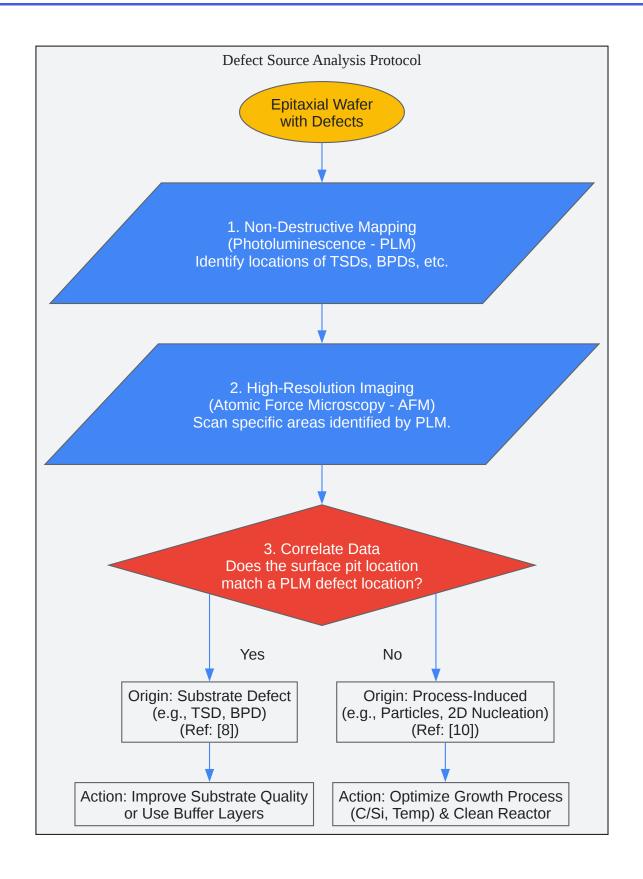

# **Protocol 2: Defect Source Analysis Workflow**

This protocol describes a workflow to identify the origin of epilayer defects by correlating surface features with underlying crystallographic defects.

Objective: To determine whether surface defects (e.g., growth pits) originate from substrate dislocations or from process-induced issues.

#### Methodology:

- Initial Non-Destructive Mapping:

- Use Photoluminescence Mapping (PLM) on the full wafer (post-epigrowth) to nondestructively map the locations of crystallographic defects like screw dislocations, grain boundaries, and stressed regions.[14]

- High-Resolution Surface Imaging:

- Based on the PLM map, select specific areas of interest that contain identified crystallographic defects.

- Use an Atomic Force Microscope (AFM) to perform high-resolution scans of these exact areas.[14]

# Troubleshooting & Optimization

#### · Correlation and Analysis:

- Correlate the surface morphology from the AFM images with the defect map from the PLM.

- Determine which types of surface growth pits are associated with specific crystallographic defects (e.g., pits with nano-cores are often linked to screw dislocations).[14]

- Identify surface defects that do not correlate with any underlying crystallographic defect;

these are likely process-induced (e.g., from downfall particles or surface contamination).

#### Feedback to Process:

- If defects are primarily linked to substrate dislocations, focus on improving substrate quality or implementing buffer layers to block defect propagation.

- If defects are process-induced, focus on optimizing growth parameters (C/Si, temp) and reactor cleanliness.

Click to download full resolution via product page

#### **Need Custom Synthesis?**

BenchChem offers custom synthesis for rare earth carbides and specific isotopiclabeling.

Email: info@benchchem.com or Request Quote Online.

### References

- 1. mdpi.com [mdpi.com]

- 2. Influence of Growth Process on Suppression of Surface Morphological Defects in 4H-SiC Homoepitaxial Layers - PMC [pmc.ncbi.nlm.nih.gov]

- 3. What are the defects of silicon carbide epitaxial layer [vet-china.com]

- 4. diva-portal.org [diva-portal.org]

- 5. bpb-us-w2.wpmucdn.com [bpb-us-w2.wpmucdn.com]

- 6. Defect Inspection Techniques in SiC PMC [pmc.ncbi.nlm.nih.gov]

- 7. researchgate.net [researchgate.net]

- 8. pubs.aip.org [pubs.aip.org]

- 9. diva-portal.org [diva-portal.org]

- 10. researchgate.net [researchgate.net]

- 11. mdpi.com [mdpi.com]

- 12. Morphology Improvement of Step Bunching on 4H-SiC Wafers by Polishing Technique | Scientific.Net [scientific.net]

- 13. researchgate.net [researchgate.net]

- 14. maxmiletech.com [maxmiletech.com]

- To cite this document: BenchChem. [Technical Support Center: Optimizing SiC Epitaxial Growth]. BenchChem, [2025]. [Online PDF]. Available at: [https://www.benchchem.com/product/b1214593#optimizing-sic-epitaxial-growth-for-high-quality-devices]

#### **Disclaimer & Data Validity:**

The information provided in this document is for Research Use Only (RUO) and is strictly not intended for diagnostic or therapeutic procedures. While BenchChem strives to provide

accurate protocols, we make no warranties, express or implied, regarding the fitness of this product for every specific experimental setup.

**Technical Support:** The protocols provided are for reference purposes. Unsure if this reagent suits your experiment? [Contact our Ph.D. Support Team for a compatibility check]

Need Industrial/Bulk Grade? Request Custom Synthesis Quote

# BenchChem

Our mission is to be the trusted global source of essential and advanced chemicals, empowering scientists and researchers to drive progress in science and industry. Contact

Address: 3281 E Guasti Rd

Ontario, CA 91761, United States

Phone: (601) 213-4426

Email: info@benchchem.com