# Technical Support Center: Optimizing ITIC-M Device Performance Through Thermal Annealing

Author: BenchChem Technical Support Team. Date: December 2025

This technical support center provides troubleshooting guidance and frequently asked questions (FAQs) for researchers, scientists, and drug development professionals working with ITIC-M based organic solar cell devices. The following sections detail the critical role of thermal annealing time in optimizing device performance.

# Troubleshooting Guide: Annealing Time for ITIC-M Devices

Proper thermal annealing is a critical step in achieving high-performance organic solar cells by optimizing the morphology of the bulk-heterojunction (BHJ) active layer. This guide addresses common issues encountered during the thermal annealing of **ITIC-M** based devices.

| Issue ID | Problem                                     | Possible Cause(s)                                                                                                                                                                                                                                                                        | Suggested<br>Solution(s)                                                                                                                                                                                                       |

|----------|---------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| AT-01    | Low Power<br>Conversion Efficiency<br>(PCE) | - Sub-optimal annealing time (either too short or too long) Incomplete phase separation of the donor-acceptor blend Poor crystallinity of the active layer components.                                                                                                                   | - Systematically vary the annealing time at a fixed, optimized temperature (e.g., 100-110°C) to find the optimal duration. Start with a range of 2 to 15 minutes Refer to the data in Table 1 for expected performance trends. |

| AT-02    | Low Short-Circuit<br>Current (Jsc)          | - Insufficient annealing time leading to a poorly ordered active layer morphology, which hinders exciton dissociation and charge transport.                                                                                                                                              | - Increase the annealing time incrementally (e.g., in 2-3 minute steps) to promote better phase separation and improve charge carrier pathways.                                                                                |

| AT-03    | Low Fill Factor (FF)                        | - Short Annealing Time: Incomplete removal of residual solvent and inadequate phase separation can lead to high series resistance Excessive Annealing Time: Over- annealing can cause excessive phase separation, leading to the formation of large, pure domains which increases charge | - For low FF with short annealing, extend the duration to improve the morphology If FF decreases after prolonged annealing, reduce the annealing time to prevent excessive domain growth.                                      |

|       |                                   | recombination and series resistance.[1]                                                                                                                                                                                                                    |                                                                                                                                                                                                                   |

|-------|-----------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| AT-04 | Low Open-Circuit<br>Voltage (Voc) | - While Voc is generally less sensitive to annealing time compared to Jsc and FF, significant deviations can indicate issues with the donor-acceptor interface or energy level alignment.  Excessive annealing might lead to degradation of the materials. | - Ensure the annealing temperature is not too high Optimize the annealing time to achieve a well-defined interface without causing thermal degradation.                                                           |

| AT-05 | Poor Device<br>Reproducibility    | - Inconsistent annealing time and temperature across different batches Variations in the thermal ramp-up and cool-down rates.                                                                                                                              | - Use a calibrated hotplate with precise temperature control Standardize the annealing duration and the procedure for placing and removing the devices from the heat source to ensure consistent thermal history. |

### **Frequently Asked Questions (FAQs)**

Q1: What is the primary purpose of thermal annealing the ITIC-M active layer?

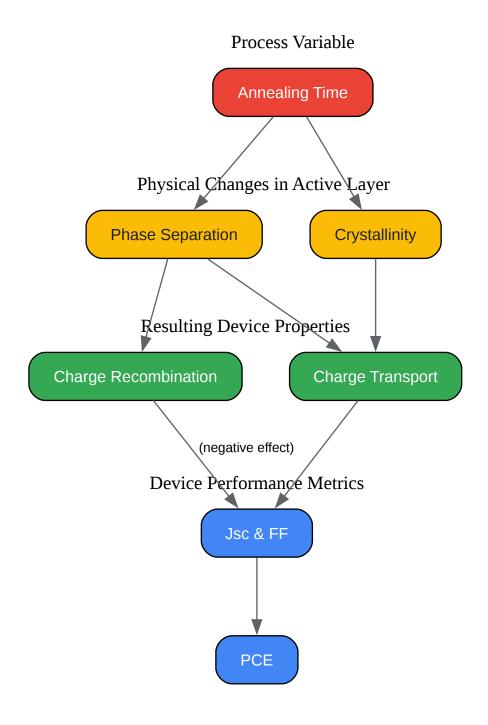

A1: Thermal annealing provides the necessary energy to promote the self-organization of the donor (e.g., PBDB-T) and acceptor (**ITIC-M**) molecules within the active layer. This process optimizes the nanoscale phase separation, improves the crystallinity of the components, and

facilitates the formation of efficient pathways for charge transport, ultimately leading to higher device performance.[1]

Q2: How does annealing time affect the key device performance parameters?

A2: Annealing time has a significant impact on the Power Conversion Efficiency (PCE), Short-Circuit Current (Jsc), and Fill Factor (FF). As shown in the table below, an optimal annealing time leads to a peak in performance. Insufficient annealing results in a poorly organized morphology, while excessive annealing can lead to overly large domains, which increases charge recombination. The Open-Circuit Voltage (Voc) is typically less affected but can decrease with very long annealing times due to potential material degradation.

Q3: What is a typical starting point for optimizing the annealing time for a PBDB-T:**ITIC-M** device?

A3: A common and effective starting point for thermal annealing of PBDB-T:**ITIC-M** active layers is 100°C for 10 minutes.[2] However, the optimal time can vary depending on the specific experimental setup and substrate. It is recommended to perform a time-dependent study around this initial condition (e.g., 5, 8, 10, 12, 15 minutes) to determine the ideal duration for your specific process.

Q4: Can I compensate for a non-optimal annealing temperature by changing the annealing time?

A4: While there is an interplay between annealing temperature and time, they are not directly interchangeable. The annealing temperature is crucial for enabling molecular motion, and the annealing time allows for the morphological arrangement to reach an optimal state. It is best practice to first determine the optimal annealing temperature and then perform a systematic study of the annealing time at that fixed temperature.

#### **Data Presentation**

The following table summarizes the typical effect of varying annealing time on the performance of a PBDB-T:**ITIC-M** based organic solar cell, annealed at an optimized temperature of 100°C. The data is a representative compilation based on literature findings.

Table 1: Effect of Annealing Time on PBDB-T:ITIC-M Device Performance

| Annealing<br>Time (minutes) | PCE (%) | Jsc (mA/cm²) | Voc (V) | FF (%) |

|-----------------------------|---------|--------------|---------|--------|

| 0 (As-cast)                 | 7.5     | 13.5         | 0.92    | 60.5   |

| 2                           | 8.8     | 14.8         | 0.92    | 64.5   |

| 5                           | 10.2    | 16.0         | 0.92    | 69.5   |

| 10                          | 11.0    | 16.9         | 0.92    | 71.0   |

| 15                          | 10.5    | 16.5         | 0.91    | 70.0   |

| 30                          | 9.2     | 15.5         | 0.90    | 66.0   |

## **Experimental Protocols**

Device Fabrication of PBDB-T:ITIC-M Solar Cells

- Substrate Cleaning: Indium tin oxide (ITO) coated glass substrates are sequentially cleaned

in an ultrasonic bath with detergent, deionized water, acetone, and isopropanol for 15

minutes each. The substrates are then dried with nitrogen gas and treated with UV-ozone for

20 minutes.

- Hole Transport Layer (HTL) Deposition: A solution of PEDOT:PSS is spin-coated onto the cleaned ITO substrates and subsequently annealed at 150°C for 15 minutes in air.

- Active Layer Deposition: A blend solution of PBDB-T and ITIC-M (typically in a 1:1 weight ratio) in chlorobenzene with a small percentage of a processing additive like 1,8diiodooctane (DIO) is spin-coated onto the HTL in a nitrogen-filled glovebox.

- Thermal Annealing: The substrates with the active layer are then annealed on a calibrated hotplate inside the glovebox at a set temperature (e.g., 100°C) for a specified duration (e.g., 0, 2, 5, 10, 15, or 30 minutes).

- Electron Transport Layer (ETL) and Electrode Deposition: Finally, an electron transport layer (e.g., PFN-Br) and a top metal electrode (e.g., Aluminum) are deposited via spin-coating and thermal evaporation, respectively, to complete the device structure.

#### **Device Characterization**

The current density-voltage (J-V) characteristics of the fabricated devices are measured under simulated AM 1.5G solar illumination at 100 mW/cm². From these measurements, the key photovoltaic parameters (PCE, Jsc, Voc, and FF) are extracted.

## **Mandatory Visualization**

Click to download full resolution via product page

#### **Need Custom Synthesis?**

BenchChem offers custom synthesis for rare earth carbides and specific isotopiclabeling.

Email: info@benchchem.com or Request Quote Online.

### References

- 1. researchgate.net [researchgate.net]

- 2. Frontiers | Constructing Desired Vertical Component Distribution Within a PBDB-T:ITIC-M

Photoactive Layer via Fine-Tuning the Surface Free Energy of a Titanium Chelate Cathode

Buffer Layer [frontiersin.org]

- To cite this document: BenchChem. [Technical Support Center: Optimizing ITIC-M Device Performance Through Thermal Annealing]. BenchChem, [2025]. [Online PDF]. Available at: [https://www.benchchem.com/product/b12090545#effect-of-annealing-time-on-itic-m-device-performance]

#### **Disclaimer & Data Validity:**

The information provided in this document is for Research Use Only (RUO) and is strictly not intended for diagnostic or therapeutic procedures. While BenchChem strives to provide accurate protocols, we make no warranties, express or implied, regarding the fitness of this product for every specific experimental setup.

**Technical Support:**The protocols provided are for reference purposes. Unsure if this reagent suits your experiment? [Contact our Ph.D. Support Team for a compatibility check]

Need Industrial/Bulk Grade? Request Custom Synthesis Quote

## BenchChem

Our mission is to be the trusted global source of essential and advanced chemicals, empowering scientists and researchers to drive progress in science and industry. Contact

Address: 3281 E Guasti Rd

Ontario, CA 91761, United States

Phone: (601) 213-4426

Email: info@benchchem.com