Check Availability & Pricing

# Technical Support Center: Optimizing Contact Resistance in In<sub>2</sub>Se<sub>3</sub> Transistors

Author: BenchChem Technical Support Team. Date: December 2025

| Compound of Interest |                      |           |

|----------------------|----------------------|-----------|

| Compound Name:       | Indium(III) selenide |           |

| Cat. No.:            | B1233659             | Get Quote |

This technical support center provides researchers, scientists, and drug development professionals with a comprehensive guide to troubleshooting and improving contact resistance in Indium Selenide (In<sub>2</sub>Se<sub>3</sub>) transistors. The following sections offer detailed experimental protocols, frequently asked questions (FAQs), and troubleshooting guidance in a user-friendly question-and-answer format.

### **Troubleshooting Guide**

High contact resistance is a prevalent issue in the fabrication of 2D material-based transistors, leading to diminished device performance. This guide addresses common problems encountered during experiments with In<sub>2</sub>Se<sub>3</sub> transistors.

Q1: My measured contact resistance is excessively high. What are the potential causes and how can I address them?

A1: High contact resistance in In<sub>2</sub>Se<sub>3</sub> transistors can stem from several factors throughout the fabrication and measurement process. Here's a breakdown of potential causes and their solutions:

- Poor Metal-Semiconductor Interface:

- Cause: Contaminants or a native oxide layer on the In<sub>2</sub>Se<sub>3</sub> surface can inhibit the formation of a clean interface with the contact metal.

Solution: Implement a thorough surface cleaning and passivation protocol before metal deposition. This may include solvent cleaning (e.g., acetone, isopropanol) followed by a gentle plasma treatment (e.g., low-power Argon or Oxygen plasma) to remove organic residues and the native oxide layer.

### Inappropriate Contact Metal:

- Cause: A large Schottky barrier height (SBH) between the metal and In₂Se₃ can impede carrier injection.

- Solution: Select a metal with a work function that aligns well with the conduction or valence band of In<sub>2</sub>Se<sub>3</sub> to minimize the SBH. For n-type In<sub>2</sub>Se<sub>3</sub>, metals with lower work functions are generally preferred. Indium (In) has been shown to form good ohmic contacts with InSe.

#### Suboptimal Deposition and Annealing:

- Cause: Improper metal deposition conditions or inadequate post-deposition annealing can result in poor adhesion, and a disordered interface.

- Solution: Optimize the metal deposition process (e.g., thermal evaporation, e-beam evaporation) to ensure good adhesion without damaging the In<sub>2</sub>Se<sub>3</sub> lattice. Perform postmetallization annealing to promote the formation of a stable, low-resistance interface.

#### Measurement Errors:

- Cause: Issues with the measurement setup, such as probe placement or incorrect analysis of the Transmission Line Method (TLM) data, can lead to inaccurate contact resistance values.

- Solution: Ensure proper probe contact with the metal pads during TLM measurements and carefully analyze the linearity of the resistance versus channel length plot. Non-linearity can indicate issues with the contacts or the semiconductor channel itself.

Q2: I observe significant device-to-device variation in contact resistance. What could be the reason?

### Troubleshooting & Optimization

A2: Device-to-device variation is often a result of inconsistencies in the fabrication process. Key factors include:

- Non-uniformity of the In<sub>2</sub>Se<sub>3</sub> Flake: Variations in the thickness and quality of the exfoliated In<sub>2</sub>Se<sub>3</sub> flakes can lead to different contact properties.

- Inconsistent Surface Preparation: If the surface cleaning process is not uniform across the substrate, some devices will have cleaner interfaces than others.

- Lithography and Etching Residues: Inconsistent removal of photoresist or other residues from the contact areas can lead to variable contact quality.

- Metal Deposition Inhomogeneity: Shadowing effects or non-uniform flux during metal deposition can result in variations in the contact thickness and quality.

To mitigate this, focus on:

- Careful selection of uniform In<sub>2</sub>Se<sub>3</sub> flakes.

- Standardizing and optimizing the cleaning and lithography processes for consistency.

- Ensuring uniform metal deposition across the entire substrate.

Q3: My contacts appear to be non-ohmic. How can I improve the linearity of the I-V curves?

A3: Non-ohmic (Schottky) contacts are characterized by non-linear current-voltage (I-V) curves, which is undesirable for transistor source and drain contacts. To achieve more ohmic behavior:

- Choose a suitable contact metal: As mentioned, selecting a metal with a work function that minimizes the Schottky barrier is crucial.[1][2]

- Doping the contact region: Introducing dopants under the contact metal can thin the Schottky barrier, allowing for easier carrier tunneling and promoting ohmic behavior.

- Post-deposition annealing: Annealing can facilitate interdiffusion at the metal-semiconductor interface, sometimes forming an alloyed region with a lower barrier height.[3]

# Frequently Asked Questions (FAQs)

Q1: What are the best contact metals for n-type In<sub>2</sub>Se<sub>3</sub> transistors?

A1: The choice of contact metal is critical for achieving low contact resistance. For n-type In<sub>2</sub>Se<sub>3</sub>, metals with low work functions are generally preferred to facilitate electron injection. Indium (In) has been demonstrated to form excellent ohmic contacts with InSe. Other metals like Titanium (Ti) and Chromium (Cr) followed by a capping layer of Gold (Au) are also commonly used. However, experimental optimization is necessary to determine the best metal for a specific fabrication process.

Q2: What is the recommended annealing temperature and duration for In<sub>2</sub>Se<sub>3</sub> transistors?

A2: The optimal annealing conditions depend on the specific contact metals and the substrate. A common starting point for annealing In<sub>2</sub>Se<sub>3</sub> transistors with metal contacts is in the range of 200-300°C for 30-60 minutes in an inert atmosphere (e.g., Nitrogen or Argon) or high vacuum. [4][5] It is crucial to perform a systematic study by varying the temperature and duration to find the optimal conditions for your specific devices, as excessive temperatures can damage the In<sub>2</sub>Se<sub>3</sub> crystal lattice.

Q3: How does surface treatment before metal deposition affect contact resistance?

A3: Surface treatment is a critical step to ensure a clean and pristine interface between the In<sub>2</sub>Se<sub>3</sub> and the contact metal. Common surface treatments include:

- Solvent Cleaning: Rinsing with acetone and isopropanol to remove organic residues.

- Plasma Treatment: A brief, low-power Argon (Ar) or Oxygen (O<sub>2</sub>) plasma treatment can effectively remove organic contaminants and the native oxide layer without causing significant damage to the In<sub>2</sub>Se<sub>3</sub> surface.[6][7][8] Ar plasma is generally used for physical sputtering of contaminants, while O<sub>2</sub> plasma is effective for removing organic residues through chemical reaction.

Q4: How do I accurately measure the contact resistance of my In<sub>2</sub>Se<sub>3</sub> transistors?

A4: The most common and reliable method for measuring contact resistance in 2D material transistors is the Transmission Line Method (TLM). This involves fabricating a series of

transistors with identical contact pad geometries but varying channel lengths. By plotting the total resistance between contacts against the channel length, the contact resistance can be extracted from the y-intercept of the linear fit. It's important to ensure that the I-V characteristics are linear in the measurement range, indicating ohmic behavior.[9][10]

# **Quantitative Data Summary**

The following table summarizes key performance parameters for In<sub>2</sub>Se<sub>3</sub> transistors with different contact metals, based on available literature. Note that direct contact resistance values for In<sub>2</sub>Se<sub>3</sub> are not always available, and performance metrics like mobility can be indicative of contact quality.

| Contact<br>Metal | In₂Se₃<br>Thicknes<br>s        | Mobility<br>(cm²/Vs) | On/Off<br>Ratio | Contact<br>Resistanc<br>e (Ω·μm) | Schottky<br>Barrier<br>Height<br>(eV) | Referenc<br>e |

|------------------|--------------------------------|----------------------|-----------------|----------------------------------|---------------------------------------|---------------|

| In/Au            | Monolayer<br>MoS <sub>2</sub>  | ~170                 | -               | Low<br>(ohmic)                   | -                                     | [11]          |

| In               | Multilayer<br>InSe             | -                    | -               | -                                | ~0.04                                 | [12]          |

| Ti/Au            | Multilayer<br>InSe             | -                    | -               | -                                | -                                     | -             |

| Cr/Au            | Multilayer<br>WSe <sub>2</sub> | -                    | -               | <200 k                           | Lower with thicker Cr                 | [13]          |

| Au               | Monolayer<br>In₂Se₃            | -                    | -               | -                                | -                                     | [14]          |

Note: Data for different 2D materials are included for reference due to the limited direct comparative data for In<sub>2</sub>Se<sub>3</sub>. The performance can vary significantly based on the entire fabrication process.

# **Experimental Protocols**

1. Protocol for In<sub>2</sub>Se<sub>3</sub> Surface Preparation Prior to Metal Deposition

### Troubleshooting & Optimization

This protocol outlines the steps for cleaning the In₂Se₃ surface to achieve a low-resistance contact interface.

- Solvent Cleaning:

- Immerse the substrate with exfoliated In₂Se₃ flakes in acetone for 5 minutes.

- Transfer the substrate to isopropanol and sonicate for 2 minutes.

- Dry the substrate with a gentle stream of nitrogen gas.

- Plasma Treatment (Optional but Recommended):

- Place the substrate in a plasma cleaner.

- Perform a low-power (e.g., 20-30 W) Argon (Ar) plasma treatment for 30-60 seconds to physically remove any remaining contaminants and the native oxide layer.[15][16][17]

- Alternatively, a low-power Oxygen (O<sub>2</sub>) plasma treatment can be used for a similar duration to remove organic residues.[7][12][18]

- Immediately transfer the substrate to the metal deposition system to minimize re-exposure to ambient conditions.

- 2. Protocol for Post-Metallization Annealing of In<sub>2</sub>Se<sub>3</sub> Transistors

This protocol describes a general procedure for annealing In₂Se₃ devices to improve contact resistance.

- Setup:

- Place the fabricated In<sub>2</sub>Se<sub>3</sub> transistors in a tube furnace or a rapid thermal annealing (RTA) system.

- Atmosphere Control:

- Purge the furnace with an inert gas (e.g., high-purity Nitrogen or Argon) for at least 30 minutes to create an oxygen-free environment.

### Annealing Process:

- Ramp up the temperature to the desired setpoint (e.g., 250°C) at a controlled rate (e.g., 10°C/minute).

- Hold the temperature at the setpoint for the desired duration (e.g., 30 minutes).

- After annealing, allow the furnace to cool down naturally to room temperature while maintaining the inert gas flow.

#### Characterization:

Once at room temperature, remove the devices and perform electrical characterization to evaluate the impact of annealing on contact resistance and device performance.

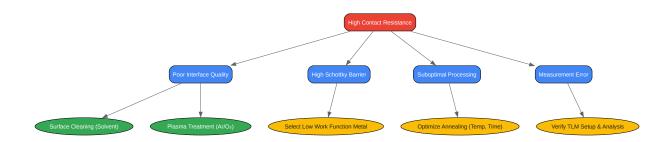

### **Visualizations**

Below are diagrams illustrating key experimental workflows and logical relationships in improving contact resistance in In<sub>2</sub>Se<sub>3</sub> transistors.

Click to download full resolution via product page

Caption: Experimental workflow for fabricating In<sub>2</sub>Se<sub>3</sub> transistors.

### Click to download full resolution via product page

Caption: Troubleshooting logic for high contact resistance.

### **Need Custom Synthesis?**

BenchChem offers custom synthesis for rare earth carbides and specific isotopiclabeling.

Email: info@benchchem.com or Request Quote Online.

## References

- 1. researchgate.net [researchgate.net]

- 2. ece.nus.edu.sg [ece.nus.edu.sg]

- 3. Metal-Semiconductor Ohmic and Schottky Contacts [cleanroom.byu.edu]

- 4. mdpi.com [mdpi.com]

- 5. researchgate.net [researchgate.net]

- 6. elib.bsu.by [elib.bsu.by]

- 7. piescientific.com [piescientific.com]

- 8. Plasma Cleaning of Surfaces using Glow Research plasma systems [glowresearch.org]

- 9. gtuttle.net [gtuttle.net]

- 10. poplab.stanford.edu [poplab.stanford.edu]

- 11. researchgate.net [researchgate.net]

- 12. researchgate.net [researchgate.net]

- 13. mdpi.com [mdpi.com]

- 14. researchgate.net [researchgate.net]

- 15. researchgate.net [researchgate.net]

- 16. discovery.ucl.ac.uk [discovery.ucl.ac.uk]

- 17. Effect of Plasma Argon Pretreatment on the Surface Properties of AZ31 Magnesium Alloy

PMC [pmc.ncbi.nlm.nih.gov]

- 18. swb.skku.edu [swb.skku.edu]

- To cite this document: BenchChem. [Technical Support Center: Optimizing Contact Resistance in In<sub>2</sub>Se<sub>3</sub> Transistors]. BenchChem, [2025]. [Online PDF]. Available at: [https://www.benchchem.com/product/b1233659#improving-contact-resistance-in-in-setransistors]

### **Disclaimer & Data Validity:**

The information provided in this document is for Research Use Only (RUO) and is strictly not intended for diagnostic or therapeutic procedures. While BenchChem strives to provide accurate protocols, we make no warranties, express or implied, regarding the fitness of this product for every specific experimental setup.

**Technical Support:**The protocols provided are for reference purposes. Unsure if this reagent suits your experiment? [Contact our Ph.D. Support Team for a compatibility check]

Need Industrial/Bulk Grade? Request Custom Synthesis Quote

# BenchChem

Our mission is to be the trusted global source of essential and advanced chemicals, empowering scientists and researchers to drive progress in science and industry. Contact

Address: 3281 E Guasti Rd

Ontario, CA 91761, United States

Phone: (601) 213-4426

Email: info@benchchem.com