## Technical Support Center: Optimizing Contact Resistance in DNTT OFETs

Author: BenchChem Technical Support Team. Date: December 2025

| Compound of Interest |         |           |  |  |  |

|----------------------|---------|-----------|--|--|--|

| Compound Name:       | Btqbt   |           |  |  |  |

| Cat. No.:            | B169727 | Get Quote |  |  |  |

This technical support center provides troubleshooting guidance and frequently asked questions (FAQs) to assist researchers in reducing contact resistance in Dinaphtho[2,3-b:2',3'-f]thieno[3,2-b]thiophene (DNTT) based Organic Field-Effect Transistors (OFETs).

### Frequently Asked Questions (FAQs)

Q1: What is contact resistance and why is it critical in DNTT OFETs?

A1: Contact resistance (Rc) is the parasitic resistance at the interface between the source/drain electrodes and the organic semiconductor layer. In DNTT OFETs, which are capable of high charge carrier mobility, a large contact resistance can severely limit the overall device performance by impeding efficient charge injection from the electrodes into the transistor channel.[1][2] This effect becomes more pronounced as the channel length of the transistor is scaled down.[2] A high contact resistance can lead to an underestimation of the intrinsic mobility of the DNTT, non-linear output characteristics at low drain voltages, and overall reduced device efficiency.[1]

Q2: What are the common causes of high contact resistance in DNTT OFETs?

A2: High contact resistance in DNTT OFETs can stem from several factors:

• Energy Barrier: A significant energy barrier between the work function of the electrode metal and the highest occupied molecular orbital (HOMO) of the p-type DNTT semiconductor hinders efficient hole injection.[1][3]

- Interface Contamination and Defects: Contaminants or defects at the electrodesemiconductor interface can act as charge traps, impeding charge carrier injection.[4]

- Poor Film Morphology: Non-uniform growth of the DNTT film on the electrode surface can lead to a poor physical and electrical interface, thereby increasing contact resistance.[2]

- Device Architecture: The choice between top-contact and bottom-contact device

architectures can influence the contact resistance, with factors like gate dielectric thickness

playing a crucial role.[3][4][5]

Q3: How is contact resistance in OFETs experimentally measured?

A3: The most common and standard technique for measuring contact resistance is the Transfer Line Method (TLM).[1][6][7] This method involves fabricating a series of transistors with identical channel widths but varying channel lengths. By plotting the total device resistance against the channel length for different gate voltages, the contact resistance can be extracted from the y-intercept. Other methods include the Y-function method and the gated four-point probe method.[1]

## Troubleshooting Guides

## Issue 1: Non-linear Output Characteristics at Low Drain Voltage

This is a classic symptom of high contact resistance, where the initial current increase is not linear with the drain voltage, indicating a barrier to charge injection.

#### **Troubleshooting Steps:**

- Verify Electrode Material: Ensure the electrode material has a suitable work function that aligns with the HOMO level of DNTT (approximately 5.3 eV).[5] Gold (Au) is a commonly used electrode material due to its high work function and chemical stability.[8]

- Implement Contact Doping: Introduce a thin layer of a p-type dopant, such as tetrafluorotetracyanoquinodimethane (F4TCNQ), at the electrode-semiconductor interface.[9]

[10] This can reduce the injection barrier and suppress variations in transistor parameters.[9]

- Apply a Self-Assembled Monolayer (SAM) to the Electrodes: Treating the electrode surface

with a SAM like pentafluorobenzenethiol (PFBT) can modify the work function of the metal to

better match the DNTT energy levels and improve the morphology of the subsequently

deposited organic film.[2][5]

- Optimize Electrode Deposition: The rate of metal deposition for the electrodes can influence

the grain size and surface morphology, which in turn affects the contact resistance.[11]

Slower deposition rates can lead to larger grains and more ordered SAM formation, reducing

contact resistance.[11]

## Issue 2: Measured Mobility is Lower than Expected and Gate Voltage Dependent

High contact resistance can lead to an underestimation of the charge carrier mobility and introduce a gate voltage dependency that is not intrinsic to the semiconductor material.

#### **Troubleshooting Steps:**

- Measure Contact Resistance using TLM: First, quantify the contact resistance using the Transfer Line Method to confirm it is a significant contributor to the total device resistance.

- Introduce an Interlayer: Inserting a thin metal oxide layer, such as Molybdenum Oxide (MoOx), between the electrode and the DNTT can improve charge injection and reduce contact resistance.[1][10]

- Consider Device Architecture: For bottom-contact devices, a thinner gate dielectric can surprisingly lead to lower contact resistance.[4][5] If using a top-contact architecture, ensure the deposition of the DNTT film creates a clean and intimate interface with the subsequently deposited electrodes.

- Surface Treatment of the Dielectric: Treating the dielectric surface with a silanizing agent like hexamethyldisilazane (HMDS) before DNTT deposition can improve the film quality and indirectly lead to better contact properties, significantly decreasing contact resistance.[12]

### **Quantitative Data Summary**

| Treatment<br>Method                         | Device<br>Architectur<br>e  | Semicondu<br>ctor | Electrode<br>Material | Achieved<br>Contact<br>Resistance<br>(Ω·cm)          | Reference |

|---------------------------------------------|-----------------------------|-------------------|-----------------------|------------------------------------------------------|-----------|

| Contact<br>Doping<br>(F4TCNQ)               | Bottom-gate,<br>Top-contact | DNTT              | -                     | Gate-voltage<br>dependence<br>suppressed             | [9]       |

| Optimized Metal Deposition + SAM            | Bottom-<br>contact          | C10-DNTT          | Au                    | As low as<br>200                                     | [2][11]   |

| SAM<br>Treatment<br>(PFBT)                  | Bottom-<br>contact          | DPh-DNTT          | Au                    | Lower than<br>top-contact<br>with thin<br>dielectric | [5]       |

| Interface<br>Doping<br>(F4TCNQ)             | Bottom-gate,<br>Top-contact | Pentacene         | Au                    | 10 kΩ·cm<br>(from 55<br>kΩ·cm)                       | [10]      |

| Monolayer<br>OFET with<br>vdW<br>Electrodes | -                           | C10-DNTT          | -                     | 89.9                                                 | [13]      |

| HMDS<br>Surface<br>Treatment                | -                           | DNTT              | -                     | Prominent<br>decrease (up<br>to one-tenth)           | [12]      |

# Experimental Protocols Protocol 1: Contact Doping with F4TCNQ

This protocol describes the introduction of a p-type dopant at the electrode-semiconductor interface for a top-contact device architecture.

• Substrate Preparation: Begin with a clean gate dielectric on a substrate (e.g., SiO2 on Si).

- DNTT Deposition: Thermally evaporate DNTT onto the substrate to the desired thickness. The substrate temperature should be optimized (e.g., 60 °C) for high-quality film growth.[12]

- Dopant Deposition: Through a shadow mask aligned with the desired source and drain regions, thermally evaporate a very thin layer (e.g., 1 nm) of F4TCNQ onto the DNTT film.

[10]

- Electrode Deposition: Without breaking vacuum, deposit the source and drain electrodes (e.g., Gold) on top of the F4TCNQ layer through the same shadow mask.

#### Protocol 2: Electrode Modification with PFBT SAM

This protocol is for treating the electrodes in a bottom-contact device architecture.

- Substrate and Electrode Fabrication: Fabricate the gate electrode, gate dielectric, and source/drain electrodes on the substrate using standard lithography and deposition techniques.

- Substrate Cleaning: Thoroughly clean the substrate with the patterned electrodes using a sequence of solvents (e.g., acetone, isopropanol) and O2 plasma treatment.

- SAM Formation: Immerse the substrate in a dilute solution of pentafluorobenzenethiol

(PFBT) in a suitable solvent (e.g., ethanol) for a specified duration (e.g., 24 hours) to allow

for the formation of a self-assembled monolayer on the electrode surfaces.

- Rinsing and Drying: Rinse the substrate with the pure solvent to remove any unbound PFBT molecules and then dry it with an inert gas (e.g., N2).

- DNTT Deposition: Proceed with the thermal evaporation of the DNTT semiconductor layer onto the SAM-treated substrate.

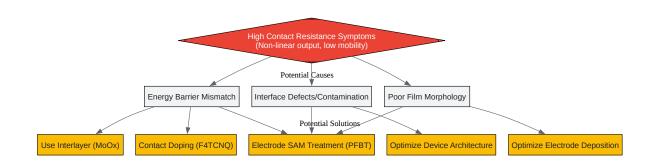

### **Diagrams**

#### Click to download full resolution via product page

Caption: Workflow for Contact Doping in a Top-Contact DNTT OFET.

#### Click to download full resolution via product page

Caption: Troubleshooting Logic for High Contact Resistance in DNTT OFETs.

#### **Need Custom Synthesis?**

BenchChem offers custom synthesis for rare earth carbides and specific isotopiclabeling.

Email: info@benchchem.com or Request Quote Online.

#### References

- 1. researchgate.net [researchgate.net]

- 2. A simple and robust approach to reducing contact resistance in organic transistors PMC [pmc.ncbi.nlm.nih.gov]

- 3. pubs.aip.org [pubs.aip.org]

- 4. researchgate.net [researchgate.net]

- 5. fkf.mpg.de [fkf.mpg.de]

- 6. mdpi.com [mdpi.com]

- 7. pubs.aip.org [pubs.aip.org]

- 8. researchgate.net [researchgate.net]

- 9. keio.elsevierpure.com [keio.elsevierpure.com]

- 10. researchgate.net [researchgate.net]

- 11. communities.springernature.com [communities.springernature.com]

- 12. researchgate.net [researchgate.net]

- 13. The Origin of Low Contact Resistance in Monolayer Organic Field-Effect Transistors with van der Waals Electrodes PMC [pmc.ncbi.nlm.nih.gov]

- To cite this document: BenchChem. [Technical Support Center: Optimizing Contact Resistance in DNTT OFETs]. BenchChem, [2025]. [Online PDF]. Available at: [https://www.benchchem.com/product/b169727#reducing-contact-resistance-in-btqbt-ofets]

#### **Disclaimer & Data Validity:**

The information provided in this document is for Research Use Only (RUO) and is strictly not intended for diagnostic or therapeutic procedures. While BenchChem strives to provide accurate protocols, we make no warranties, express or implied, regarding the fitness of this product for every specific experimental setup.

**Technical Support:** The protocols provided are for reference purposes. Unsure if this reagent suits your experiment? [Contact our Ph.D. Support Team for a compatibility check]

Need Industrial/Bulk Grade? Request Custom Synthesis Quote

### BenchChem

Our mission is to be the trusted global source of essential and advanced chemicals, empowering scientists and researchers to drive progress in science and industry. Contact

Address: 3281 E Guasti Rd

Ontario, CA 91761, United States

Phone: (601) 213-4426

Email: info@benchchem.com