# Technical Support Center: Optimizing CPDT-based Solar Cell Power Conversion Efficiency

Author: BenchChem Technical Support Team. Date: December 2025

| Compound of Interest |         |           |

|----------------------|---------|-----------|

| Compound Name:       | CPDT    |           |

| Cat. No.:            | B076147 | Get Quote |

This technical support center provides troubleshooting guides and frequently asked questions (FAQs) to assist researchers in optimizing the power conversion efficiency (PCE) of their Cyclopentadithiophene (CPDT)-based solar cells.

### **Frequently Asked Questions (FAQs)**

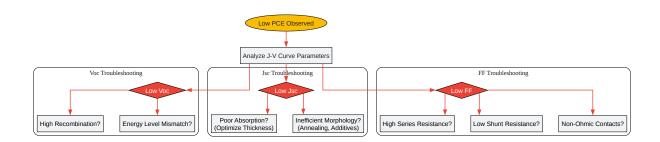

Q1: My **CPDT**-based solar cell has a very low Power Conversion Efficiency (PCE). What are the primary factors I should investigate?

A1: A low PCE is typically a result of suboptimal values for one or more of the key solar cell parameters: open-circuit voltage (Voc), short-circuit current density (Jsc), and fill factor (FF). A systematic approach to troubleshooting involves evaluating each of these parameters to pinpoint the underlying issue. Common areas to investigate include the active layer morphology, interfacial layers, and overall device architecture.

Q2: What are the common causes of a low open-circuit voltage (Voc) in **CPDT**-based solar cells?

A2: A low Voc can stem from several factors.[1] It is a measure of the quality and bandgap of your absorber material and the dominant recombination processes within your device.[1] Potential causes include:

High recombination rates: Recombination of charge carriers at the donor-acceptor interface or at the electrode interfaces is a primary cause of reduced Voc.

#### Troubleshooting & Optimization

- Energy level mismatch: Improper alignment of the energy levels between the **CPDT**-based donor polymer, the acceptor material (e.g., PCBM), and the charge transport layers can lead to voltage losses.

- Presence of trap states: Defects or impurities within the active layer can create trap states that facilitate recombination.[1]

- High reverse saturation current: This indicates a high rate of recombination in the device.

Q3: Why is the short-circuit current density (Jsc) in my device lower than expected?

A3: Low Jsc is often related to inefficient light absorption or poor charge carrier collection. Key factors include:

- Suboptimal active layer thickness: If the active layer is too thin, it may not absorb a sufficient amount of incident light. Conversely, if it is too thick, charge carriers may recombine before reaching the electrodes.

- Poor active layer morphology: An unfavorable morphology can lead to inefficient exciton dissociation and charge transport.

- Optical interference effects: The thickness of each layer in the device can lead to destructive optical interference, reducing the amount of light absorbed by the active layer.

- High series resistance: High resistance in any of the device layers can impede the flow of current.

Q4: My device has a good Voc and Jsc, but the fill factor (FF) is low. What could be the reason?

A4: A low fill factor, even with good Voc and Jsc, is a common issue and often points to problems with charge transport and collection.[2] Possible causes include:

High series resistance (Rs): This can be due to the bulk resistance of the active and transport layers, or high contact resistance at the electrode interfaces.[2][3]

- Low shunt resistance (Rsh): This is often caused by leakage currents, for example, through pinholes or defects in the active layer that create shorting pathways between the electrodes.

- Non-ohmic contacts: Poor contacts between the active layer and the electrodes can create a barrier to charge extraction, resulting in an "S-shaped" J-V curve and a low FF.[3]

- Unbalanced charge carrier mobility: A significant mismatch in the electron and hole mobilities within the active layer can lead to space-charge effects that limit the FF.

## **Troubleshooting Guides Issue 1: Low Fill Factor (FF)**

Symptoms: The J-V curve is not "square-shaped" and may exhibit an "S-kink" near the open-circuit voltage. The calculated FF is below the expected values for your material system.

Possible Causes & Solutions:

| Possible Cause              | Suggested Troubleshooting Steps                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |

|-----------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| High Series Resistance (Rs) | 1. Optimize Active Layer Thickness: A very thick active layer increases bulk resistance.  Systematically vary the spin coating speed to achieve different thicknesses and identify the optimum.[4] 2. Improve Interfacial Layers: Ensure the hole transport layer (e.g., PEDOT:PSS) and electron transport layer provide good electrical contact. Consider alternative transport layer materials or optimizing their thickness and annealing conditions. 3. Check Electrode Deposition: Ensure a good vacuum and slow deposition rate during metal electrode evaporation to create a uniform and highly conductive contact. |  |  |  |

| Low Shunt Resistance (Rsh)  | 1. Improve Film Quality: Filter the polymer and fullerene solutions before spin coating to remove aggregates that can cause pinholes. 2. Optimize Spin Coating Environment: Work in a cleanroom environment to minimize dust contamination which can lead to shorting.[5] 3. Inspect Substrates: Thoroughly clean and inspect the ITO substrates for any defects before device fabrication.                                                                                                                                                                                                                                 |  |  |  |

| Non-Ohmic Contacts          | 1. Introduce an Interfacial Layer: Use a thin interfacial layer between the active layer and the cathode (e.g., LiF, Ca) to improve electron extraction. 2. Modify the Cathode: Use a low work function metal for the cathode to ensure an ohmic contact for electron collection.                                                                                                                                                                                                                                                                                                                                           |  |  |  |

### Issue 2: Low Open-Circuit Voltage (Voc)

Symptoms: The measured Voc is significantly lower than the theoretical maximum, which is related to the energy difference between the HOMO of the donor (CPDT polymer) and the

LUMO of the acceptor (e.g., PCBM).

Possible Causes & Solutions:

| Possible Cause           | Suggested Troubleshooting Steps                                                                                                                                                                                                                                                                                                                                        |  |

|--------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| High Recombination Rates | 1. Optimize Active Layer Morphology: Use solvent additives (e.g., 1,8-diiodooctane) or post-deposition annealing (thermal or solvent vapor) to induce a more favorable nanostructure that facilitates efficient charge separation and reduces recombination.[3] 2. Passivate Surfaces: Introduce surface passivating layers to reduce recombination at the interfaces. |  |

| Energy Level Mismatch    | 1. Select Appropriate Materials: Ensure the HOMO and LUMO levels of the donor, acceptor, and transport layers are well-aligned for efficient charge transfer and minimal energy loss.                                                                                                                                                                                  |  |

### **Issue 3: Low Short-Circuit Current (Jsc)**

Symptoms: The current density at zero voltage is lower than reported values for similar **CPDT**-based devices.

Possible Causes & Solutions:

| Possible Cause                          | Suggested Troubleshooting Steps                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |

|-----------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Poor Light Absorption                   | Optimize Active Layer Thickness:  Systematically vary the active layer thickness to find the optimal balance between light absorption and charge extraction. Thicker films absorb more light but can suffer from higher recombination.[6][7]                                                                                                                                                                                                                           |  |  |

| Inefficient Charge Generation/Transport | 1. Optimize Morphology with Annealing: Post-fabrication thermal annealing can improve the crystallinity and domain size within the active layer, leading to better exciton dissociation and charge transport. Experiment with different annealing temperatures and times.[8][9] 2. Utilize Solvent Additives: Small amounts of high-boiling-point solvent additives can slow down the drying of the active layer, allowing for better phase separation and morphology. |  |  |

### **Quantitative Data Summary**

The following table summarizes the performance of **CPDT**-based solar cells under various experimental conditions as reported in the literature.

| Donor<br>Polymer                 | Accepto<br>r            | Additive | Anneali<br>ng<br>Conditi<br>ons                     | Voc (V) | Jsc<br>(mA/cm²<br>) | FF (%) | PCE (%)           |

|----------------------------------|-------------------------|----------|-----------------------------------------------------|---------|---------------------|--------|-------------------|

| Crosslink able PCPDTB T analogue | Fullerene<br>derivative | None     | -                                                   | -       | -                   | -      | 2.0               |

| Crosslink able PCPDTB T analogue | Fullerene<br>derivative | Dithiol  | -                                                   | -       | -                   | -      | 3.7[2]            |

| PCDTBT                           | PC71BM                  | None     | Annealin g > 140°C leads to decrease d performa nce | -       | -                   | -      | Decrease<br>d[10] |

| PBDTT-<br>DPP                    | Fullerene               | -        | -                                                   | -       | -                   | -      | 8.91[11]          |

# **Experimental Protocols**Substrate Cleaning

A thorough cleaning of the ITO-coated glass substrates is crucial for good device performance. [5]

- Load substrates into a cleaning rack.

- Sonicate in a sequence of solvents, for instance:

- Detergent solution (15 minutes)

- Deionized water (15 minutes)

- Acetone (15 minutes)[12]

- Isopropyl alcohol (15 minutes)[12]

- Dry the substrates with a nitrogen gun and store them in a clean environment.

#### **Hole Transport Layer (HTL) Deposition**

- Deposit a layer of PEDOT:PSS onto the cleaned ITO substrates.

- Spin coat the PEDOT:PSS solution. A typical procedure is to use a filtered solution and spin coat in a nitrogen-filled glovebox.

- Anneal the PEDOT:PSS layer on a hotplate. A common annealing condition is 150°C for 5-10 minutes to remove residual water.[5]

#### **Active Layer Deposition**

- Prepare a solution of the CPDT-based polymer and the acceptor (e.g., PCBM) in a suitable solvent like chlorobenzene or dichlorobenzene. The ratio of donor to acceptor and the total concentration should be optimized.

- If using a solvent additive, add it to the solution at this stage.

- Spin coat the active layer solution onto the HTL. The spin speed and time will determine the thickness of the active layer.[13][14]

- Allow the film to dry.

## Post-Deposition Annealing (Optional but often necessary)

• Thermal Annealing: Place the substrates on a hotplate in a nitrogen-filled glovebox at a specific temperature (e.g., 80-160°C) for a defined time (e.g., 5-15 minutes).[8][9]

Solvent Vapor Annealing: Place the substrates in a sealed chamber containing a small amount of a specific solvent. The solvent vapor will slowly plasticize the active layer, allowing for morphological rearrangement.[3][15]

### **Cathode Deposition**

- Transfer the substrates to a thermal evaporator.

- If required, deposit a thin interfacial layer (e.g., LiF or Ca).

- Deposit the metal cathode (e.g., Aluminum) under high vacuum. The deposition rate should be controlled to ensure a uniform film.

#### **Visualizations**

Click to download full resolution via product page

Caption: Experimental workflow for the fabrication of a CPDT-based solar cell.

#### Click to download full resolution via product page

Caption: Logical workflow for troubleshooting low Power Conversion Efficiency (PCE).

#### **Need Custom Synthesis?**

BenchChem offers custom synthesis for rare earth carbides and specific isotopiclabeling.

Email: info@benchchem.com or Request Quote Online.

#### References

- 1. ossila.com [ossila.com]

- 2. researchgate.net [researchgate.net]

- 3. Solvent annealing for morphology control to realize high efficiency all-small-molecule organic solar cells Sustainable Energy & Fuels (RSC Publishing) [pubs.rsc.org]

- 4. researchgate.net [researchgate.net]

- 5. ossila.com [ossila.com]

- 6. researchgate.net [researchgate.net]

- 7. Evaluation of Active Layer Thickness Influence in Long-Term Stability and Degradation Mechanisms in CsFAPbIBr Perovskite Solar Cells [mdpi.com]

- 8. mdpi.com [mdpi.com]

- 9. researchgate.net [researchgate.net]

- 10. Influence of Thermal Annealing on PCDTBT:PCBM Composition Profiles | Semantic Scholar [semanticscholar.org]

- 11. researchgate.net [researchgate.net]

- 12. mdpi.com [mdpi.com]

- 13. louisville.edu [louisville.edu]

- 14. m.youtube.com [m.youtube.com]

- 15. Effects of Solvent Vapor Annealing on Morphology and Charge Transport of Poly(3-hexylthiophene) (P3HT) Films Incorporated with Preformed P3HT Nanowires PubMed [pubmed.ncbi.nlm.nih.gov]

- To cite this document: BenchChem. [Technical Support Center: Optimizing CPDT-based Solar Cell Power Conversion Efficiency]. BenchChem, [2025]. [Online PDF]. Available at: [https://www.benchchem.com/product/b076147#optimizing-cpdt-based-solar-cell-power-conversion-efficiency]

#### **Disclaimer & Data Validity:**

The information provided in this document is for Research Use Only (RUO) and is strictly not intended for diagnostic or therapeutic procedures. While BenchChem strives to provide accurate protocols, we make no warranties, express or implied, regarding the fitness of this product for every specific experimental setup.

**Technical Support:** The protocols provided are for reference purposes. Unsure if this reagent suits your experiment? [Contact our Ph.D. Support Team for a compatibility check]

Need Industrial/Bulk Grade? Request Custom Synthesis Quote

## BenchChem

Our mission is to be the trusted global source of essential and advanced chemicals, empowering scientists and researchers to drive progress in science and industry. Contact

Address: 3281 E Guasti Rd

Ontario, CA 91761, United States

Phone: (601) 213-4426

Email: info@benchchem.com