# Technical Support Center: Optimizing Annealing for MoS<sub>2</sub> Device Fabrication

Author: BenchChem Technical Support Team. Date: December 2025

| Compound of Interest |                    |           |

|----------------------|--------------------|-----------|

| Compound Name:       | Molybdenum sulfide |           |

| Cat. No.:            | B1676702           | Get Quote |

This technical support center provides researchers, scientists, and drug development professionals with troubleshooting guides and frequently asked questions (FAQs) to address common challenges encountered during the annealing stage of MoS<sub>2</sub> device fabrication.

#### **Troubleshooting Guides**

This section addresses specific issues that may arise during your experiments, offering potential causes and solutions.

Issue 1: High Contact Resistance in Fabricated MoS<sub>2</sub> Devices

- Question: My MoS<sub>2</sub> field-effect transistors (FETs) exhibit very high contact resistance after fabrication. How can I reduce it?

- Answer: High contact resistance is a common issue in MoS<sub>2</sub> devices, often stemming from a poor interface between the metal contacts and the MoS<sub>2</sub> channel. Annealing is a critical step to improve this interface.

- Solution 1: Post-Deposition Annealing. A post-deposition anneal is crucial for reducing contact resistance.[1][2] For instance, annealing devices with silver (Ag) contacts at temperatures between 250°C and 300°C has been shown to significantly decrease contact resistance from a range of 0.8–3.5 kΩ·μm down to 0.2–0.7 kΩ·μm.[1][2][3] This improvement is attributed to the diffusion of the contact metal into the MoS<sub>2</sub>, leading to localized doping.[1][2]

#### Troubleshooting & Optimization

- Solution 2: Stepped Annealing. Instead of a single annealing step, a "stepped annealing" approach can be more effective.[4] This involves a gradual increase in temperature. An optimized stepped anneal in an Argon (Ar) atmosphere at 300°C has been demonstrated to reduce contact resistance from 209.3 kΩ·μm to 4.7 kΩ·μm.[4] This method helps in minimizing the Schottky barrier height, thereby improving the electrical properties of the contact.[4]

- Solution 3: Choice of Annealing Environment. The annealing ambient plays a significant role. Inert atmospheres like Argon (Ar) or Nitrogen (N<sub>2</sub>) are commonly used to prevent oxidation of the MoS<sub>2</sub>.[4][5] Vacuum annealing is another effective method to remove contaminants and improve contact quality.[6]

#### Issue 2: Inconsistent and Poor Device Performance After Annealing

- Question: The electrical characteristics of my MoS<sub>2</sub> devices, such as mobility and on/off ratio, are poor and vary significantly across different devices even after annealing. What could be the cause?

- Answer: Inconsistent device performance can be due to several factors, including residual

contaminants from the fabrication process, structural defects in the MoS<sub>2</sub>, or non-optimal

annealing parameters.

- Solution 1: Surface Cleaning Prior to Dielectric Deposition. For top-gated devices, it is

essential to have a clean MoS<sub>2</sub> surface before depositing the high-k dielectric. An ultrahigh vacuum (UHV) anneal before dielectric deposition can effectively clean the surface,

leading to a higher quality dielectric layer with reduced leakage current.[6]

- Solution 2: Optimize Annealing Temperature. The annealing temperature needs to be carefully optimized. While higher temperatures can improve crystallinity, excessively high temperatures can lead to degradation of the MoS<sub>2</sub> film. For instance, monolayer MoS<sub>2</sub> has been found to be stable up to 700°C in a vacuum, with significant degradation occurring at 800°C.[7] A study on sputtered MoS<sub>2</sub> films showed that post-annealing at 450°C in a nitrogen flow improved crystallinity.[5]

- Solution 3: Consider Forming Gas Anneal. Annealing in a forming gas (a mixture of hydrogen and nitrogen) can passivate charged defects.[6] For example, a 400°C anneal in

forming gas has been shown to reduce charged defects, decrease I-V hysteresis, and lower gate leakage in top-gated MoS<sub>2</sub> transistors.[6]

Issue 3: Degradation of MoS<sub>2</sub> Film During High-Temperature Annealing

- Question: I am observing degradation or even disappearance of my MoS<sub>2</sub> flakes after hightemperature annealing. How can I prevent this?

- Answer: MoS2 can be susceptible to thermal degradation, especially at the monolayer level.

- Solution 1: Control the Annealing Temperature and Environment. As mentioned, monolayer MoS<sub>2</sub> can degrade at temperatures above 700°C in a vacuum due to sulfur loss.[7] It is crucial to stay within the stable temperature range for your specific MoS<sub>2</sub> thickness and annealing environment. Annealing in a sulfur-rich atmosphere can help to mitigate sulfur vacancy formation at high temperatures.

- Solution 2: Rapid Thermal Annealing (RTA) or Laser Annealing. Conventional furnace annealing involves prolonged exposure to high temperatures. Alternative methods like Rapid Thermal Annealing (RTA) or laser annealing can provide rapid heating and cooling, minimizing the time the material spends at high temperatures and thus reducing the risk of degradation.[8][9] Femtosecond laser pulse annealing, for example, can rapidly process the material, suppressing surface defects while avoiding the thermal effects of traditional annealing.[8]

#### Frequently Asked Questions (FAQs)

Q1: What is the optimal annealing temperature for MoS2 devices?

The optimal annealing temperature is not a single value but depends on several factors including the substrate, the contact metals, the thickness of the MoS<sub>2</sub> film, and the desired outcome. However, several studies provide guidance:

- For reducing contact resistance with Ag contacts, 250-300°C is effective.[1][2]

- A stepped anneal in an Ar atmosphere up to 300°C has shown excellent results for improving overall device performance.[4]

- For improving the optical and structural quality of CVD-grown monolayer MoS<sub>2</sub>, annealing in an Ar-diluted sulfur atmosphere at temperatures between 800-860°C has been explored.[10]

- For sputtered MoS<sub>2</sub> films, a post-annealing step at 450°C in nitrogen can improve crystallinity.[5]

Q2: What is the effect of the annealing atmosphere on device performance?

The annealing atmosphere is critical to prevent unwanted chemical reactions.

- Inert Atmospheres (Ar, N<sub>2</sub>): These are the most common choices to prevent oxidation of the MoS<sub>2</sub> and the metal contacts.[4][5]

- Vacuum: Annealing in a vacuum is effective for removing adsorbed molecules and residues from the fabrication process.[6]

- Forming Gas (H<sub>2</sub>/N<sub>2</sub>): This atmosphere can be used to passivate defects, particularly in the gate dielectric of top-gated transistors.[6]

- Sulfur-containing Atmosphere: To prevent the formation of sulfur vacancies at high annealing temperatures, an atmosphere containing sulfur can be beneficial.[10]

Q3: How does annealing affect the different properties of a MoS<sub>2</sub> FET?

Annealing can significantly improve several key performance metrics of a MoS<sub>2</sub> FET:

- Contact Resistance: Generally decreases significantly, leading to higher drive currents.[1][2]

[4]

- Carrier Mobility: Often increases due to improved contact quality and reduction of defects.

- On/Off Ratio: Can be improved by several orders of magnitude.[4]

- Subthreshold Swing (SS): A reduction in the SS indicates a lower density of interface traps. [4]

- Hysteresis: Can be reduced, indicating fewer charge traps in the dielectric or at the interface.

[11][12]

## **Quantitative Data Summary**

The following table summarizes the impact of different annealing conditions on the performance of MoS<sub>2</sub> devices as reported in various studies.

| Annealing<br>Method  | Temperatur<br>e (°C) | Atmospher<br>e | Contact<br>Metal | Key<br>Improveme<br>nt                                                                                                 | Reference |

|----------------------|----------------------|----------------|------------------|------------------------------------------------------------------------------------------------------------------------|-----------|

| Stepped<br>Annealing | 300                  | Ar             | -                | Contact resistance reduced from 209.3 to 4.7 kΩ·μm; Mobility improved ~10x.[4]                                         | [4]       |

| Thermal<br>Annealing | 250 - 300            | -              | Ag               | Contact resistance reduced from 0.8–3.5 to 0.2–0.7 kΩ·μm.[1][2]                                                        | [1][2][3] |

| Thermal<br>Annealing | 400                  | Forming Gas    | -                | Reduced charged defects, decreased hysteresis, and lower gate leakage.                                                 | [6]       |

| Thermal<br>Annealing | 850                  | -              | -                | Conductivity reached $2.848 \times 10^{-4}$ S/m and carrier mobility up to $6.42 \times 10^2$ cm <sup>2</sup> /Vs.[13] | [13]      |

| Pulsed Laser<br>Annealing | -   | -              | Ag/Au | Peak field- effect mobility increased from 60 to 135 cm² V⁻¹ s⁻¹; Contact resistance decreased to 0.29 kΩ·μm. [14] | [14] |

|---------------------------|-----|----------------|-------|--------------------------------------------------------------------------------------------------------------------|------|

| Post-<br>Annealing        | 450 | N <sub>2</sub> | -     | Improved<br>crystallinity of<br>sputtered<br>MoS <sub>2</sub> films.[5]                                            | [5]  |

### **Experimental Protocols**

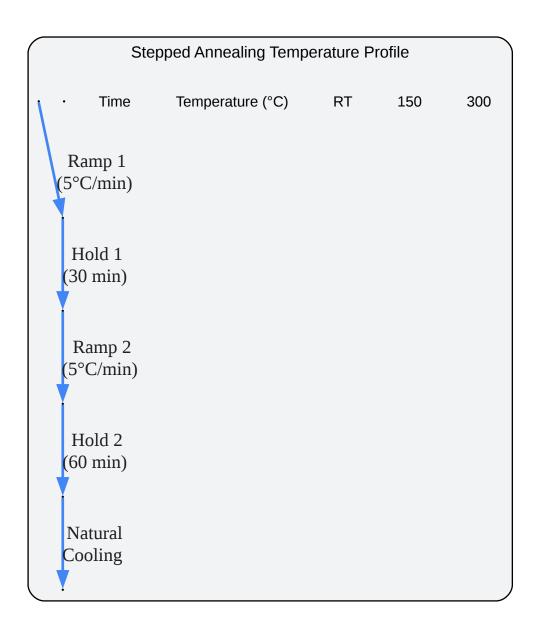

Protocol 1: Stepped Annealing for Contact Resistance Reduction

This protocol is based on the method described for significantly improving the contact interface and overall device performance.[4]

- Device Placement: Place the fabricated MoS2 devices in the center of a tube furnace.

- Purging: Purge the furnace tube with high-purity Argon (Ar) gas for at least 30 minutes to create an inert environment. Maintain a constant Ar flow throughout the process.

- Heating Ramp:

- Ramp the temperature from room temperature to 150°C at a rate of 5°C/min.

- Hold the temperature at 150°C for 30 minutes.

- Ramp the temperature from 150°C to 300°C at a rate of 5°C/min.

- Hold the temperature at 300°C for 60 minutes.

- Cooling: After the hold time, turn off the furnace and let the devices cool down naturally to room temperature under the continuous Ar flow.

- Characterization: Once at room temperature, the devices can be removed for electrical characterization.

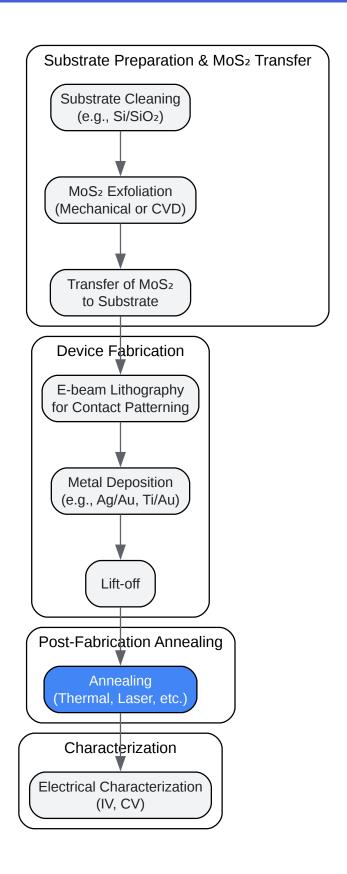

## **Diagrams**

Click to download full resolution via product page

Caption: Workflow for MoS<sub>2</sub> device fabrication, highlighting the critical post-fabrication annealing step.

Click to download full resolution via product page

Caption: Temperature profile for an optimized stepped annealing process.

#### **Need Custom Synthesis?**

BenchChem offers custom synthesis for rare earth carbides and specific isotopiclabeling.

Email: info@benchchem.com or Request Quote Online.

#### References

- 1. pubs.aip.org [pubs.aip.org]

- 2. pubs.aip.org [pubs.aip.org]

- 3. researchgate.net [researchgate.net]

- 4. Reducing MoS2 FET contact resistance by stepped annealing to optimize device performance - Journal of Materials Chemistry C (RSC Publishing) [pubs.rsc.org]

- 5. ira.lib.polyu.edu.hk [ira.lib.polyu.edu.hk]

- 6. pubs.aip.org [pubs.aip.org]

- 7. researchgate.net [researchgate.net]

- 8. spiedigitallibrary.org [spiedigitallibrary.org]

- 9. The Impact of Microwave Annealing on MoS2 Devices Assisted by Neural Network-Based Big Data Analysis PMC [pmc.ncbi.nlm.nih.gov]

- 10. Temperature-dependent properties of monolayer MoS2 annealed in an Ar diluted S atmosphere: an experimental and first-principles study Journal of Materials Chemistry C (RSC Publishing) [pubs.rsc.org]

- 11. pubs.acs.org [pubs.acs.org]

- 12. On the Contact Optimization of ALD-Based MoS2 FETs: Correlation of Processing Conditions and Interface Chemistry with Device Electrical Performance PMC [pmc.ncbi.nlm.nih.gov]

- 13. researchgate.net [researchgate.net]

- 14. pubs.acs.org [pubs.acs.org]

- To cite this document: BenchChem. [Technical Support Center: Optimizing Annealing for MoS<sub>2</sub> Device Fabrication]. BenchChem, [2025]. [Online PDF]. Available at: [https://www.benchchem.com/product/b1676702#optimizing-annealing-conditions-for-mos-device-fabrication]

#### **Disclaimer & Data Validity:**

The information provided in this document is for Research Use Only (RUO) and is strictly not intended for diagnostic or therapeutic procedures. While BenchChem strives to provide accurate protocols, we make no warranties, express or implied, regarding the fitness of this product for every specific experimental setup.

**Technical Support:**The protocols provided are for reference purposes. Unsure if this reagent suits your experiment? [Contact our Ph.D. Support Team for a compatibility check]

Need Industrial/Bulk Grade? Request Custom Synthesis Quote

## BenchChem

Our mission is to be the trusted global source of essential and advanced chemicals, empowering scientists and researchers to drive progress in science and industry. Contact

Address: 3281 E Guasti Rd

Ontario, CA 91761, United States

Phone: (601) 213-4426

Email: info@benchchem.com