Check Availability & Pricing

# Technical Support Center: Optimizing ALD-Grown AlO<sub>x</sub> Films for Enhanced Mobility

Author: BenchChem Technical Support Team. Date: November 2025

| Compound of Interest |                 |           |

|----------------------|-----------------|-----------|

| Compound Name:       | Aluminum;indium |           |

| Cat. No.:            | B15444497       | Get Quote |

This technical support center provides troubleshooting guidance and frequently asked questions for researchers and scientists working on the optimization of aluminum concentration in ALD-grown aluminum oxide (AlO<sub>x</sub>) films, with a focus on maximizing charge carrier mobility in thin-film transistor devices.

### Frequently Asked Questions (FAQs)

Q1: What is the primary role of the ALD-grown AlO<sub>x</sub> film when optimizing for mobility?

A1: In most electronic applications, aluminum oxide (AlO<sub>×</sub>) is used as a high-quality gate dielectric material in field-effect transistors (FETs). Its primary role is to efficiently couple the gate voltage to the semiconductor channel, enabling the accumulation of charge carriers and turning the transistor "on". A high-quality AlO<sub>×</sub> dielectric minimizes charge trapping and scattering at the dielectric/semiconductor interface, which is crucial for achieving high carrier mobility in the channel.

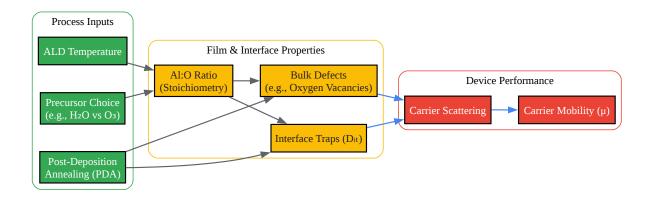

Q2: How does the "aluminum concentration" or stoichiometry of the AlO<sub>x</sub> film affect mobility?

A2: The stoichiometry of the aluminum oxide film, which can be described as  $AlO_x$ , plays a critical role. ALD-grown films are often not perfectly stoichiometric  $Al_2O_3$  and can contain oxygen vacancies or excess oxygen, as well as hydrogen impurities.[1][2] These deviations from ideal stoichiometry create defects within the film and at the interface.

- Oxygen Vacancies: These are common defects in ALD Al<sub>2</sub>O<sub>3</sub> and can act as charge traps.[3]

Trapped charges can scatter the charge carriers in the transistor channel, thereby reducing mobility.[3]

- Fixed Charges: Non-stoichiometry can also lead to fixed charges within the dielectric, which can alter the threshold voltage of the transistor and increase carrier scattering.[3] Optimizing the ALD process parameters, such as precursor choice and deposition temperature, can help control the film's stoichiometry and reduce these performance-limiting defects.[1][4]

Q3: Is post-deposition annealing (PDA) necessary for achieving high mobility?

A3: Yes, post-deposition annealing is a critical step for activating and improving the quality of the AlO<sub>x</sub> dielectric and the dielectric/semiconductor interface. Annealing can help to densify the film, reduce the concentration of impurities like hydrogen, and repair defects.[1] For silicon-based devices, PDA can also promote the formation of a thin, high-quality SiO<sub>2</sub> interfacial layer, which can lead to a lower density of interface traps and improved surface passivation.

Q4: What are typical mobility values for devices using ALD Al<sub>2</sub>O<sub>3</sub> as a gate dielectric?

A4: Mobility is highly dependent on the semiconductor channel material, not the AlO<sub>x</sub> itself. However, the quality of the AlO<sub>x</sub> dielectric is what allows the channel material to achieve its potential. For example:

- In graphene-based FETs, mobilities exceeding 8,000 cm²/Vs have been achieved with ALD Al<sub>2</sub>O<sub>3</sub> top gates.[5][6]

- For GaN MOSFETs, channel mobilities around 414 cm<sup>2</sup>/V·s have been reported, showing that the ALD process did not degrade the channel.[7]

- In pentacene organic FETs, hole mobilities of up to 1.5 cm²/V⋅s have been demonstrated using ALD Al<sub>2</sub>O<sub>3</sub>.[8]

### **Troubleshooting Guide**

Problem: My measured carrier mobility is significantly lower than expected.

#### Troubleshooting & Optimization

This is a common issue that can originate from various stages of the device fabrication and measurement process. Follow this guide to diagnose the potential cause.

Q1: Have you optimized the ALD growth parameters for the AlOx film?

A1: The quality of the ALD film is fundamental. Non-ideal growth conditions can lead to a high density of bulk and interface defects, which are detrimental to mobility.

- Check Deposition Temperature: The ALD temperature window is critical. Temperatures that are too low can result in incomplete reactions and high impurity content (e.g., hydrogen), while temperatures that are too high can cause precursor decomposition.[1] Both scenarios can increase defect density.

- Verify Precursor Pulse and Purge Times: Inadequate pulse times lead to incomplete surface reactions, while insufficient purge times can cause parasitic chemical vapor deposition (CVD) reactions. Both will degrade film quality. Ensure you are operating within the ALD saturation regime for your specific reactor.

Q2: Is the interface between the semiconductor and the AlOx dielectric of high quality?

A2: The interface is where charge transport occurs, making it the most critical region. A poor interface will severely limit mobility due to charge trapping and scattering.

- Surface Preparation: Was the semiconductor surface properly cleaned and prepared before ALD deposition? Contaminants or a poor-quality native oxide can create a high density of interface traps.

- Post-Deposition Annealing (PDA): As mentioned in the FAQ, PDA is crucial. The annealing temperature and ambient (e.g., N<sub>2</sub>, O<sub>2</sub>, forming gas) must be optimized for your specific semiconductor system to passivate interface defects.

Q3: Are there extrinsic factors from the device fabrication or measurement process affecting the results?

A3: Issues unrelated to the AlO<sub>x</sub> film itself can lead to erroneously low mobility calculations.

- Contact Resistance: High resistance at the source and drain contacts can lead to an underestimation of the intrinsic channel mobility.

- Mobility Calculation Method: Are you using the correct model to extract mobility? The

standard MOSFET equations may not be accurate for all material systems or operating

regimes.[9][10] Ensure you are correctly calculating the gate capacitance (C<sub>i</sub>) and accurately

determining the device dimensions (channel length L and width W).[11]

### **Data Summary**

The following tables summarize how ALD process parameters and post-processing can influence the properties of the AlO<sub>x</sub> film and, consequently, the carrier mobility of the device.

Table 1: Effect of ALD Parameters on AlO<sub>x</sub> Film Properties

| Parameter                 | Typical Range      | Effect on Film<br>Properties                                                                                               | Impact on Device<br>Mobility                                                                                                        |

|---------------------------|--------------------|----------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------|

| Deposition<br>Temperature | 150 - 300 °C       | Higher temperatures generally lead to denser films with lower hydrogen content but can affect the underlying material.[1]  | Can improve mobility<br>by reducing bulk<br>traps, but an optimal<br>temperature must be<br>found to preserve<br>interface quality. |

| Precursors (Oxidant)      | H₂O, O₃, O₂ plasma | O <sub>3</sub> and plasma-based processes can produce denser films at lower temperatures compared to H <sub>2</sub> O.[12] | Denser films with fewer impurities generally lead to higher mobility.                                                               |

| Film Thickness            | 5 - 30 nm          | Thicker films may have lower defect density in the bulk but can increase the risk of stress-related issues.[1]             | An optimal thickness provides good insulation without introducing excessive stress or degrading the interface.                      |

Table 2: Influence of Post-Deposition Annealing (PDA) on Device Performance

| PDA Parameter            | Typical Range                                                                      | Effect on<br>AIO <sub>×</sub> /Semiconduct<br>or Interface                                                                                                  | Impact on Device<br>Mobility                                                                   |

|--------------------------|------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------|

| Annealing<br>Temperature | 300 - 600 °C                                                                       | Reduces interface<br>trap density (Dit) and<br>can modulate fixed<br>charge (Qf). Can also<br>induce interfacial layer<br>growth (e.g., SiO <sub>2</sub> ). | Generally increases mobility by passivating interface traps, which reduces carrier scattering. |

| Annealing Ambient        | N <sub>2</sub> , O <sub>2</sub> , Forming Gas<br>(H <sub>2</sub> /N <sub>2</sub> ) | Forming gas is often effective at passivating dangling bonds at the interface.  O2 can help reduce oxygen vacancies.                                        | The optimal ambient depends on the semiconductor and the dominant type of interface defects.   |

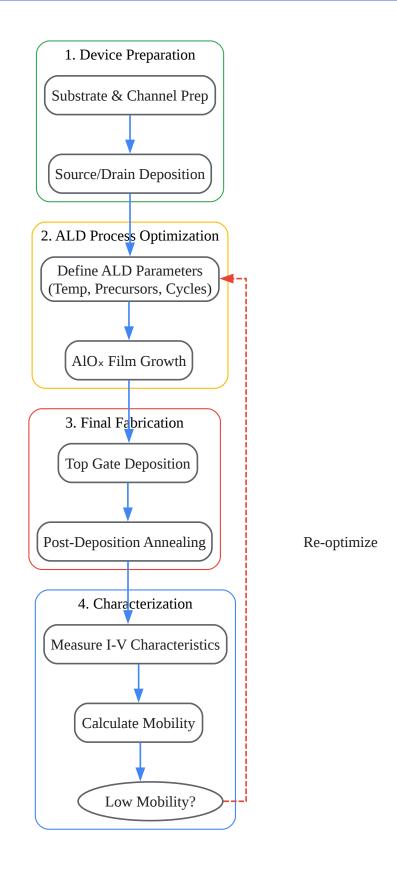

# **Experimental Protocols**

Protocol 1: Fabrication of a Top-Gated Field-Effect Transistor (FET) with ALD AlOx

This protocol outlines the key steps for creating a simple FET structure to test the performance of your ALD AlO $_{\times}$  as a gate dielectric.

- Substrate Preparation: Begin with a suitable substrate (e.g., Si/SiO<sub>2</sub>) on which the semiconductor channel material has been deposited or grown.

- Source/Drain Contact Definition:

- Use photolithography to define the source and drain regions.

- Deposit appropriate contact metals (e.g., Ti/Au, Ni/Au) using e-beam evaporation or sputtering.

- Perform a lift-off process to remove excess metal.

- Surface Preparation for ALD:

- Clean the surface of the semiconductor channel thoroughly to remove any organic residues or contaminants. A gentle O<sub>2</sub> plasma clean or solvent rinse (e.g., acetone, IPA) may be appropriate, depending on the channel material's stability.

- ALD of AlO<sub>x</sub> Dielectric:

- Transfer the substrate to the ALD chamber.

- Deposit the AlO<sub>x</sub> film using your optimized ALD recipe (e.g., using Trimethylaluminum (TMA) and H<sub>2</sub>O as precursors). A typical thickness for the gate dielectric is 10-20 nm.

- Gate Electrode Definition:

- Use photolithography to define the top gate electrode over the channel region.

- Deposit the gate metal (e.g., Al, Ti/Au).

- Perform a lift-off process.

- Post-Deposition Annealing (PDA):

- Anneal the completed device in a controlled environment (e.g., tube furnace) at the desired temperature and in the chosen ambient (e.g., 400 °C in N<sub>2</sub> for 30 minutes).

Protocol 2: Measurement and Calculation of Field-Effect Mobility (µFE)

- Electrical Characterization: Use a semiconductor parameter analyzer or a probe station connected to source-measure units.

- Measure Transfer Characteristics:

- Apply a small, constant drain-source voltage (Vds), typically 50-100 mV to operate in the linear regime.

- Sweep the gate-source voltage (Vgs) from negative to positive (or vice versa, depending on the transistor type) and measure the corresponding drain-source current (Ids).

- Calculate Field-Effect Mobility:

- The field-effect mobility in the linear regime can be calculated from the transconductance (g<sub>m</sub>), which is the slope of the Ids-Vgs curve.

- The formula is:  $\mu = [L/(W * C_i * Vds)] * g_m$

- L: Channel length

- W: Channel width

- C<sub>i</sub>: Gate capacitance per unit area. This can be calculated as  $\epsilon_0 \epsilon_r / t$ , where  $\epsilon_0$  is the permittivity of free space,  $\epsilon_r$  is the dielectric constant of AlO<sub>×</sub> (~8-9), and t is the thickness of the AlO<sub>×</sub> film.

- g<sub>m</sub>: The transconductance, calculated as d(lds)/d(Vgs) from the linear region of the transfer curve.[11]

#### **Visualizations**

Click to download full resolution via product page

Caption: Experimental workflow for optimizing ALD AlO<sub>x</sub> for high mobility.

Click to download full resolution via product page

#### **Need Custom Synthesis?**

BenchChem offers custom synthesis for rare earth carbides and specific isotopiclabeling.

Email: info@benchchem.com or Request Quote Online.

#### References

- 1. Atomic-Layer-Deposited Aluminum Oxide Thin Films Probed with X-ray Scattering and Compared to Molecular Dynamics and Density Functional Theory Models - PMC [pmc.ncbi.nlm.nih.gov]

- 2. arxiv.org [arxiv.org]

- 3. researchgate.net [researchgate.net]

- 4. pubs.acs.org [pubs.acs.org]

- 5. arxiv.org [arxiv.org]

- 6. pubs.aip.org [pubs.aip.org]

- 7. researchgate.net [researchgate.net]

- 8. researchgate.net [researchgate.net]

- 9. web.eecs.umich.edu [web.eecs.umich.edu]

- 10. On the methodology of the determination of charge concentration dependent mobility from organic field-effect transistor characteristics - Physical Chemistry Chemical Physics (RSC Publishing) [pubs.rsc.org]

- 11. rsc.org [rsc.org]

- 12. researchgate.net [researchgate.net]

- To cite this document: BenchChem. [Technical Support Center: Optimizing ALD-Grown AlOx Films for Enhanced Mobility]. BenchChem, [2025]. [Online PDF]. Available at: [https://www.benchchem.com/product/b15444497#optimizing-aluminum-concentration-in-ald-grown-aio-films-for-mobility]

#### **Disclaimer & Data Validity:**

The information provided in this document is for Research Use Only (RUO) and is strictly not intended for diagnostic or therapeutic procedures. While BenchChem strives to provide accurate protocols, we make no warranties, express or implied, regarding the fitness of this product for every specific experimental setup.

**Technical Support:** The protocols provided are for reference purposes. Unsure if this reagent suits your experiment? [Contact our Ph.D. Support Team for a compatibility check]

Need Industrial/Bulk Grade? Request Custom Synthesis Quote

# BenchChem

Our mission is to be the trusted global source of essential and advanced chemicals, empowering scientists and researchers to drive progress in science and industry.

#### Contact

Address: 3281 E Guasti Rd

Ontario, CA 91761, United States

Phone: (601) 213-4426

Email: info@benchchem.com