# Technical Support Center: Optimizing 2-Isopropyltetracene Thin Films

Author: BenchChem Technical Support Team. Date: December 2025

| Compound of Interest |                          |           |

|----------------------|--------------------------|-----------|

| Compound Name:       | 2-(Propan-2-YL)tetracene |           |

| Cat. No.:            | B15447862                | Get Quote |

This technical support center provides researchers, scientists, and drug development professionals with troubleshooting guides and frequently asked questions (FAQs) to address common challenges encountered when working to reduce charge carrier traps in 2-isopropyltetracene (TIPS-tetracene) thin films.

### Frequently Asked Questions (FAQs)

Q1: What are charge carrier traps in TIPS-tetracene thin films and why are they detrimental?

A1: Charge carrier traps are localized electronic states within the bandgap of the TIPS-tetracene semiconductor material. These states can capture and immobilize charge carriers (holes, in the case of p-type TIPS-tetracene), preventing them from contributing to the electrical current. The presence of traps leads to reduced charge carrier mobility, lower device performance, and potential device instability. Traps can originate from various sources, including structural defects, impurities, grain boundaries, and interface states between the semiconductor and the dielectric layer.

Q2: What are the most common methods to reduce charge carrier traps in TIPS-tetracene films?

A2: The most prevalent and effective techniques for reducing charge carrier traps in TIPStetracene thin films include:

- Solvent Vapor Annealing (SVA): Exposing the thin film to a solvent vapor atmosphere can induce molecular rearrangement and improve crystallinity, thereby reducing defects that act as traps.

- Thermal Annealing: Heating the thin film to a specific temperature below its melting point can provide the necessary energy for molecules to organize into a more ordered crystalline structure, which minimizes trap states.

- Polymer Blending: Incorporating an insulating polymer, such as polystyrene (PS), into the TIPS-tetracene solution can influence the crystallization process and passivate the semiconductor-dielectric interface, leading to a reduction in trap density.

Q3: How does the choice of solvent affect the quality of TIPS-tetracene films and the prevalence of charge traps?

A3: The choice of solvent is critical as it significantly influences the morphology and crystallinity of the resulting thin film. Solvents with higher boiling points, like toluene or trichlorobenzene, generally lead to slower solvent evaporation during deposition.[1] This slower process allows more time for the TIPS-tetracene molecules to self-organize into larger, more ordered crystalline domains, which in turn reduces the density of grain boundaries that can act as charge traps.[1][2][3] In contrast, highly volatile solvents can lead to rapid, less controlled crystallization, resulting in smaller grains and more defects.[1]

Q4: Can blending TIPS-tetracene with a polymer really improve performance?

A4: Yes, blending TIPS-tetracene with an insulating polymer like polystyrene (PS) or poly(triarylamine) (PTAA) has been shown to be an effective strategy.[4] The polymer can serve multiple purposes: it can act as a template to guide the crystallization of TIPS-tetracene, lead to vertical phase separation which is beneficial for charge transport, and passivate the dielectric interface to reduce interface traps. For instance, blending with PTAA has been shown to significantly increase charge carrier mobility.[4]

## **Troubleshooting Guide**

## Troubleshooting & Optimization

Check Availability & Pricing

| Issue                       | Potential Cause(s)                                                                                                         | Recommended Solution(s)                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|-----------------------------|----------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Low Charge Carrier Mobility | High density of charge carrier traps due to poor crystallinity, small grain size, or interface defects.                    | - Implement post-deposition annealing: Try thermal annealing at temperatures between 60°C and 150°C.[5] - Utilize solvent vapor annealing: Expose the film to a solvent vapor like toluene to improve molecular ordering.[6] - Optimize the solvent: Use a higher boiling point solvent such as toluene or trichlorobenzene for film deposition.[1][3] - Introduce a polymer binder: Blend TIPS-tetracene with polystyrene or PTAA to improve morphology and passivate the interface.[4]          |

| Non-uniform Film Coverage   | Improper deposition technique (spin coating or drop casting), incorrect solution concentration, or poor substrate wetting. | - Adjust spin coating parameters: Optimize the spin speed and duration. A two-step process with a lower initial speed can improve spreading Modify drop casting procedure: Ensure the substrate is level and consider heating the substrate to control solvent evaporation.[7][8] - Check solution concentration: A concentration of around 0.5 wt% is a good starting point for many solvents.[7] - Improve substrate surface energy: Treat the substrate with a self-assembled monolayer (e.g., |

|                                 |                                                                                                   | OTS) to promote uniform film formation.[9]                                                                                                                                                                                                                                                              |

|---------------------------------|---------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Film Cracking                   | Stress induced during solvent evaporation or rapid temperature changes during thermal annealing.  | - Slow down solvent evaporation: Use a solvent with a higher boiling point or partially cover the substrate during drying to create a solvent-rich atmosphere Optimize thermal annealing ramp rates: Use a slower heating and cooling rate to minimize thermal stress.                                  |

| High Off-Current in Transistors | Presence of mobile ions or a high density of deep trap states that contribute to leakage current. | - Ensure high purity of materials: Use purified TIPS-tetracene and high-purity solvents Thoroughly clean substrates: Employ a rigorous substrate cleaning procedure to remove ionic contaminants.  [7] - Apply annealing: Both thermal and solvent vapor annealing can help to reduce deep trap states. |

## **Quantitative Data on Trap Reduction Techniques**

The following tables summarize the impact of different processing parameters on the performance of TIPS-pentacene-based organic field-effect transistors (OFETs), a close analogue to TIPS-tetracene. Higher mobility is generally indicative of a lower charge carrier trap density.

Table 1: Effect of Annealing Temperature on OFET Mobility (TIPS-Pentacene in Toluene)

| Annealing Temperature (°C) | Average Mobility (cm²/Vs) |

|----------------------------|---------------------------|

| No Annealing               | 1.5 x 10 <sup>-3</sup>    |

| 120                        | $2.1 \times 10^{-3}$      |

| 150                        | 4.5 x 10 <sup>-3</sup>    |

Data adapted from Kadri et al., Materials Sciences and Applications, 2018.[5]

Table 2: Effect of Solvent Choice on OFET Mobility (TIPS-Pentacene/PTAA Blend)

| Solvent       | Boiling Point (°C) | Top-Gate Mobility (cm²/Vs) |

|---------------|--------------------|----------------------------|

| Chlorobenzene | 132                | Lower                      |

| Tetralin      | 207                | Up to 2.82                 |

Data adapted from Kim et al., J. Mater. Chem., 2012.[2][3]

## **Experimental Protocols**

#### **Protocol 1: Spin Coating of TIPS-Tetracene Thin Films**

- Solution Preparation: Prepare a 0.5 wt% solution of TIPS-tetracene in a high boiling point solvent (e.g., toluene, chlorobenzene). Ensure the solute is fully dissolved, which may require gentle heating and stirring.

- Substrate Cleaning: Thoroughly clean the substrate (e.g., Si/SiO<sub>2</sub>) by sonicating in a sequence of deionized water, acetone, and isopropanol for 10-15 minutes each. Dry the substrate with a stream of nitrogen gas.

- Surface Treatment (Optional but Recommended): To improve film quality, treat the substrate surface with an adhesion promoter like octadecyltrichlorosilane (OTS).

- Spin Coating:

- Place the substrate on the spin coater chuck and ensure it is centered.

- o Dispense a sufficient amount of the TIPS-tetracene solution to cover the substrate.

- Use a two-step spin coating process: a low speed (e.g., 500 rpm) for a few seconds to allow the solution to spread, followed by a higher speed (e.g., 1500-3000 rpm) for 30-60 seconds to achieve the desired thickness.

- Drying: Allow the film to dry on a hotplate at a moderate temperature (e.g., 60°C) to remove residual solvent.

#### **Protocol 2: Solvent Vapor Annealing (SVA)**

- Prepare the Annealing Chamber: Place a small vial containing the annealing solvent (e.g., toluene) inside a sealed container, such as a petri dish or a desiccator.

- Sample Placement: Place the substrate with the dried TIPS-tetracene film inside the chamber, ensuring it is not in direct contact with the liquid solvent.

- Annealing: Seal the chamber and leave the film exposed to the solvent vapor for a

predetermined time (e.g., 1-12 hours) at room temperature. The optimal time will depend on

the solvent and film thickness and should be determined experimentally.

- Drying: After annealing, remove the substrate from the chamber and allow any absorbed solvent to evaporate in a nitrogen-purged environment or on a hotplate at a low temperature.

### **Protocol 3: Thermal Annealing**

- Sample Placement: Place the substrate with the TIPS-tetracene film on a hotplate or in a vacuum oven.

- Heating: Ramp up the temperature to the desired annealing temperature (typically between 60°C and 150°C for TIPS-pentacene) at a controlled rate (e.g., 5-10°C/minute).[5]

- Annealing: Hold the sample at the set temperature for a specific duration (e.g., 10-30 minutes).

- Cooling: Slowly cool the sample back to room temperature at a controlled rate to prevent cracking.

### **Visualizations**

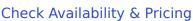

Click to download full resolution via product page

Caption: Experimental workflow for fabricating and optimizing TIPS-tetracene thin films.

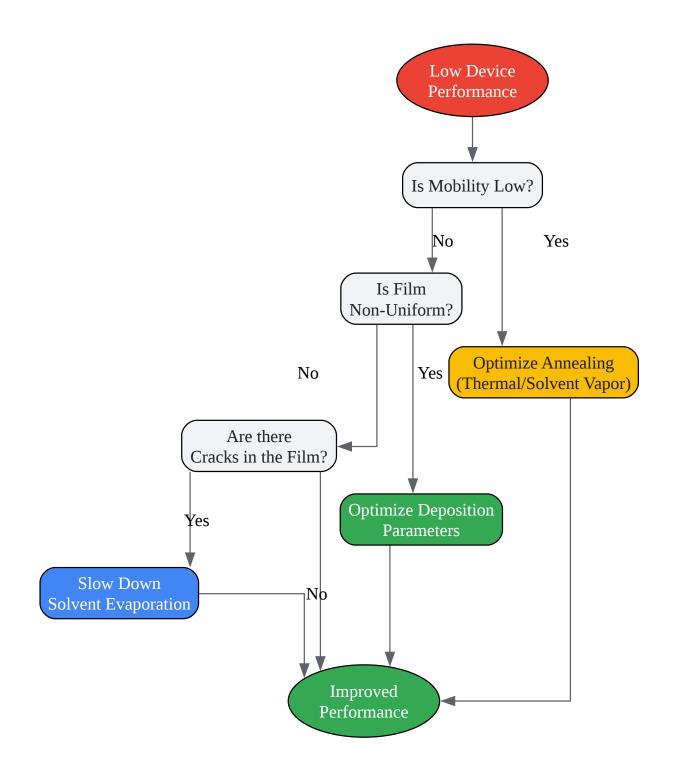

Click to download full resolution via product page

Caption: A logical troubleshooting flow for common issues in TIPS-tetracene film fabrication.

#### **Need Custom Synthesis?**

BenchChem offers custom synthesis for rare earth carbides and specific isotopiclabeling.

Email: info@benchchem.com or Request Quote Online.

#### References

- 1. repositorio.unesp.br [repositorio.unesp.br]

- 2. researchgate.net [researchgate.net]

- 3. Solvent and polymer matrix effects on TIPS-pentacene/polymer blend organic field-effect transistors Journal of Materials Chemistry (RSC Publishing) [pubs.rsc.org]

- 4. researchgate.net [researchgate.net]

- 5. researchgate.net [researchgate.net]

- 6. Grain Boundary Control of Organic Semiconductors via Solvent Vapor Annealing for High-Sensitivity NO2 Detection - PubMed [pubmed.ncbi.nlm.nih.gov]

- 7. journals.aps.org [journals.aps.org]

- 8. encyclopedia.pub [encyclopedia.pub]

- 9. mdpi.com [mdpi.com]

- To cite this document: BenchChem. [Technical Support Center: Optimizing 2-Isopropyltetracene Thin Films]. BenchChem, [2025]. [Online PDF]. Available at: [https://www.benchchem.com/product/b15447862#reducing-charge-carrier-traps-in-2-isopropyltetracene-thin-films]

#### **Disclaimer & Data Validity:**

The information provided in this document is for Research Use Only (RUO) and is strictly not intended for diagnostic or therapeutic procedures. While BenchChem strives to provide accurate protocols, we make no warranties, express or implied, regarding the fitness of this product for every specific experimental setup.

**Technical Support:**The protocols provided are for reference purposes. Unsure if this reagent suits your experiment? [Contact our Ph.D. Support Team for a compatibility check]

#### Need Industrial/Bulk Grade? Request Custom Synthesis Quote

## BenchChem

Our mission is to be the trusted global source of essential and advanced chemicals, empowering scientists and researchers to drive progress in science and industry. Contact

Address: 3281 E Guasti Rd

Ontario, CA 91761, United States

Phone: (601) 213-4426

Email: info@benchchem.com