# Technical Support Center: Optimizing 2,7-Dimethylphenazine-Based Electronic Devices

Author: BenchChem Technical Support Team. Date: December 2025

| Compound of Interest |                       |           |

|----------------------|-----------------------|-----------|

| Compound Name:       | 2,7-Dimethylphenazine |           |

| Cat. No.:            | B15491785             | Get Quote |

This technical support center provides researchers, scientists, and drug development professionals with a comprehensive resource for troubleshooting and optimizing the performance of electronic devices based on **2,7-Dimethylphenazine**.

# **Frequently Asked Questions (FAQs)**

Q1: What are the key electronic properties of **2,7-Dimethylphenazine**?

A1: **2,7-Dimethylphenazine** is an organic semiconductor. Its electronic properties, like those of other phenazine derivatives, are influenced by its molecular structure, which allows for charge transport. The addition of electron-donating methyl groups can influence the charge density on the phenazine core. The performance of devices using this material is highly dependent on factors such as the purity of the material, the morphology of the thin film, and the device architecture.

Q2: What are the common device architectures for **2,7-Dimethylphenazine**?

A2: **2,7-Dimethylphenazine** is typically used as the active channel material in an Organic Field-Effect Transistor (OFET). The most common OFET architectures are bottom-gate top-contact (BGTC) and bottom-gate bottom-contact (BGBC). The choice of architecture can impact device performance, with factors like contact resistance playing a significant role.

Q3: What are the primary methods for depositing **2,7-Dimethylphenazine** thin films?

A3: The two primary methods for depositing **2,7-Dimethylphenazine** thin films are vacuum thermal evaporation and solution processing. Vacuum deposition can offer high purity films with well-ordered molecular packing, while solution processing techniques like spin-coating or inkjet printing are often more cost-effective and suitable for large-area applications. The choice of deposition method significantly impacts the thin film's morphology and, consequently, the device's performance.

Q4: Why is the purity of 2,7-Dimethylphenazine important for device performance?

A4: Impurities in the **2,7-Dimethylphenazine** material can act as charge traps, hindering the movement of charge carriers within the semiconductor. This can lead to reduced charge carrier mobility and a lower on/off ratio in the final device. Therefore, purification of the material before device fabrication is a critical step.

Q5: What is the purpose of post-deposition annealing?

A5: Post-deposition annealing is a heat treatment process applied to the thin film after its deposition. This process can improve the crystallinity and molecular ordering within the film, leading to enhanced charge transport and overall better device performance. The optimal annealing temperature and duration need to be determined experimentally.[1][2]

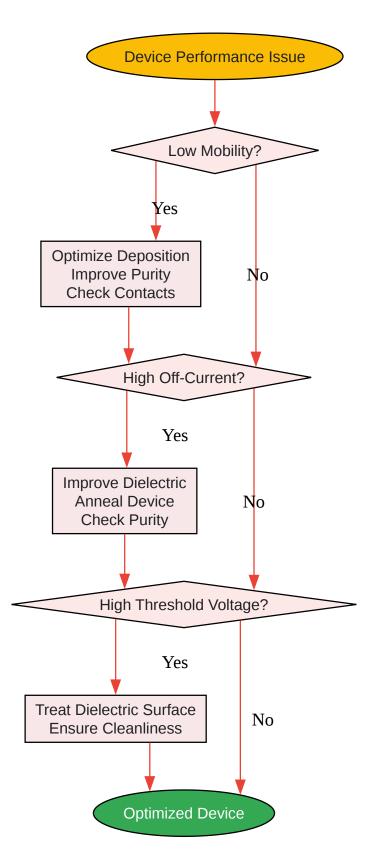

## **Troubleshooting Guide**

This guide addresses common issues encountered during the fabrication and characterization of **2,7-Dimethylphenazine**-based electronic devices.

# Troubleshooting & Optimization

Check Availability & Pricing

| Issue                                               | Possible Causes                                                                                                                                                                                      | Troubleshooting Steps                                                                                                                                                                                                                                                                                                                                                            |

|-----------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Low Charge Carrier Mobility                         | - Poor thin film morphology (amorphous or small grains)- Presence of impurities in the material- High contact resistance between the semiconductor and electrodes- Inappropriate device architecture | - Optimize deposition parameters (substrate temperature, deposition rate) to improve film crystallinity Purify the 2,7- Dimethylphenazine material before use Use a suitable contact metal with a work function that aligns with the energy levels of 2,7- Dimethylphenazine Consider a different device architecture (e.g., top-gate) to potentially reduce contact resistance. |

| High Off-State Current (Low<br>On/Off Ratio)        | - Presence of charge traps or<br>defects in the semiconductor<br>or at the dielectric interface-<br>Gate leakage current-<br>Impurities in the active layer                                          | - Anneal the device after fabrication to reduce traps Ensure a high-quality gate dielectric with low leakage Verify the purity of the 2,7- Dimethylphenazine source material.                                                                                                                                                                                                    |

| High Threshold Voltage                              | - Trapped charges at the semiconductor-dielectric interface- Surface contamination of the dielectric layer- Mismatch in energy levels between the semiconductor and the dielectric                   | - Treat the dielectric surface (e.g., with a self-assembled monolayer) to reduce trap states Ensure a clean fabrication environment to prevent contamination Select a gate dielectric with appropriate surface energy.                                                                                                                                                           |

| Device Instability (Performance degrades over time) | - Degradation of the organic<br>material due to exposure to air,<br>moisture, or light-<br>Electromigration or diffusion of<br>electrode material into the                                           | - Encapsulate the device to protect it from the ambient environment Use a buffer layer between the electrode and the organic                                                                                                                                                                                                                                                     |

|                                            | organic layer- Trapping of charges over time                                                                                     | semiconductor Perform<br>measurements in an inert<br>atmosphere (e.g., a glovebox).                                                                                                                                |

|--------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Poor Film Quality (e.g., cracks, pinholes) | - Inappropriate solvent for solution processing- Incorrect substrate temperature during vacuum deposition-Contaminated substrate | - Screen different solvents to find one that provides uniform film formation Optimize the substrate temperature to control the nucleation and growth of the film Thoroughly clean the substrate before deposition. |

# **Experimental Protocols**Purification of 2,7-Dimethylphenazine

Objective: To remove impurities that can act as charge traps and degrade device performance.

Methodology: Gradient Sublimation

- Place the crude **2,7-Dimethylphenazine** powder in a sublimation tube.

- Evacuate the tube to a high vacuum (e.g., < 10-5 Torr).</li>

- Establish a temperature gradient along the tube using a tube furnace. The temperature at the source end should be high enough to sublime the material, while the temperature should gradually decrease towards the other end.

- Heat the source end of the tube. **2,7-Dimethylphenazine** will sublime and then re-deposit in a purer crystalline form at a cooler zone of the tube, leaving less volatile impurities behind.

- Carefully collect the purified crystals in an inert atmosphere.

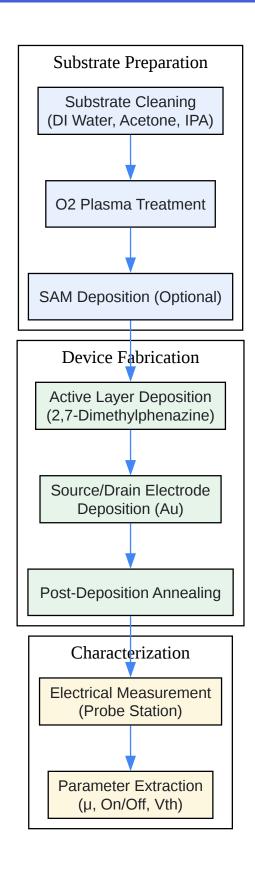

## Fabrication of a Bottom-Gate, Top-Contact (BGTC) OFET

Objective: To fabricate a standard transistor structure for electrical characterization of **2,7- Dimethylphenazine**.

#### Methodology:

- Substrate Cleaning:

- Start with a heavily n-doped silicon wafer with a thermally grown silicon dioxide (SiO<sub>2</sub>)

layer (e.g., 300 nm) which will act as the gate electrode and gate dielectric, respectively.

- Sonnicate the substrate sequentially in deionized water, acetone, and isopropanol for 15 minutes each.

- Dry the substrate with a stream of nitrogen gas.

- Treat the SiO<sub>2</sub> surface with an oxygen plasma or a piranha solution to create a hydrophilic surface.

- Dielectric Surface Modification (Optional but Recommended):

- To improve the interface quality, treat the SiO<sub>2</sub> surface with a self-assembled monolayer (SAM) such as octadecyltrichlorosilane (OTS). This can be done by immersing the substrate in a dilute solution of OTS in an anhydrous solvent (e.g., toluene) for a specified time, followed by rinsing and annealing.

- Active Layer Deposition (Vacuum Thermal Evaporation):

- Place the purified **2,7-Dimethylphenazine** in a quartz crucible in a thermal evaporator.

- Mount the prepared substrate above the crucible.

- Evacuate the chamber to a high vacuum (e.g., < 10-6 Torr).</li>

- Heat the crucible to sublime the 2,7-Dimethylphenazine.

- Deposit a thin film (e.g., 50 nm) of the material onto the substrate at a controlled deposition rate (e.g., 0.1-0.5 Å/s). The substrate temperature can be controlled to influence film morphology.

- Source and Drain Electrode Deposition:

- Use a shadow mask to define the source and drain electrodes.

- Deposit a suitable metal (e.g., gold) with good work function matching for hole injection into 2,7-Dimethylphenazine. A thin adhesion layer (e.g., chromium or titanium) may be used. The typical thickness of the electrodes is 50-100 nm.

- Post-Deposition Annealing:

- Anneal the completed device in an inert atmosphere (e.g., in a glovebox or a nitrogenfilled oven) at a temperature below the material's melting point (e.g., 100-150 °C) for a specific duration (e.g., 30-60 minutes) to improve film crystallinity.

#### **Electrical Characterization**

Objective: To measure the key performance metrics of the fabricated OFET.

#### Methodology:

- Use a semiconductor parameter analyzer and a probe station in an inert and dark environment.

- Output Characteristics (ID vs. VD):

- Apply a constant gate-source voltage (VG).

- Sweep the drain-source voltage (VD) from 0 V to a negative voltage (for a p-type semiconductor) and measure the drain current (ID).

- Repeat for several different VG values.

- Transfer Characteristics (ID vs. VG):

- Apply a constant, high drain-source voltage (VD) to operate in the saturation regime.

- Sweep the gate-source voltage (VG) from a positive to a negative voltage and measure the drain current (ID).

- Parameter Extraction:

- Field-Effect Mobility (μ): Calculated from the slope of the (ID)1/2 vs. VG plot in the saturation regime.

- On/Off Ratio: The ratio of the maximum drain current (Ion) to the minimum drain current (Ioff).

- Threshold Voltage (Vth): The x-intercept of the linear fit to the (ID)1/2 vs. VG plot.

## **Performance Data**

The following table summarizes typical performance parameters for phenazine-based OFETs. Note that specific values for **2,7-Dimethylphenazine** can vary significantly based on the experimental conditions.

| Parameter                 | Typical Range for Phenazine<br>Derivatives | Factors Influencing Performance                                                                                                |

|---------------------------|--------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------|

| Field-Effect Mobility (µ) | 10-3 - 1 cm2/Vs                            | - Crystalline order and grain size of the thin film- Purity of the material- Quality of the semiconductor-dielectric interface |

| On/Off Ratio              | 104 - 107                                  | - Gate leakage current-<br>Presence of trap states-<br>Doping level of the<br>semiconductor                                    |

| Threshold Voltage (Vth)   | 0 to -40 V                                 | - Work function of the gate<br>electrode- Fixed charges in the<br>dielectric- Interface trap<br>density                        |

# **Visualizations**

Click to download full resolution via product page

Caption: Experimental workflow for fabricating and characterizing **2,7-Dimethylphenazine** OFETs.

Check Availability & Pricing

Click to download full resolution via product page

Caption: Logical flowchart for troubleshooting common OFET performance issues.

#### **Need Custom Synthesis?**

BenchChem offers custom synthesis for rare earth carbides and specific isotopiclabeling.

Email: info@benchchem.com or Request Quote Online.

### References

- 1. mdpi.com [mdpi.com]

- 2. mdpi.com [mdpi.com]

- To cite this document: BenchChem. [Technical Support Center: Optimizing 2,7-Dimethylphenazine-Based Electronic Devices]. BenchChem, [2025]. [Online PDF]. Available at: [https://www.benchchem.com/product/b15491785#optimizing-the-performance-of-2-7-dimethylphenazine-based-electronic-devices]

#### **Disclaimer & Data Validity:**

The information provided in this document is for Research Use Only (RUO) and is strictly not intended for diagnostic or therapeutic procedures. While BenchChem strives to provide accurate protocols, we make no warranties, express or implied, regarding the fitness of this product for every specific experimental setup.

**Technical Support:** The protocols provided are for reference purposes. Unsure if this reagent suits your experiment? [Contact our Ph.D. Support Team for a compatibility check]

Need Industrial/Bulk Grade? Request Custom Synthesis Quote

# BenchChem

Our mission is to be the trusted global source of essential and advanced chemicals, empowering scientists and researchers to drive progress in science and industry. Contact

Address: 3281 E Guasti Rd

Ontario, CA 91761, United States

Phone: (601) 213-4426

Email: info@benchchem.com