# **Technical Support Center: Optimization of Tellurium Doping in Semiconductors**

Author: BenchChem Technical Support Team. Date: December 2025

| Compound of Interest |           |           |

|----------------------|-----------|-----------|

| Compound Name:       | Tellurium |           |

| Cat. No.:            | B081085   | Get Quote |

This technical support center provides troubleshooting guidance and frequently asked questions (FAQs) for researchers, scientists, and drug development professionals working with **tellurium** doping in semiconductors. The information is presented in a guestion-and-answer format to directly address specific issues encountered during experimental procedures.

### Frequently Asked Questions (FAQs)

Q1: What are the primary advantages of using **tellurium** as an n-type dopant in III-V semiconductors compared to other dopants like silicon?

A1: **Tellurium** (Te), a group VI element, is a preferred n-type dopant in many III-V compound semiconductors for several reasons. Unlike group IV dopants such as silicon (Si) which are amphoteric, **tellurium** is not, meaning it doesn't self-compensate by occupying acceptor sites at high concentrations.[1][2] This allows for achieving higher maximum carrier concentrations. For instance, in Gallium Arsenide (GaAs), the maximum electron concentration in Te-doped samples is higher than in Si-doped ones, often exceeding 1x10<sup>19</sup> cm<sup>-3</sup>.[3] Additionally, tellurium exhibits a low diffusion coefficient in GaAs, which is crucial for creating abrupt doping profiles and interfaces, a significant factor in the fabrication of devices like tunnel junctions.[4] [5]

Q2: What is the "memory effect" in the context of tellurium doping and how can it be mitigated?

#### Troubleshooting & Optimization

A2: The "memory effect" refers to the continued incorporation of the dopant into subsequent layers even after the dopant source has been turned off.[1][6] This is attributed to the accumulation of **tellurium** on the growth surface, which then gets incorporated into the following layers.[1] This effect can be particularly problematic when growing structures with abrupt changes in doping concentration, such as an undoped cap layer on a doped layer.[1] To combat the memory effect, potential strategies include pulsing the dopant precursor before the growth of the intentionally doped layer for a sharp turn-on, or introducing a post-growth bake step after the doped layer to sublimate any residual **tellurium** precursor products from the wafer surface.[2]

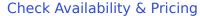

Q3: What is surface segregation of **tellurium** and how does it impact the doping process?

A3: Surface segregation is a phenomenon where **tellurium** atoms tend to accumulate on the surface of the growing crystal rather than being incorporated into the bulk material.[1][7] This behavior is driven by the volatile nature of **tellurium** and its tendency to act as a surfactant.[1] [2] High growth temperatures can exacerbate this issue, as **tellurium** is more likely to evaporate or remain on the surface instead of incorporating.[1][2] Surface segregation can lead to non-uniform doping profiles and can negatively impact the performance of subsequently grown layers.[5][8] For instance, in Molecular Beam Epitaxy (MBE) grown InGaP, significant surface segregation was observed at a growth temperature of 460 °C.[7]

#### **Troubleshooting Guides**

Problem 1: Low activation efficiency of **tellurium** dopants.

- Symptom: Hall measurements show a significantly lower active electron density compared to the **tellurium** concentration measured by Secondary Ion Mass Spectrometry (SIMS).

- Possible Cause 1: Unfavorable growth conditions. The V/III ratio can significantly impact the incorporation and activation of tellurium.

- Solution 1: Optimize the V/III ratio. For example, in InGaAs growth, reducing the V/III ratio from 44 to 22 was shown to increase the activation efficiency from 19.6% to 59.6%.[1][2]

This is because a lower V/III ratio facilitates the substitution of arsenic with tellurium in the crystal lattice.[1][2]

#### Troubleshooting & Optimization

- Possible Cause 2: High growth temperature. At elevated temperatures, **tellurium** tends to evaporate from the surface rather than being incorporated into the crystal.[1][2]

- Solution 2: Lower the growth temperature. However, this needs to be balanced with the

requirement for good crystal quality. The optimal temperature will depend on the specific

material system. For instance, in Te-doped GaAs grown by MOVPE, a low temperature of

560 °C was used for high Te incorporation.[8]

Problem 2: Difficulty in achieving high carrier concentrations.

- Symptom: The active electron density saturates and may even decrease with increasing tellurium precursor flow.

- Possible Cause: Dopant deactivation at high concentrations. At very high doping levels, Teinduced defects can form, which may lead to a reduction in carrier concentration.[9] For

instance, in InGaAs, increasing the diethyl-telluride (DETe) flow by 50 times only increased

the dopant level by a factor of 1.7 and reduced the activation efficiency from 60.3% to 23%,

resulting in a lower active electron density.[1][2]

- Solution: Carefully control the dopant precursor flow rate to stay below the saturation point.

Characterize the relationship between precursor flow and active carrier concentration for your specific material and growth conditions to identify the optimal doping window.

Problem 3: Non-uniform doping profile and graded interfaces.

- Symptom: SIMS analysis reveals a gradual change in **tellurium** concentration at the intended interface instead of an abrupt profile.

- Possible Cause: The "memory effect" and surface segregation of tellurium.[1][5]

- Solution: As mentioned in the FAQ, employ techniques like pre-growth dopant pulsing or post-growth baking to mitigate the memory effect.[2] Additionally, optimizing growth temperature and V/III ratio can help control surface segregation. In some cases, using a different tellurium precursor might be beneficial. For instance, SnTe has been used as a tellurium source for GaSb growth in MBE, offering good control over the doping concentration.[10]

Problem 4: Poor surface morphology of the grown film.

- Symptom: Atomic Force Microscopy (AFM) reveals a rough surface on the tellurium-doped layer.

- Possible Cause: While **tellurium** can act as a surfactant and improve surface morphology in some cases, improper doping conditions can lead to surface roughening.[1]

- Solution: Optimize growth parameters. Interestingly, the surfactant properties of **tellurium** in InGaAs growth at 600°C were found to reduce the root-mean-square surface roughness from 3.6 nm for undoped material to 0.4 nm for heavily Te-doped material.[1] This suggests that leveraging the surfactant effect through careful control of doping levels and growth temperature can be beneficial.

## **Quantitative Data**

Table 1: Influence of DETe Flow and V/III Ratio on Te-doped Ino.53Gao.47As on InP at 660°C[2]

| DETe<br>Flow<br>(µmol/mi<br>n) | V/III Ratio | Sheet<br>Resistanc<br>e<br>(Ω/square<br>) | Mobility<br>(cm²/V·s) | Active<br>Electron<br>Density<br>(10 <sup>19</sup><br>cm <sup>-3</sup> ) | Tellurium<br>Concentr<br>ation<br>(10 <sup>19</sup><br>cm <sup>-3</sup> ) | Activatio<br>n<br>Efficiency<br>(%) |

|--------------------------------|-------------|-------------------------------------------|-----------------------|--------------------------------------------------------------------------|---------------------------------------------------------------------------|-------------------------------------|

| 0.024                          | 44          | 13.6                                      | 1310                  | 3.5                                                                      | 5.8                                                                       | 60.3                                |

| 0.13                           | 44          | 43.5                                      | 1100                  | 1.3                                                                      | 6.6                                                                       | 19.6                                |

| 0.13                           | 22          | 13.8                                      | 1320                  | 3.4                                                                      | 5.7                                                                       | 59.6                                |

| 1.2                            | 44          | 24.4                                      | 1110                  | 2.3                                                                      | 10                                                                        | 23.0                                |

Table 2: Hall Data for as-grown and annealed GaAs:Te layers[8]

| Condition                | Free Electron<br>Concentration nH (cm <sup>-3</sup> ) | Hall Mobility μH (cm²/V·s)                 |  |  |

|--------------------------|-------------------------------------------------------|--------------------------------------------|--|--|

| As-grown                 | Varies with Te concentration                          | Decreases from 1600 to 500 as nH increases |  |  |

| Annealed (740°C, 30 min) | Shows a decrease compared to as-grown samples         | Generally lower than as-grown samples      |  |  |

## **Experimental Protocols**

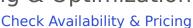

1. Metal-Organic Chemical Vapor Deposition (MOCVD) of Te-doped InGaAs

This protocol is based on the methodology described for growing Te-doped In<sub>0.53</sub>Ga<sub>0.47</sub>As.[1][2]

- System: Aixtron CRIUS-R 300mm system.[2]

- Substrates: 3-inch Indium Phosphide (InP) and 300mm Silicon (Si) (100) wafers.[2]

- · Precursors:

- Trimethyl-gallium (TMGa)

- Trimethyl-indium (TMIn)

- Arsine (AsH<sub>3</sub>)

- Diethyl-telluride (DETe) as the n-type dopant source.[1][2]

- Carrier Gas: Palladium-purified hydrogen.[1][2]

- Growth Temperature: Ranged from 500°C to 660°C.[1]

- V/III Ratio: Varied, with values of 22 and 44 being reported.[1][2]

- Procedure:

- Load the substrates into the MOCVD reactor.

- For growth on Si, deposit an InP/GaAs buffer layer to bridge the lattice mismatch.[1][2]

- Heat the substrates to the desired growth temperature under a stable flow of the carrier gas and arsine.

- Introduce TMGa, TMIn, and DETe into the reactor to initiate the growth of the Te-doped InGaAs layer. The flow rates of the precursors are controlled to achieve the desired composition and doping concentration.

- After the desired thickness is achieved, stop the flow of the metal-organic precursors and the dopant source.

- Cool down the reactor under an arsine overpressure to prevent surface degradation.

- Characterization:

- Secondary Ion Mass Spectrometry (SIMS): To determine the tellurium concentration and doping profile.[1]

- Hall Measurements: To determine the active electron density, mobility, and sheet resistance.[1][2]

- Atomic Force Microscopy (AFM): To characterize the surface morphology and roughness.

[1]

- 2. Characterization of Te-doped Semiconductors

A variety of techniques are essential to characterize the properties of **tellurium**-doped semiconductors:

- Electrical Characterization:

- Hall Effect Measurements: Used to determine the carrier concentration (active dopant concentration), mobility, and resistivity of the doped layer.[8][11]

- Electrochemical CV Profiling (ECV): Can be used to measure the doping profile.

- Structural and Compositional Characterization:

#### Troubleshooting & Optimization

- Secondary Ion Mass Spectrometry (SIMS): A highly sensitive technique to measure the total concentration of **tellurium** atoms and their depth distribution within the semiconductor.[8]

- X-ray Diffraction (XRD): To assess the crystal quality and determine the lattice parameters,

which can be affected by the incorporation of large tellurium atoms.[12]

- Transmission Electron Microscopy (TEM): To investigate the microstructure and identify any defects or precipitates that may form at high doping concentrations.[11]

- Surface Morphology Characterization:

- Atomic Force Microscopy (AFM): Provides high-resolution images of the surface topography, allowing for the quantification of surface roughness.[1]

- Scanning Electron Microscopy (SEM): Used to observe the surface morphology and any larger-scale features.[12]

- Optical Characterization:

- Photoluminescence (PL): Can provide information about the material quality and the electronic band structure, which can be influenced by heavy doping.

#### **Visualizations**

Click to download full resolution via product page

Caption: MOCVD experimental workflow for Te-doping.

Click to download full resolution via product page

Caption: The process of **tellurium** surface segregation.

Click to download full resolution via product page

Caption: Logical workflow for doping optimization.

#### **Need Custom Synthesis?**

BenchChem offers custom synthesis for rare earth carbides and specific isotopiclabeling.

Email: info@benchchem.com or Request Quote Online.

#### References

- 1. semiconductor-today.com [semiconductor-today.com]

- 2. Tellurium doping for n-type indium gallium arsenide [semiconductor-today.com]

- 3. pubs.aip.org [pubs.aip.org]

- 4. pdfs.semanticscholar.org [pdfs.semanticscholar.org]

- 5. researchgate.net [researchgate.net]

- 6. researchgate.net [researchgate.net]

- 7. Improved InGaP solar cells grown by molecular beam epitaxy by use of tellurium doping | IDEALS [ideals.illinois.edu]

- 8. fbh-berlin.de [fbh-berlin.de]

- 9. A study of dopant incorporation in Te-doped GaAsSb nanowires using a combination of XPS/UPS, and C-AFM/SKPM PMC [pmc.ncbi.nlm.nih.gov]

- 10. Tellurium doping study of GaSb grown by molecular beam epitaxy using SnTe | CoLab [colab.ws]

- 11. researchgate.net [researchgate.net]

- 12. iasj.rdd.edu.iq [iasj.rdd.edu.iq]

- To cite this document: BenchChem. [Technical Support Center: Optimization of Tellurium Doping in Semiconductors]. BenchChem, [2025]. [Online PDF]. Available at: [https://www.benchchem.com/product/b081085#optimization-of-tellurium-doping-concentration-in-semiconductors]

#### **Disclaimer & Data Validity:**

The information provided in this document is for Research Use Only (RUO) and is strictly not intended for diagnostic or therapeutic procedures. While BenchChem strives to provide accurate protocols, we make no warranties, express or implied, regarding the fitness of this product for every specific experimental setup.

**Technical Support:**The protocols provided are for reference purposes. Unsure if this reagent suits your experiment? [Contact our Ph.D. Support Team for a compatibility check]

Need Industrial/Bulk Grade? Request Custom Synthesis Quote

# BenchChem

Our mission is to be the trusted global source of essential and advanced chemicals, empowering scientists and researchers to drive progress in science and industry.

#### Contact

Address: 3281 E Guasti Rd

Ontario, CA 91761, United States

Phone: (601) 213-4426

Email: info@benchchem.com