# Technical Support Center: Mitigating Interface Defects in HfO<sub>2</sub>/Si Structures

Author: BenchChem Technical Support Team. Date: December 2025

| Compound of Interest |               |           |  |  |

|----------------------|---------------|-----------|--|--|

| Compound Name:       | Hafnium oxide |           |  |  |

| Cat. No.:            | B213204       | Get Quote |  |  |

This technical support center provides troubleshooting guidance and answers to frequently asked questions for researchers and scientists working with **hafnium oxide** (HfO<sub>2</sub>) on silicon (Si) substrates. The information is designed to help address specific issues encountered during experimental work.

# **Troubleshooting Guides**

This section addresses common problems encountered during the fabrication and characterization of HfO<sub>2</sub>/Si stacks.

# Question: I am observing a high interface trap density (Dit) after depositing HfO<sub>2</sub> on my silicon substrate. What are the potential causes and how can I reduce it?

### Answer:

A high interface trap density (Dit) is a common issue that degrades device performance. The primary causes are typically related to the quality of the Si surface before deposition, the deposition process itself, and post-deposition processing.

#### Potential Causes:

Inadequate Surface Preparation: Residual organic contaminants or an unstable native oxide on the silicon surface can introduce a high number of defects.

# Troubleshooting & Optimization

- Sub-optimal Deposition: Certain deposition techniques, like sputtering, can cause surface damage.[1] The choice of precursors and deposition temperature in Atomic Layer Deposition (ALD) can also affect interface quality.

- Lack of Passivation: Dangling bonds (like P-like centers) at the Si surface are a major source of interface traps if not properly passivated.[2]

- Crystallization of HfO<sub>2</sub>: While annealing is necessary, crystallization of the HfO<sub>2</sub> film can introduce stress and create defect states at the grain boundaries and the interface.[3]

## **Troubleshooting Steps:**

- Optimize Si Surface Cleaning: Implement a standard pre-deposition cleaning sequence (e.g., RCA clean) to remove contaminants. A final dip in dilute hydrofluoric (HF) acid can produce a hydrogen-terminated surface, which is stable for a short period before loading into the deposition chamber.[4]

- Introduce an Interfacial Layer: Intentionally growing a thin, high-quality silicon dioxide (SiO<sub>2</sub>) or silicon nitride (SiN) layer before HfO<sub>2</sub> deposition can significantly reduce interface traps.[5] An in-situ formed hydrophilic SiO<sub>2</sub> layer in an ALD chamber has also shown to produce high-quality interfaces.[6]

- Implement Post-Deposition Annealing (PDA): Annealing is crucial for reducing defect density. Annealing in a forming gas (a mixture of N<sub>2</sub> and H<sub>2</sub>) is effective for passivating dangling bonds with hydrogen.[1][7] Nitrogen anneals can also be effective and help to incorporate nitrogen, which can suppress boron diffusion and improve thermal stability.[8]

- Control Annealing Temperature: The annealing temperature must be carefully chosen. While

higher temperatures can improve film density, they can also promote the growth of an

unwanted low-k interfacial SiO<sub>2</sub> layer and lead to crystallization.[9][10] Annealing at

temperatures between 400°C and 600°C is often a good starting point.[11][12]

# Question: My measured dielectric constant (k-value) for the HfO<sub>2</sub> film is much lower than expected. Why is this happening?

# Troubleshooting & Optimization

## Answer:

A lower-than-expected dielectric constant for the  $HfO_2$  stack is almost always due to the presence of an unintentional interfacial layer with a lower k-value, typically silicon dioxide (k  $\approx$  3.9).

#### Potential Causes:

- Interfacial SiO<sub>2</sub> Growth: During deposition or subsequent high-temperature annealing, oxygen can diffuse to the Si interface and form a SiO<sub>2</sub> layer.[10] This layer, being in series with the HfO<sub>2</sub>, lowers the total capacitance and thus the effective k-value of the stack.

- Film Contamination: Precursors used in deposition (especially in ALD or CVD) can leave behind carbon or hydrogen residues if the reactions are incomplete, lowering the film's dielectric performance.[13]

- Amorphous vs. Crystalline Phase: The dielectric constant of HfO<sub>2</sub> is dependent on its crystal phase. The amorphous phase generally has a lower k-value (around 16-20) than crystalline phases like monoclinic or orthorhombic (which can be over 25).[10][14]

### **Troubleshooting Steps:**

- Minimize Interfacial Layer Growth: Use deposition techniques that are less prone to oxidizing the silicon, such as ALD at moderate temperatures. Some researchers use an "oxygen scavenging" method, where a metal layer like titanium is deposited and annealed to pull oxygen from the interfacial SiO<sub>2</sub>, effectively thinning it.[15][16]

- Optimize Annealing Conditions: Perform annealing in an oxygen-deficient atmosphere like N<sub>2</sub> or a vacuum to limit further SiO<sub>2</sub> growth.[11] Rapid Thermal Annealing (RTA) is preferred over furnace annealing as it minimizes the thermal budget.[10]

- Verify Film Purity: Use high-purity precursors and optimize deposition parameters (temperature, pulse times in ALD) to ensure complete chemical reactions and minimize impurities.

- Control Crystallization: If a higher k-value is desired, anneal at temperatures sufficient to induce crystallization (typically >500°C).[10] However, be aware of the trade-off with

increased leakage current through grain boundaries.

# Question: I'm observing high gate leakage current in my HfO<sub>2</sub>-based MOS capacitor. What are the likely sources and mitigation strategies?

#### Answer:

High leakage current is a critical issue that can compromise device functionality. It can originate from defects within the bulk HfO<sub>2</sub> or at the interface.

#### Potential Causes:

- Oxygen Vacancies: Oxygen vacancies are common intrinsic defects in HfO<sub>2</sub> that can act as charge traps and facilitate trap-assisted tunneling, a major leakage mechanism.[17][18][19]

- Grain Boundaries: When the HfO<sub>2</sub> film crystallizes during annealing, grain boundaries can form. These boundaries act as high-leakage paths through the dielectric.[3]

- Thin Interfacial Layer: While a thin interfacial layer is good for a high k-value, an overly thin or poor-quality layer may not be sufficient to prevent direct tunneling of charge carriers.

- Hf-Si Bonds: The formation of metallic hafnium-silicide bonds at the interface can also create states in the silicon bandgap, leading to increased leakage.[17]

### Troubleshooting Steps:

- Passivate Oxygen Vacancies: Annealing in a mildly oxidizing ambient or N<sub>2</sub> can help fill some oxygen vacancies, though this must be balanced against unwanted interfacial layer growth.

- Control Crystallinity: For applications where leakage is more critical than the absolute highest k-value, it may be beneficial to keep the HfO<sub>2</sub> film amorphous by using lower annealing temperatures (<500°C).[10] Incorporating elements like Al or N can increase the crystallization temperature.[4]

- Optimize the Interfacial Layer: A high-quality, intentionally grown SiO<sub>2</sub> or SiN layer of ~1 nm can serve as an effective barrier to leakage without excessively compromising the overall

capacitance.[5]

Use Forming Gas Anneal: A post-metallization anneal in forming gas at around 400-450°C

can passivate interface states that contribute to leakage.[3][9]

# Frequently Asked Questions (FAQs)

- Q1: What are the most common types of defects at the HfO2/Si interface?

- The most common defects include silicon dangling bonds (P-like centers), similar to those at the SiO<sub>2</sub>/Si interface, and oxygen vacancies within the HfO<sub>2</sub> near the interface.[2][17]

Other defects can include Hf-Si bonds and impurities from deposition precursors.[19]

- Q2: Why is a thin SiO<sub>2</sub> interfacial layer often intentionally used?

- A high-quality SiO<sub>2</sub> layer provides a much better electrical interface with silicon than HfO<sub>2</sub> does directly, resulting in a significantly lower interface trap density (D<sub>it</sub>).[5] It also improves channel mobility in transistors. This creates a trade-off between achieving a low D<sub>it</sub> and obtaining the highest possible equivalent oxide thickness (EOT) scaling.[15]

- Q3: What is the main purpose of Post-Deposition Annealing (PDA)?

- PDA serves several purposes: it densifies the HfO<sub>2</sub> film, removes residual impurities from

the deposition process, repairs defects like oxygen vacancies, and passivates interface

states.[13][20] The choice of temperature and atmosphere determines the final properties

of the film and interface.[9][11]

- Q4: How does the deposition method affect interface quality?

- Atomic Layer Deposition (ALD) is generally preferred for HfO<sub>2</sub> on Si because it offers excellent film uniformity, precise thickness control, and lower deposition temperatures, which help minimize initial interfacial SiO<sub>2</sub> growth and surface damage.[7][12] Sputtering methods can create more surface defects due to ion bombardment.[13]

- Q5: What is the role of the annealing atmosphere (e.g., N<sub>2</sub>, O<sub>2</sub>, Forming Gas)?

- N<sub>2</sub>: Provides an inert environment that allows for film densification and crystallization without significant further oxidation of the Si interface.[10][11]

- O<sub>2</sub>: Can be used to reduce oxygen vacancies within the HfO<sub>2</sub> but will also cause significant growth of the interfacial SiO<sub>2</sub> layer.[21]

- Forming Gas (N<sub>2</sub>/H<sub>2</sub>): Very effective at passivating Si dangling bonds at the interface by bonding hydrogen to them, which reduces D<sub>it</sub>.[3][9] This is often performed at lower temperatures (400-450°C) after gate metallization.

# **Quantitative Data Summary**

The following tables summarize key quantitative data from various experimental studies.

Table 1: Impact of Annealing Conditions on HfO2/Si Interface Properties

| Annealing<br>Temp. (°C) | Atmospher<br>e          | Film<br>Thickness<br>(nm) | Resulting Dit (cm <sup>-2</sup> eV <sup>-1</sup> ) | Key Finding                                                                       | Citation(s) |

|-------------------------|-------------------------|---------------------------|----------------------------------------------------|-----------------------------------------------------------------------------------|-------------|

| 400                     | N <sub>2</sub> / 10 min | ~8                        | Decreases<br>after anneal                          | Annealing improves passivation quality.                                           | [12]        |

| 350                     | Forming Gas             | 15                        | 3.6 x 10 <sup>10</sup>                             | Activates surface passivation, yielding very low Dit.                             | [3]         |

| 475                     | Air / 30 min            | 12                        | Not specified                                      | Found to be the most effective condition for activating passivation in one study. | [20]        |

| 500 - 900               | Ar                      | Not specified             | Not specified                                      | Higher temperatures lead to increased hafnium silicate and silicide formation.    | [8]         |

| 800 | N2 or O2    | Not specified | Not specified | High- temperature anneals cause significant growth of the interfacial layer.   | [9]  |

|-----|-------------|---------------|---------------|--------------------------------------------------------------------------------|------|

| 600 | N2 / 30 min | Not specified | Not specified | Promotes the formation of the orthorhombic phase in undoped HfO <sub>2</sub> . | [11] |

Table 2: Typical Properties of HfO2 Films and Interfaces

| Deposition<br>Method   | Film<br>Thickness<br>(nm) | Dielectric<br>Constant<br>(k) | Interfacial<br>Layer                | Typical D <sub>it</sub><br>(cm <sup>-2</sup> eV <sup>-1</sup> ) | Citation(s) |

|------------------------|---------------------------|-------------------------------|-------------------------------------|-----------------------------------------------------------------|-------------|

| ALD                    | 8 - 30                    | ~20 (as-<br>deposited)        | ~1-2 nm SiO2                        | ~10 <sup>11</sup> - 10 <sup>12</sup><br>(before<br>anneal)      | [12]        |

| ALD                    | 15                        | Not specified                 | Not specified                       | 3.6 x 10 <sup>10</sup> (after anneal)                           | [3]         |

| UHV E-Beam             | 2.2                       | ~20                           | < 0.15 nm                           | Sufficiently<br>low for<br>MOSFETs                              | [4]         |

| Sputtering             | Not specified             | Not specified                 | Forms<br>SiO <sub>2</sub> /silicate | High,<br>requires<br>passivation                                | [5][13]     |

| Thermal<br>Evaporation | 50 - 60                   | Increases<br>with anneal      | Minimal<br>initially                | Dominated by shallow traps                                      | [1]         |

# **Experimental Protocols**

# Protocol 1: Standard Post-Deposition Annealing (PDA) for Dit Reduction

This protocol describes a general-purpose two-stage annealing process for passivating defects in HfO<sub>2</sub>/Si structures.

Objective: To densify the HfO<sub>2</sub> film and passivate Si interface dangling bonds.

# Methodology:

- Initial High-Temperature Anneal:

- Immediately after HfO<sub>2</sub> deposition, place the wafer in a Rapid Thermal Annealing (RTA) system.

- Purge the chamber with high-purity nitrogen (N2) for 5-10 minutes.

- Ramp up the temperature to 500-700°C at a rate of 50-100°C/s.

- Hold the temperature for 30-60 seconds. This step densifies the film and can initiate crystallization.

- Cool down under the N<sub>2</sub> ambient.

- · Gate Electrode Deposition:

- Deposit the top metal gate electrode (e.g., Al, TiN, Pt) using evaporation or sputtering.

- Final Forming Gas Anneal (FGA):

- Place the now-metallized sample into a tube furnace.

- Purge with forming gas (typically 5% H<sub>2</sub> in 95% N<sub>2</sub>).

- Heat to 400-450°C and hold for 20-30 minutes. This low-temperature step drives hydrogen to the HfO<sub>2</sub>/Si interface to passivate dangling bonds without disturbing the gate metal.

- Cool down to room temperature under the forming gas flow.

# Protocol 2: Characterization of Interface Trap Density (Dit) using the Conductance Method

This protocol outlines the procedure for measuring Dit in a fabricated MOS capacitor.

Objective: To quantify the density of electrically active traps at the HfO<sub>2</sub>/Si interface.

### Methodology:

- Equipment Setup:

- Use a precision LCR meter and a probe station.

- Connect the LCR meter to the top gate electrode and the bottom substrate of the MOS capacitor.

#### Measurement:

- Apply a DC gate voltage (Vg) sweep from strong accumulation to strong inversion.

- At each DC voltage step, superimpose a small AC signal (typically 15-30 mV).

- Measure the parallel capacitance (Cp) and parallel conductance (Gp) as a function of Vg at multiple AC frequencies (e.g., from 1 kHz to 1 MHz).

#### Data Extraction:

- For each frequency, plot Gp/ω versus Vg, where ω = 2πf (f is the measurement frequency).

- The conductance method relies on the energy loss caused by the capture and emission of carriers by interface traps. This loss is maximal when the AC signal frequency matches the trap response time.

- $\circ$  A peak will appear in the Gp/ $\omega$  plot in the depletion region. The magnitude of this peak is directly related to D<sub>it</sub>.

#### Calculation:

- First, correct the measured conductance (Gm) and capacitance (Cm) to extract the true parallel conductance (Gp) by accounting for the oxide capacitance (Cox) and series resistance (Rs).

- o The interface trap density can be calculated from the maximum value of the (Gp/ω) peak using the following relation:  $D_{it} \approx (2.5 / q) * (Gp,max / ω)$  where q is the elementary charge.

- By performing this analysis at different frequencies and temperatures, the D<sub>it</sub> can be mapped across the silicon bandgap.

# **Visualizations**

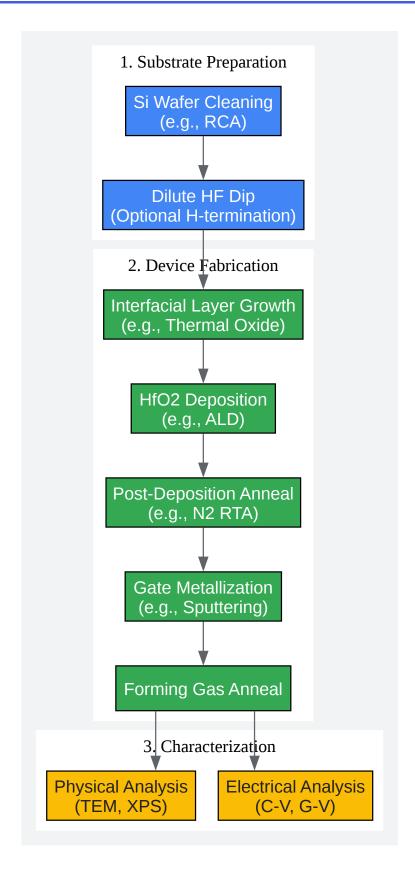

Click to download full resolution via product page

Caption: Experimental workflow for HfO<sub>2</sub>/Si device fabrication and analysis.

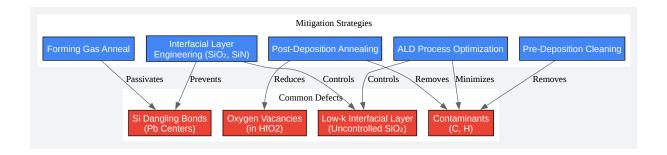

#### Click to download full resolution via product page

Caption: Logical relationships between defects and mitigation strategies.

## **Need Custom Synthesis?**

BenchChem offers custom synthesis for rare earth carbides and specific isotopiclabeling.

Email: info@benchchem.com or Request Quote Online.

# References

- 1. web.njit.edu [web.njit.edu]

- 2. pubs.aip.org [pubs.aip.org]

- 3. pubs.aip.org [pubs.aip.org]

- 4. Study of Direct-Contact HfO2/Si Interfaces PMC [pmc.ncbi.nlm.nih.gov]

- 5. researchgate.net [researchgate.net]

- 6. researchgate.net [researchgate.net]

- 7. pubs.aip.org [pubs.aip.org]

- 8. researchgate.net [researchgate.net]

- 9. pubs.aip.org [pubs.aip.org]

- 10. Temperature-Dependent HfO2/Si Interface Structural Evolution and its Mechanism PMC [pmc.ncbi.nlm.nih.gov]

- 11. mdpi.com [mdpi.com]

- 12. researchgate.net [researchgate.net]

- 13. mdpi.com [mdpi.com]

- 14. csqs.xjtu.edu.cn [csqs.xjtu.edu.cn]

- 15. pubs.aip.org [pubs.aip.org]

- 16. researchgate.net [researchgate.net]

- 17. pubs.aip.org [pubs.aip.org]

- 18. escholarship.org [escholarship.org]

- 19. ieee-jp.org [ieee-jp.org]

- 20. researchgate.net [researchgate.net]

- 21. pubs.aip.org [pubs.aip.org]

- To cite this document: BenchChem. [Technical Support Center: Mitigating Interface Defects in HfO<sub>2</sub>/Si Structures]. BenchChem, [2025]. [Online PDF]. Available at: [https://www.benchchem.com/product/b213204#mitigating-interface-defects-between-hafnium-oxide-and-silicon]

# **Disclaimer & Data Validity:**

The information provided in this document is for Research Use Only (RUO) and is strictly not intended for diagnostic or therapeutic procedures. While BenchChem strives to provide accurate protocols, we make no warranties, express or implied, regarding the fitness of this product for every specific experimental setup.

**Technical Support:**The protocols provided are for reference purposes. Unsure if this reagent suits your experiment? [Contact our Ph.D. Support Team for a compatibility check]

Need Industrial/Bulk Grade? Request Custom Synthesis Quote

# BenchChem

Our mission is to be the trusted global source of essential and advanced chemicals, empowering scientists and researchers to drive progress in science and industry. Contact

Address: 3281 E Guasti Rd

Ontario, CA 91761, United States

Phone: (601) 213-4426

Email: info@benchchem.com