# Technical Support Center: Mitigating Fermi Level Pinning at Metal/MoS<sub>2</sub> Contacts

Author: BenchChem Technical Support Team. Date: December 2025

| Compound of Interest |                    |           |

|----------------------|--------------------|-----------|

| Compound Name:       | Molybdenum sulfide |           |

| Cat. No.:            | B1676702           | Get Quote |

Welcome to the technical support center for researchers, scientists, and professionals working with metal/MoS<sub>2</sub> contacts. This resource provides troubleshooting guidance and answers to frequently asked questions related to the mitigation of Fermi level pinning, a critical challenge in the development of high-performance electronic devices based on molybdenum disulfide (MoS<sub>2</sub>).

## Frequently Asked Questions (FAQs)

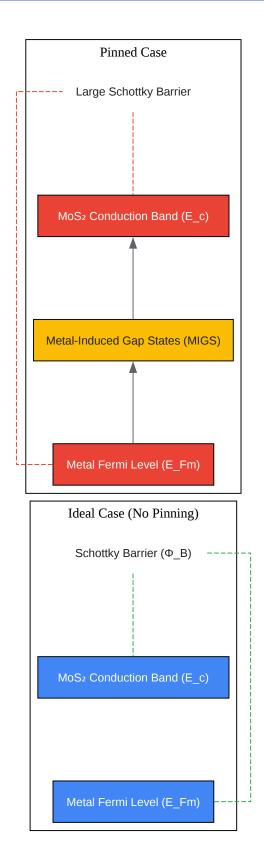

Q1: What is Fermi level pinning and why is it a problem for Metal/MoS2 contacts?

A1: Fermi level pinning (FLP) at the metal-MoS<sub>2</sub> interface is a phenomenon where the Schottky barrier height (SBH) becomes largely independent of the work function of the contact metal.[1] [2][3] This is problematic because it prevents the formation of low-resistance Ohmic contacts, which are crucial for efficient charge carrier injection from the metal to the MoS<sub>2</sub> channel.[1][3] High contact resistance leads to poor device performance, including lower drive currents and higher power consumption. The pinning is often attributed to the formation of metal-induced gap states (MIGS) and interface dipoles.[2][4][5]

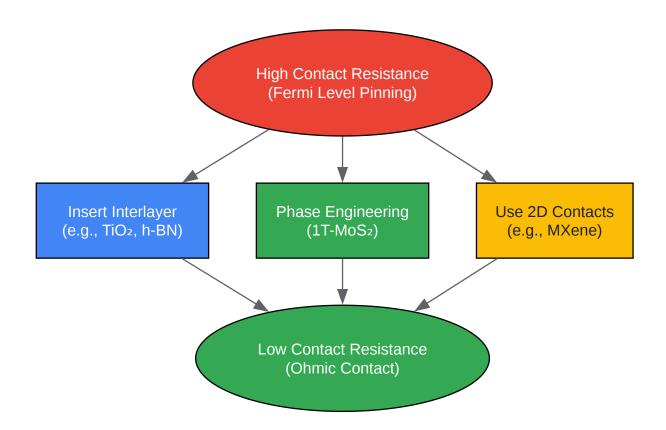

Q2: What are the common strategies to mitigate Fermi level pinning in MoS2 devices?

A2: Several strategies have been developed to overcome Fermi level pinning at metal/MoS<sub>2</sub> contacts:

#### Troubleshooting & Optimization

- Insertion of Interfacial Layers: Introducing a thin insulating or semi-metallic layer, such as titanium dioxide (TiO<sub>2</sub>)[3][6][7][8], hexagonal boron nitride (h-BN)[1], or graphene[9][10], between the metal and MoS<sub>2</sub> can effectively depin the Fermi level.[1] These layers can suppress the formation of MIGS and reduce the interaction between the metal and MoS<sub>2</sub>.[1] [3]

- Phase Engineering: Locally converting the semiconducting 2H phase of MoS<sub>2</sub> to the metallic

1T phase at the contact regions can significantly reduce contact resistance.[11] The 1T phase provides a more efficient path for carrier injection into the 2H channel.

- Use of 2D Metal Contacts (MXenes): Utilizing 2D materials like MXenes (e.g., Ti₃C₂Tx) as contact electrodes can create van der Waals interfaces with MoS₂, which helps in alleviating Fermi level pinning.[12]

- Local Pressurization: Applying local pressure on the MoS<sub>2</sub> under the contact can induce a reversible semiconductor-to-metal transition, thereby lowering the contact resistance.[13]

- Optimized Metal Deposition: The conditions under which the metal contact is deposited, such as the vacuum level, can significantly impact the interface quality and contact resistance.[14] [15][16]

Q3: How do I choose the right contact metal for my MoS2 device?

A3: The choice of contact metal is crucial. While the Schottky-Mott rule suggests selecting a metal with a work function that aligns with the band edges of MoS<sub>2</sub>, Fermi level pinning complicates this.[1] For n-type MoS<sub>2</sub>, low work function metals are generally preferred. However, the chemical reactivity of the metal with MoS<sub>2</sub> is also a critical factor.[17][18][19][20] Some metals can react with MoS<sub>2</sub> and create defects, while others form cleaner van der Waals interfaces. It is often necessary to combine the choice of metal with a pinning mitigation strategy, such as using an interlayer.

Q4: What is the role of defects in Fermi level pinning at the MoS2 interface?

A4: Defects in the MoS<sub>2</sub> lattice, such as sulfur vacancies, can play a significant role in Fermi level pinning.[21] These defects can introduce states within the bandgap of MoS<sub>2</sub>, which can pin the Fermi level. The quality of the MoS<sub>2</sub> film has been shown to dramatically impact the

extent of Fermi level pinning.[22] Subsurface defects, in particular, have been identified as dominant sources of charge transport and strong Fermi level pinning.[21]

## **Troubleshooting Guides**

Issue 1: High Contact Resistance in Fabricated MoS<sub>2</sub> Transistors

- Symptom: The measured resistance of your device is dominated by the contacts, leading to low ON-current and poor device performance.

- Possible Cause: Strong Fermi level pinning at the metal/MoS<sub>2</sub> interface is creating a large Schottky barrier.

- Troubleshooting Steps:

- Characterize the Interface: Use techniques like X-ray Photoelectron Spectroscopy (XPS) to analyze the chemical composition at the metal-MoS<sub>2</sub> interface to check for unwanted reactions or oxide formation.[14][15]

- Implement an Interlayer: Introduce a thin depinning layer like TiO<sub>2</sub> or h-BN between your metal contact and the MoS<sub>2</sub>. This can be done using techniques like atomic layer deposition (ALD) or transfer of 2D materials.[1][6][8]

- Consider Phase Engineering: If your experimental setup allows, attempt to locally induce the metallic 1T phase of MoS<sub>2</sub> in the contact regions using chemical treatments (e.g., organolithium) or laser irradiation.[11]

- Optimize Metal Deposition: Ensure that the metal deposition is carried out under ultra-high vacuum (UHV) conditions to minimize the incorporation of impurities and the formation of oxides at the interface.[14][15][16]

- Evaluate Different Contact Metals: Experiment with different contact metals, paying attention to both their work function and their reactivity with MoS<sub>2</sub>.[23][24]

Issue 2: Inconsistent Device Performance and Large Device-to-Device Variation

Symptom: Fabricated devices show a wide range of contact resistances and overall performance metrics.

- Possible Cause: Inhomogeneous MoS<sub>2</sub> film quality, variations in the metal-MoS<sub>2</sub> interface, or the presence of defects.

- Troubleshooting Steps:

- Assess MoS<sub>2</sub> Quality: Characterize the structural quality of your MoS<sub>2</sub> films using techniques like Raman spectroscopy and Atomic Force Microscopy (AFM) to ensure uniformity and low defect density.[17]

- Control the Fabrication Process: Standardize all fabrication steps, including lithography,

etching, and metal deposition, to minimize process-induced variations.

- Investigate the Role of Defects: Studies have shown that defects can dominate charge transport.[21] Consider pre-treating the MoS<sub>2</sub> surface to passivate defects before metal deposition.

- Statistical Analysis: Fabricate a large number of devices to perform statistical analysis of the performance metrics. This can help identify if the variation is random or systematic.[15]

#### **Quantitative Data Summary**

Table 1: Contact Resistance and Schottky Barrier Height for Different Mitigation Strategies

| Mitigation<br>Strategy      | Metal<br>Contact                                         | Interlayer          | Contact<br>Resistanc<br>e (Ω·μm) | Schottky<br>Barrier<br>Height<br>(eV) | Pinning<br>Factor (S) | Referenc<br>e |

|-----------------------------|----------------------------------------------------------|---------------------|----------------------------------|---------------------------------------|-----------------------|---------------|

| None<br>(Direct<br>Contact) | Various                                                  | None                | 0.7 k - 10 k                     | Varies                                | ~0.1                  | [11][25]      |

| Phase<br>Engineerin<br>g    | Au                                                       | 1T-MoS <sub>2</sub> | 200 - 300                        | -                                     | -                     | [11]          |

| Interlayer                  | Various                                                  | TiO <sub>2</sub>    | ~5.4 k                           | 0.1                                   | 0.24                  | [6][7][8]     |

| Al                          | h-BN                                                     | -                   | ~0                               | -                                     | [1]                   |               |

| Mg, In, Sc,                 | Single-<br>layer<br>Graphene                             | -                   | -0.116 to<br>-0.014              | -                                     | [9]                   | -             |

| Ni                          | Ni-etched<br>Graphene                                    | ~200                | -                                | -                                     | [26]                  | -             |

| 2D Metal<br>Contact         | Ti <sub>3</sub> C <sub>2</sub> T <sub>×</sub><br>(MXene) | None                | -                                | 0.121                                 | 0.87                  | [12]          |

| Optimized Deposition        | Ni                                                       | None<br>(UHV)       | ~500                             | -                                     | -                     | [14][15]      |

| Au                          | None<br>(UHV)                                            | 740                 | -                                | -                                     | [16]                  |               |

| Local<br>Pressurizat<br>ion | -                                                        | -                   | Up to 30-<br>fold<br>reduction   | -                                     | -                     | [13]          |

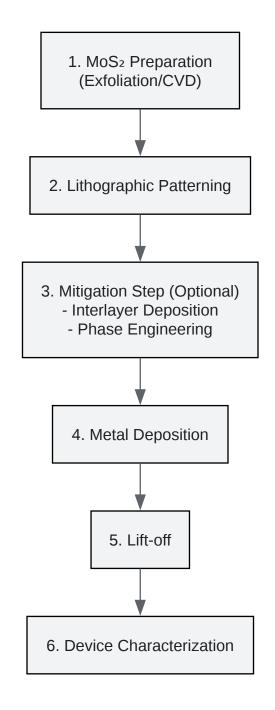

# **Experimental Protocols**

Protocol 1: Fabrication of MoS<sub>2</sub> Transistors with a TiO<sub>2</sub> Interlayer

- Substrate Preparation: Begin with a clean Si/SiO2 substrate.

- MoS<sub>2</sub> Flake Exfoliation/Transfer: Mechanically exfoliate or transfer CVD-grown MoS<sub>2</sub> onto the substrate.

- Contact Patterning: Use electron beam lithography (EBL) or photolithography to define the source and drain contact regions.

- TiO<sub>2</sub> Deposition: Deposit an ultrathin layer of TiO<sub>2</sub> (e.g., 1 nm) using Atomic Layer Deposition (ALD). This allows for precise thickness control.

- Metal Deposition: Immediately following TiO<sub>2</sub> deposition, deposit the desired contact metal (e.g., Ti/Au) using electron beam evaporation or sputtering.

- Lift-off: Perform a lift-off process in a suitable solvent to remove the resist and excess metal, leaving the patterned contacts.

- Annealing: Anneal the device in a controlled environment (e.g., vacuum or inert gas) to improve the contact quality.

#### Protocol 2: Phase Engineering of MoS<sub>2</sub> Contacts

- Device Fabrication: Fabricate the MoS<sub>2</sub> transistor up to the point before contact metallization, with the contact areas on the MoS<sub>2</sub> exposed.

- Chemical Treatment: Immerse the device in an organolithium solution (e.g., n-butyl lithium in hexane) for a specific duration to induce the 2H to 1T phase transition in the exposed MoS<sub>2</sub> regions.

- Quenching: Quench the reaction by rinsing the sample with a suitable solvent.

- Metallization: Proceed with the deposition of the contact metal onto the phase-engineered regions.

- Characterization: Verify the phase transition using techniques like Raman spectroscopy or XPS.

## **Visualizations**

Click to download full resolution via product page

#### **Need Custom Synthesis?**

BenchChem offers custom synthesis for rare earth carbides and specific isotopiclabeling.

Email: info@benchchem.com or Request Quote Online.

## References

#### Troubleshooting & Optimization

- 1. scispace.com [scispace.com]

- 2. pubs.acs.org [pubs.acs.org]

- 3. researchgate.net [researchgate.net]

- 4. cgong.weebly.com [cgong.weebly.com]

- 5. The unusual mechanism of partial Fermi level pinning at metal-MoS2 interfaces PubMed [pubmed.ncbi.nlm.nih.gov]

- 6. Contact resistance reduction using Fermi level de-pinning layer for MoS2 FETs | Semantic Scholar [semanticscholar.org]

- 7. Contact resistance reduction using Fermi level de-pinning layer for MoS2 FETs | IEEE Conference Publication | IEEE Xplore [ieeexplore.ieee.org]

- 8. pubs.acs.org [pubs.acs.org]

- 9. researchgate.net [researchgate.net]

- 10. Tuning the Schottky barrier height in single- and bi-layer graphene-inserted MoS2/metal contacts | Semantic Scholar [semanticscholar.org]

- 11. Phase-engineered low-resistance contacts for ultrathin MoS2 transistors PubMed [pubmed.ncbi.nlm.nih.gov]

- 12. researchgate.net [researchgate.net]

- 13. Low resistance electrical contacts to few-layered MoS 2 by local pressurization | NSF Public Access Repository [par.nsf.gov]

- 14. pubs.acs.org [pubs.acs.org]

- 15. pubs.acs.org [pubs.acs.org]

- 16. poplab.stanford.edu [poplab.stanford.edu]

- 17. researchgate.net [researchgate.net]

- 18. [PDF] Uncovering the Effects of Metal Contacts on Monolayer MoS2. | Semantic Scholar [semanticscholar.org]

- 19. On the Contact Optimization of ALD-Based MoS2 FETs: Correlation of Processing Conditions and Interface Chemistry with Device Electrical Performance - PMC [pmc.ncbi.nlm.nih.gov]

- 20. pubs.acs.org [pubs.acs.org]

- 21. Defect Dominated Charge Transport and Fermi Level Pinning in MoS2/Metal Contacts PMC [pmc.ncbi.nlm.nih.gov]

- 22. pubs.acs.org [pubs.acs.org]

- 23. pubs.aip.org [pubs.aip.org]

- 24. pubs.aip.org [pubs.aip.org]

- 25. pubs.acs.org [pubs.acs.org]

- 26. pubs.acs.org [pubs.acs.org]

- To cite this document: BenchChem. [Technical Support Center: Mitigating Fermi Level Pinning at Metal/MoS<sub>2</sub> Contacts]. BenchChem, [2025]. [Online PDF]. Available at: [https://www.benchchem.com/product/b1676702#mitigating-fermi-level-pinning-at-metal-mos-contacts]

#### **Disclaimer & Data Validity:**

The information provided in this document is for Research Use Only (RUO) and is strictly not intended for diagnostic or therapeutic procedures. While BenchChem strives to provide accurate protocols, we make no warranties, express or implied, regarding the fitness of this product for every specific experimental setup.

**Technical Support:**The protocols provided are for reference purposes. Unsure if this reagent suits your experiment? [Contact our Ph.D. Support Team for a compatibility check]

Need Industrial/Bulk Grade? Request Custom Synthesis Quote

# BenchChem

Our mission is to be the trusted global source of essential and advanced chemicals, empowering scientists and researchers to drive progress in science and industry. Contact

Address: 3281 E Guasti Rd

Ontario, CA 91761, United States

Phone: (601) 213-4426

Email: info@benchchem.com