# Technical Support Center: Minimizing Void Formation in Tin-Zinc Solder Joints

Author: BenchChem Technical Support Team. Date: December 2025

| Compound of Interest |          |           |

|----------------------|----------|-----------|

| Compound Name:       | Tin-ZINC |           |

| Cat. No.:            | B8454451 | Get Quote |

This technical support center provides researchers, scientists, and engineers with comprehensive troubleshooting guides and frequently asked questions to address void formation in **Tin-Zinc** (Sn-Zn) solder joints.

## **Frequently Asked Questions (FAQs)**

Q1: What are voids in the context of solder joints?

A1: Solder joint voids are empty spaces, gaps, or pockets that form within the solder connection between a component and a printed circuit board (PCB).[1][2] These spaces do not contain solder and are typically filled with trapped gases, air, or flux residues that did not escape before the solder solidified.[1][2][3] Voids can be categorized into several types, including macro voids, micro voids, and shrinkage voids, each differing in size, cause, and location.[3][4]

Q2: Why is minimizing void formation in Sn-Zn solder joints critical for my research?

A2: Excessive voiding is considered a defect because it can significantly compromise the integrity and reliability of electronic assemblies.[2] Voids create mechanical weaknesses that can lead to cracks, reduce the joint's current-carrying capacity, and lower its thermal conductivity.[2] For applications requiring effective heat dissipation, such as with high-power components, voids can hinder thermal transfer and lead to component failure.[5][6] For high-density components, void percentages above 25% are often considered a risk to long-term reliability.[7]

Q3: What are the primary causes of void formation?

A3: Void formation is primarily caused by the entrapment of gases that fail to escape the molten solder during the reflow process.[1][8] The main sources of these gases are:

- Solder Paste Outgassing: The flux in the solder paste releases volatile materials and gases as it activates and evaporates during heating.[5][7][8]

- Improper Reflow Profile: An unoptimized heating profile, such as a rapid temperature rampup or insufficient peak temperature, can lead to violent outgassing or prevent complete solder wetting.[5][7]

- Surface Contamination: Moisture, oxides, or other residues on PCB pads or component leads can vaporize during reflow, forming bubbles.[7]

- Component and PCB Design: Factors like via-in-pad designs can trap air, and the choice of surface finish can affect how well the solder wets the surface, influencing gas escape.[7][9]

[10]

### **Troubleshooting Guide**

This guide addresses specific issues you may encounter during your soldering experiments.

Q4: My Sn-Zn solder joints exhibit a high percentage of voids. Which process parameters should I investigate first?

A4: The reflow profile is one of the most critical factors influencing void formation.[1][5] If you are experiencing high void levels, you should first optimize your reflow profile.

- Preheat/Soak Stage: A low preheat temperature or insufficient soak time may not allow the volatile solvents in the flux to fully evaporate before the solder melts.[2][3] Try extending the preheat or soak time to allow these volatiles to escape.[2][11]

- Ramp Rate: A ramp rate that is too high can cause rapid, violent outgassing, trapping bubbles within the solder.[5]

- Peak Temperature and Time Above Liquidus (TAL): The peak temperature and the duration the solder remains molten (TAL) are critical. Insufficient temperature or time may lead to poor

### Troubleshooting & Optimization

wetting, which can trap gases.[8] Conversely, an excessively high peak temperature can sometimes generate additional gases from the flux.[1][5] A longer TAL generally allows more time for bubbles to escape.[8] However, the effect can be flux-dependent.[8]

Q5: How does my choice of solder paste and flux affect voiding in Sn-Zn joints?

A5: The solder paste and flux chemistry are major contributors to void formation.[1][12][13]

- Flux Activity & Volatiles: The primary role of flux is to remove oxides, but the chemical reactions involved can generate by-products like water vapor, which form voids.[12] Fluxes with higher activity can sometimes reduce voids by improving wetting, but can also increase outgassing.[12][14] Low-voiding solder paste formulations are designed to minimize outgassing by using solvents with higher boiling points and optimized activator packages.[3]

[12]

- Solder Powder: The grain size of the solder paste alloy can influence voiding; a clear correlation has been found between solder ball diameter and void percentage.[14]

- Solder Alloy: Different solder alloys exhibit different voiding characteristics.[13] SnAgCu alloys, for instance, have a higher surface tension than traditional tin-lead solders, which can make it more difficult for volatiles to escape.[9] The melting range of the alloy can also play a role; some studies suggest that a wider melting range may help decrease voiding.[10]

Q6: Can the surface finish on my PCB and components contribute to void formation?

A6: Yes, the surface finish plays a major role in voiding as it directly impacts the solder's wetting behavior.[9][10]

- Wettability: Surfaces that are more difficult for solder to wet, such as Organic Solderability

Preservative (OSP) over copper, can lead to higher voiding because poor wetting can trap

gases.[6][10]

- Common Finishes: Studies have shown that finishes like Electroless Nickel Immersion Gold

(ENIG) or Immersion Silver (ImAg) often result in lower voiding compared to bare copper or

OSP, as they promote faster and more complete wetting, allowing gases to escape more

easily.[9][15] The thickness of the metallization layer can also be a factor.[14]

### Troubleshooting & Optimization

Q7: I'm working with Bottom Terminated Components (BTCs) like QFNs and observe significant voiding on the thermal pad. What specific actions can I take?

A7: BTCs are particularly prone to voiding due to the large thermal pad and the confined space, which restricts gas escape routes.[6]

- Stencil Design: The design of the stencil used to print the solder paste is critical. Instead of a single large opening for the thermal pad, use a windowpane or checkerboard pattern. This breaks up the large deposit, creating channels for outgassing volatiles to escape from underneath the component.[10][11] Reducing the solder paste coverage area to 50-80% can also significantly reduce voiding.[10]

- Via-in-Pad: If you have vias in the thermal pad, ensure they are properly filled or tented.

Open vias can act as a pathway for gases from within the PCB to escape up into the solder joint during reflow, causing voids.[5][7]

- Vacuum Reflow: For the most critical applications, vacuum reflow soldering is a highly

effective method. By subjecting the assembly to a vacuum while the solder is molten,

trapped volatiles and bubbles are actively removed from the joint, dramatically reducing void

percentages.[3][15]

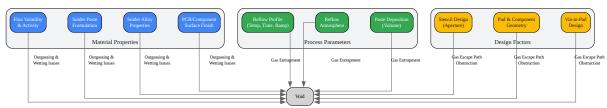

# Visual Guides and Workflows Diagram 1: Root Causes of Void Formation

Figure 1: Key Factors Contributing to Solder Joint Voiding

Click to download full resolution via product page

Caption: Key factors contributing to solder joint voiding.

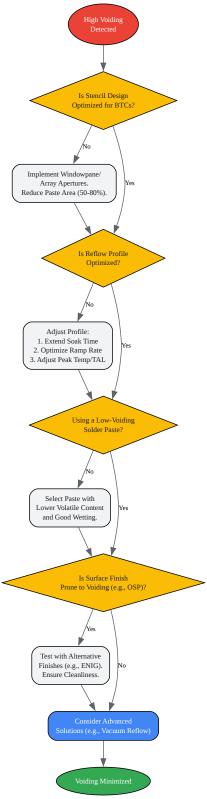

# Diagram 2: Troubleshooting Workflow for Void Reduction

Figure 2: A Step-by-Step Workflow for Diagnosing and Mitigating Voids

Click to download full resolution via product page

Caption: A workflow for diagnosing and mitigating voids.

## **Quantitative Data Summary**

The following tables summarize key experimental parameters and their impact on void formation, based on studies of lead-free solders. These principles are generally applicable to Sn-Zn systems, but specific values may require optimization.

Table 1: Effect of Reflow Profile Parameters on Voiding

| Parameter<br>Variation | Condition 1          | Void %<br>(Typical) | Condition 2                  | Void %<br>(Typical) | Rationale                                                                                                              |

|------------------------|----------------------|---------------------|------------------------------|---------------------|------------------------------------------------------------------------------------------------------------------------|

| Soak Time              | Short Soak           | Higher              | Extended<br>Soak             | Lower               | Allows more time for volatile components of the flux to outgas before the solder fully reflows.                        |

| Peak<br>Temperature    | Low Peak<br>(~235°C) | Higher              | Standard<br>Peak<br>(~245°C) | Lower               | Higher peak temperatures can reduce voiding to a certain extent by improving wetting and allowing gases to escape.[14] |

| Time Above<br>Liquidus | Short TAL            | Higher              | Longer TAL                   | Lower               | Provides a larger window for trapped bubbles to escape from the molten solder, though this can be flux-dependent.[8]   |

Table 2: Influence of PCB Surface Finish on Voiding

| Surface Finish                              | Relative Voiding Tendency | Primary Reason                                                                                                          |

|---------------------------------------------|---------------------------|-------------------------------------------------------------------------------------------------------------------------|

| OSP (Organic Solderability Preservative)    | Higher                    | More difficult to wet, which can lead to the entrapment of flux and volatiles.[9][10]                                   |

| Immersion Tin (ImSn)                        | Moderate                  | Provides good solderability, but performance can be influenced by the thickness and condition of the tin layer.[14][16] |

| Immersion Silver (ImAg)                     | Lower                     | Offers excellent wettability,<br>allowing gases to escape more<br>freely during reflow.[9]                              |

| ENIG (Electroless Nickel<br>Immersion Gold) | Lower                     | Provides a highly solderable and robust surface, leading to rapid wetting and reduced void formation.[9][15][16]        |

## **Experimental Protocols**

Protocol 1: Evaluating the Effect of Reflow Profile on Sn-Zn Solder Voiding

- 1. Objective: To determine the optimal reflow soldering profile for minimizing void formation in Sn-Zn solder joints for a specific component type and PCB design.

- 2. Materials & Equipment:

- Test PCBs with appropriate surface finish (e.g., ENIG).

- Target components (e.g., QFNs or other BTCs).

- Sn-Zn based solder paste.

- Stencil printer and stencil with optimized apertures.

- Pick-and-place machine.

- Forced convection reflow oven with a thermocouple profiling system.

- X-ray inspection system with void calculation software.

- 3. Methodology:

- Sample Preparation: Clean all test PCBs and components to remove any contaminants.

- Solder Paste Printing: Using the stencil printer, apply the Sn-Zn solder paste to the pads of the test PCBs. Ensure a consistent and uniform deposition.

- Component Placement: Use the pick-and-place machine to accurately position the components onto the solder paste deposits.

- Reflow Profile Groups:

- Group A (Control): Process boards using the solder paste manufacturer's standard recommended reflow profile. Attach a thermocouple to a test board to record the actual profile.

- Group B (Extended Soak): Modify the profile to increase the soak time by 30-50%

compared to the control, while keeping other parameters constant.

- Group C (Increased Peak Temp): Modify the profile to increase the peak temperature by 5-10°C compared to the control.

- Group D (Reduced Ramp Rate): Modify the profile to decrease the ramp-up rate, allowing for more gradual heating.

- Reflow Soldering: Process a statistically significant number of boards (e.g., n=5) for each experimental group through the reflow oven.

- Analysis:

- After cooling, visually inspect the solder joints for any obvious defects.

- Use the X-ray inspection system to analyze the target solder joints (e.g., the central thermal pad of a QFN).

- Utilize the system's software to calculate the void percentage for each joint.

- Data Interpretation: Compare the average void percentages across all groups. Use the data

to identify which profile modification had the most significant positive impact on reducing

voids. The results will guide the establishment of an optimized reflow process for your

specific application.

#### **Need Custom Synthesis?**

BenchChem offers custom synthesis for rare earth carbides and specific isotopiclabeling.

Email: info@benchchem.com or Request Quote Online.

#### References

- 1. What does voids in a solder joint mean and what is the solution? [ams-electronics.co.uk]

- 2. Voids in Solder Joints | Prevent Voids in Solder Joints [mclpcb.com]

- 3. venture-mfg.com [venture-mfg.com]

- 4. hisco.com [hisco.com]

- 5. fctsolder.com [fctsolder.com]

- 6. electronics.org [electronics.org]

- 7. Decoding Solder Joint Voids: Causes, Detection, and Prevention Strategies [allpcb.com]

- 8. circuitinsight.com [circuitinsight.com]

- 9. circuitnet.com [circuitnet.com]

- 10. fctsolder.com [fctsolder.com]

- 11. raypcb.com [raypcb.com]

- 12. Void Caused by the Inherent Characteristics of Solder Paste Flux [fitech-solderpaste.com]

- 13. epp-europe-news.com [epp-europe-news.com]

- 14. electronics.org [electronics.org]

- 15. electronics.org [electronics.org]

- 16. Void Formation and Their Effect on Reliability of Lead-Free Solder Joints on MID and PCB Substrates | Semantic Scholar [semanticscholar.org]

To cite this document: BenchChem. [Technical Support Center: Minimizing Void Formation in Tin-Zinc Solder Joints]. BenchChem, [2025]. [Online PDF]. Available at: [https://www.benchchem.com/product/b8454451#minimizing-void-formation-in-tin-zinc-solder-joints]

#### **Disclaimer & Data Validity:**

The information provided in this document is for Research Use Only (RUO) and is strictly not intended for diagnostic or therapeutic procedures. While BenchChem strives to provide accurate protocols, we make no warranties, express or implied, regarding the fitness of this product for every specific experimental setup.

**Technical Support:** The protocols provided are for reference purposes. Unsure if this reagent suits your experiment? [Contact our Ph.D. Support Team for a compatibility check]

Need Industrial/Bulk Grade? Request Custom Synthesis Quote

# BenchChem

Our mission is to be the trusted global source of essential and advanced chemicals, empowering scientists and researchers to drive progress in science and industry.

#### Contact

Address: 3281 E Guasti Rd

Ontario, CA 91761, United States

Phone: (601) 213-4426

Email: info@benchchem.com