# Technical Support Center: Minimizing Interfacial Layer Growth in HfO<sub>2</sub> Deposition

Author: BenchChem Technical Support Team. Date: December 2025

| Compound of Interest |                      |           |

|----------------------|----------------------|-----------|

| Compound Name:       | Hafnium tetranitrate |           |

| Cat. No.:            | B098167              | Get Quote |

This technical support center provides troubleshooting guidance and frequently asked questions (FAQs) to assist researchers, scientists, and drug development professionals in minimizing the formation of an unwanted interfacial layer (IL) during the deposition of hafnium dioxide (HfO<sub>2</sub>). This guide offers practical solutions and detailed experimental protocols to address common challenges encountered in the laboratory.

## **Troubleshooting Guides**

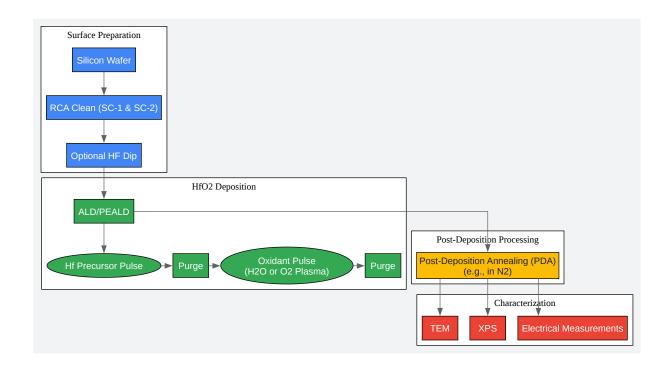

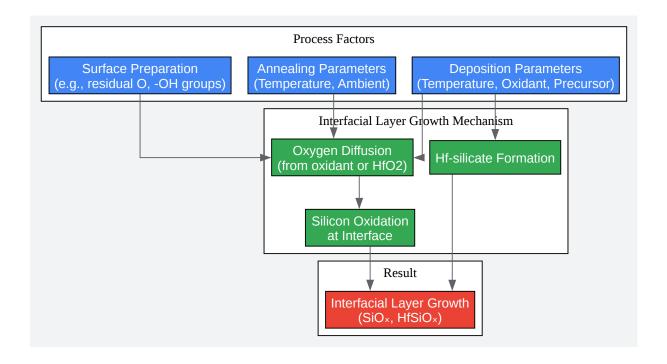

Problem 1: Excessive Interfacial Layer Growth During Deposition

#### Symptoms:

- Thicker than expected interfacial layer observed through Transmission Electron Microscopy (TEM).

- Higher than anticipated Equivalent Oxide Thickness (EOT) in electrical measurements.

- Reduced overall capacitance of the gate stack.

Possible Causes and Solutions:

## Troubleshooting & Optimization

Check Availability & Pricing

| Cause                          | Recommended Solution                                                                                                                                                                                                                                                                                                                                                                                                        |  |

|--------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Inadequate Surface Preparation | Implement a thorough pre-deposition cleaning procedure to remove organic and metallic contaminants. The RCA clean is a standard and effective method. For a pristine, hydrogenterminated surface, an additional diluted hydrofluoric acid (HF) dip (HF-last) can be performed. However, be aware that a bare silicon surface is highly reactive and can reoxidize if not immediately transferred to the deposition chamber. |  |

| Choice of Oxidant              | The choice of oxidant in Atomic Layer  Deposition (ALD) significantly impacts IL growth.  Using a stronger oxidant like ozone (O₃) plasma instead of water (H₂O) can lead to a higher quality HfO₂ film with a potentially thinner or more controlled interfacial layer.[1][2][3]                                                                                                                                           |  |

| Deposition Temperature         | Higher deposition temperatures can promote the reaction between the silicon substrate and the oxidant, leading to increased IL thickness.  Consider reducing the deposition temperature.  Plasma-Enhanced ALD (PEALD) allows for lower deposition temperatures compared to thermal ALD, which can help in minimizing IL growth.[2][4][5][6]                                                                                 |  |

| Choice of Hafnium Precursor    | Different hafnium precursors exhibit varying reactivity with the substrate. Metal-organic precursors like Tetrakis(dimethylamino)hafnium (TDMAH) or Tetrakis(ethylmethylamino)hafnium (TEMAH) are often preferred over halide precursors like Hafnium tetrachloride (HfCl <sub>4</sub> ) as they can lead to a more controlled initial growth and potentially a thinner interfacial layer.[7][8][9]                         |  |

Problem 2: Interfacial Layer Growth During Post-Deposition Annealing (PDA)

#### Symptoms:

- Increase in interfacial layer thickness after the annealing step.

- Degradation of electrical properties, such as increased leakage current, after annealing.

#### Possible Causes and Solutions:

| Cause                              | Recommended Solution                                                                                                                                                                                                                                                                                                                                                                                                                            |  |

|------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Annealing Ambient                  | Annealing in an oxygen-containing ambient will invariably lead to the growth of the interfacial layer. To minimize this, perform the post-deposition anneal in an inert atmosphere, such as nitrogen (N <sub>2</sub> ) or argon (Ar).[11][12]                                                                                                                                                                                                   |  |

| Annealing Temperature and Duration | High annealing temperatures and long durations can provide the thermal budget for oxygen diffusion from the HfO <sub>2</sub> layer to the silicon interface, promoting IL growth. Optimize the annealing temperature and time to achieve the desired HfO <sub>2</sub> crystallization without excessive IL formation. Rapid Thermal Annealing (RTA) is often preferred over conventional furnace annealing due to the shorter processing times. |  |

| In-situ Treatments                 | Consider in-situ treatments to make the interface more robust against oxidation during annealing. A pre-deposition in-situ nitridation of the silicon surface can form a thin silicon nitride layer that acts as a barrier to oxygen diffusion.  [1]                                                                                                                                                                                            |  |

# Frequently Asked Questions (FAQs)

Q1: What is the typical thickness of the interfacial layer in HfO2 deposition?

The thickness of the interfacial layer can range from a few angstroms to several nanometers, depending on the deposition method, surface preparation, and post-deposition processing. For example, HfO<sub>2</sub> films deposited using PEALD with an O<sub>2</sub> plasma oxidant on a silicon substrate have shown an interfacial layer thickness of approximately 2.6 nm, which increased to 3.0 nm after annealing at 800°C. In contrast, using an N<sub>2</sub>O plasma under similar conditions resulted in a thinner and more stable interfacial layer of about 2.0 nm, even after annealing.[13]

Q2: How can I accurately measure the thickness of the interfacial layer?

High-Resolution Transmission Electron Microscopy (HR-TEM) is the most direct method for visualizing and measuring the thickness of the interfacial layer. X-ray Photoelectron Spectroscopy (XPS) can also be used to chemically characterize the interface and estimate the IL thickness by analyzing the Si 2p core level spectra to distinguish between silicon, sub-oxides, and SiO<sub>2</sub>.

Q3: Does the number of ALD cycles affect the interfacial layer thickness?

The initial ALD cycles are crucial in the formation of the interfacial layer. The IL growth is often most significant during the nucleation phase of the HfO<sub>2</sub> film. After a certain number of cycles, the HfO<sub>2</sub> film becomes continuous and can act as a barrier, slowing down further IL growth during the deposition process itself.

Q4: What is the effect of an interfacial layer on the device performance?

The presence of a  $SiO_x$  interfacial layer, which has a lower dielectric constant ( $k \approx 3.9$ ) than  $HfO_2$  ( $k \approx 25$ ), effectively reduces the total capacitance of the gate stack, increasing the EOT. While a thin, high-quality  $SiO_2$  layer can be beneficial for reducing interface traps and improving channel mobility, a thick or poor-quality IL can degrade device performance by increasing the leakage current and reducing the overall capacitance.[14][15]

## **Quantitative Data Summary**

Table 1: Effect of Post-Deposition Annealing (PDA) on Interfacial Layer Thickness

| Deposition<br>Method | As-Deposited<br>IL Thickness | Annealing<br>Conditions     | Post-<br>Annealing IL<br>Thickness       | Reference |

|----------------------|------------------------------|-----------------------------|------------------------------------------|-----------|

| PECVD                | ~1.0 nm                      | 900°C in N2                 | ~1.3 nm                                  | [12]      |

| RP-ALD               | Amorphous IL                 | < 400°C in N <sub>2</sub>   | Amorphous IL                             | [11]      |

| RP-ALD               | Amorphous IL                 | 450-550°C in N <sub>2</sub> | Crystalline SiO <sub>2</sub>             | [11]      |

| RP-ALD               | Amorphous IL                 | > 550°C in N2               | Fully crystalline<br>SiO <sub>2</sub> IL | [11]      |

Table 2: Comparison of Oxidants in Plasma-Enhanced ALD (PEALD) of HfO2

| Oxidant               | As-<br>Deposited<br>IL<br>Thickness | Post-<br>Annealing<br>IL<br>Thickness<br>(800°C, 1<br>min, N <sub>2</sub> ) | EOT (Post-<br>Annealing) | Leakage<br>Current<br>Density<br>(Post-<br>Annealing) | Reference |

|-----------------------|-------------------------------------|-----------------------------------------------------------------------------|--------------------------|-------------------------------------------------------|-----------|

| O <sub>2</sub> plasma | 2.6 nm                              | 3.0 nm                                                                      | 2.01 nm                  | $1.3 \times 10^{-7}$ A/cm <sup>2</sup>                | [13]      |

| N₂O plasma            | ~2.0 nm                             | ~2.0 nm                                                                     | 1.56 nm                  | 4.8 x 10 <sup>-8</sup><br>A/cm <sup>2</sup>           | [13]      |

## **Experimental Protocols**

Protocol 1: Standard RCA Clean for Silicon Wafers

This protocol describes the standard RCA cleaning procedure to remove organic and inorganic contaminants from silicon wafers prior to HfO<sub>2</sub> deposition.[8][14][16]

#### Materials:

• Deionized (DI) water

- Ammonium hydroxide (NH<sub>4</sub>OH, 29% by weight of NH<sub>3</sub>)

- Hydrogen peroxide (H<sub>2</sub>O<sub>2</sub>, 30%)

- Hydrochloric acid (HCl, 37%)

- Fused silica or quartz beakers

- Wafer handling tweezers

#### Procedure:

- SC-1 (Organic Clean):

- Prepare a solution of DI water, NH₄OH, and H₂O₂ in a 5:1:1 volume ratio in a fused silica beaker.

- Heat the solution to 75-80°C.

- Immerse the silicon wafers in the hot SC-1 solution for 10 minutes to remove organic contaminants and particles.

- o Rinse the wafers thoroughly with DI water.

- Optional HF Dip (Oxide Strip):

- To remove the thin chemical oxide grown during the SC-1 step and achieve a hydrogen-terminated surface, immerse the wafers in a dilute hydrofluoric acid (HF) solution (e.g., 1:50 HF:DI water) for 15-30 seconds at room temperature.

- Rinse the wafers thoroughly with DI water. Caution: HF is extremely hazardous. Follow all safety protocols.

- SC-2 (Ionic Clean):

- Prepare a solution of DI water, HCl, and H<sub>2</sub>O<sub>2</sub> in a 6:1:1 volume ratio in a fused silica beaker.

- Heat the solution to 75-80°C.

- Immerse the wafers in the hot SC-2 solution for 10 minutes to remove metallic (ionic) contaminants.

- Rinse the wafers thoroughly with DI water.

- Drying:

- Dry the wafers using a spin dryer or by blowing with high-purity nitrogen gas.

Protocol 2: Post-Deposition Annealing in an Inert Atmosphere

This protocol outlines a general procedure for post-deposition annealing of HfO<sub>2</sub> films to promote crystallization while minimizing interfacial layer growth.

#### Equipment:

- Rapid Thermal Annealing (RTA) system or a tube furnace with a controlled atmosphere.

- High-purity nitrogen (N<sub>2</sub>) or argon (Ar) gas.

#### Procedure:

- Sample Loading:

- Load the wafer with the as-deposited HfO<sub>2</sub> film into the annealing chamber.

- Purging:

- Purge the chamber with high-purity N<sub>2</sub> or Ar gas for a sufficient time to displace any residual oxygen and moisture. A typical purge time is 10-20 minutes.

- Ramping to Annealing Temperature:

- Ramp up the temperature to the desired setpoint (e.g., 400-800°C) under a continuous flow of the inert gas. The ramp rate can be controlled in an RTA system.

- Annealing:

- Hold the temperature at the setpoint for the desired duration (e.g., 30-60 seconds for RTA or longer for furnace annealing).

- Cool-down:

- o Cool down the chamber to room temperature under the inert gas flow.

- Sample Unloading:

- o Once the wafer has cooled, unload it from the chamber.

## **Visualizations**

Click to download full resolution via product page

#### **Need Custom Synthesis?**

BenchChem offers custom synthesis for rare earth carbides and specific isotopiclabeling.

Email: info@benchchem.com or Request Quote Online.

### References

- 1. ir.lib.nycu.edu.tw [ir.lib.nycu.edu.tw]

- 2. researchgate.net [researchgate.net]

- 3. mdpi.com [mdpi.com]

- 4. researchgate.net [researchgate.net]

### Troubleshooting & Optimization

- 5. Comparison between thermal and plasma enhanced atomic layer deposition processes for the growth of HfO2 dielectric layers | Catania HQ [hq.imm.cnr.it]

- 6. Uniformity of HfO2 Thin Films Prepared on Trench Structures via Plasma-Enhanced Atomic Layer Deposition [mdpi.com]

- 7. researchgate.net [researchgate.net]

- 8. researchgate.net [researchgate.net]

- 9. A Comparative Study on the Ferroelectric Performances in Atomic Layer Deposited Hf0.5Zr0.5O2 Thin Films Using Tetrakis(ethylmethylamino) and Tetrakis(dimethylamino) Precursors PMC [pmc.ncbi.nlm.nih.gov]

- 10. mdpi.com [mdpi.com]

- 11. gcris.iyte.edu.tr [gcris.iyte.edu.tr]

- 12. Optica Publishing Group [opg.optica.org]

- 13. researchgate.net [researchgate.net]

- 14. briefs.techconnect.org [briefs.techconnect.org]

- 15. worldscientific.com [worldscientific.com]

- 16. bdt.semi.ac.cn [bdt.semi.ac.cn]

- To cite this document: BenchChem. [Technical Support Center: Minimizing Interfacial Layer Growth in HfO<sub>2</sub> Deposition]. BenchChem, [2025]. [Online PDF]. Available at: [https://www.benchchem.com/product/b098167#minimizing-interfacial-layer-growth-in-hfo2-deposition]

#### **Disclaimer & Data Validity:**

The information provided in this document is for Research Use Only (RUO) and is strictly not intended for diagnostic or therapeutic procedures. While BenchChem strives to provide accurate protocols, we make no warranties, express or implied, regarding the fitness of this product for every specific experimental setup.

**Technical Support:**The protocols provided are for reference purposes. Unsure if this reagent suits your experiment? [Contact our Ph.D. Support Team for a compatibility check]

Need Industrial/Bulk Grade? Request Custom Synthesis Quote

# BenchChem

Our mission is to be the trusted global source of essential and advanced chemicals, empowering scientists and researchers to drive progress in science and industry. Contact

Address: 3281 E Guasti Rd

Ontario, CA 91761, United States

Phone: (601) 213-4426

Email: info@benchchem.com