Check Availability & Pricing

# Technical Support Center: Minimizing Interface Traps at the SiC/SiO2 Interface

Author: BenchChem Technical Support Team. Date: December 2025

| Compound of Interest |                 |           |

|----------------------|-----------------|-----------|

| Compound Name:       | Silicon carbide |           |

| Cat. No.:            | B1214593        | Get Quote |

This technical support center provides researchers, scientists, and drug development professionals with troubleshooting guides and frequently asked questions (FAQs) to address common issues encountered during experiments aimed at minimizing interface traps at the SiC/SiO2 interface.

### Frequently Asked Questions (FAQs)

Q1: What are interface traps at the SiC/SiO2 interface and why are they problematic?

A1: Interface traps are electronically active defects located at the boundary between the **silicon carbide** (SiC) substrate and the silicon dioxide (SiO2) dielectric layer. These traps can capture and emit charge carriers (electrons and holes), which degrades the performance of SiC-based metal-oxide-semiconductor field-effect transistors (MOSFETs). The primary issues arising from a high density of interface traps (Dit) include reduced channel mobility, threshold voltage instability, and increased channel resistance, all of which limit the overall efficiency and reliability of the device.[1][2][3]

Q2: What are the primary causes of high interface trap density in SiC/SiO2 structures?

A2: The high density of interface traps at the 4H-SiC/SiO2 interface is a significant challenge that can impede the performance of 4H-SiC MOSFETs.[1] The formation of these traps is largely attributed to the thermal oxidation process itself. Key contributors include:

#### Troubleshooting & Optimization

- Carbon-related defects: During thermal oxidation of SiC, excess carbon can accumulate at the interface, forming carbon clusters or Si-C-O compounds that act as electrically active defects.[3][4]

- Silicon-related defects: Si-Si bonds, silicon dangling bonds, and silicon vacancies near the interface can also introduce trap states.[5]

- Sub-stoichiometric silicon oxide: The presence of a thin layer of sub-stoichiometric silicon oxide (~1nm) at the interface can contribute to trapping.[4]

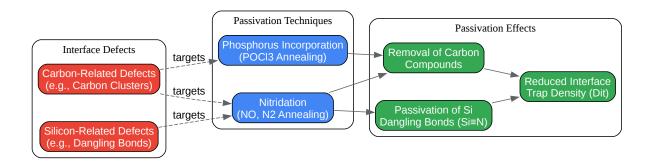

Q3: What are the most common methods to reduce or "passivate" these interface traps?

A3: Post-oxidation annealing (POA) is the most widely used technique to passivate interface traps. This involves heating the oxidized SiC wafer in a specific gas environment. The most effective and commonly used methods include:

- Nitric Oxide (NO) Annealing: This is considered the standard and most effective process for reducing interface trap density near both the conduction and valence band edges.[1]

- Nitrogen (N2) Annealing: High-temperature annealing in N2 can also significantly reduce interface traps, particularly near the valence band edge.[1]

- Phosphoryl Chloride (POCI3) Annealing: This method has been shown to be highly effective

in reducing interface state density, sometimes even more so than NO annealing.[5] A

subsequent NO anneal can further improve the interface quality.[5]

Q4: How do nitridation-based annealing processes (e.g., in NO or N2) work to passivate interface traps?

A4: Nitridation introduces nitrogen atoms at the SiC/SiO2 interface. This process is believed to passivate traps in several ways:

- Passivation of Dangling Bonds: Nitrogen can form strong Si≡N bonds, which passivates silicon dangling bonds at the interface.[5]

- Removal of Carbon-Related Defects: Nitrogen can help to remove carbon-oxide compounds from the interface, a process sometimes referred to as nitrogen-assisted carbon removal.[5]

Q5: Can alternative passivation techniques be used?

A5: Yes, researchers are exploring various alternative techniques. One promising method involves the incorporation of impurities like barium (Ba) at the interface before oxide deposition, which has been shown to passivate the interface without introducing significant strain.[2] Another approach is the use of alumina-enhanced oxidation, though this can introduce mobile ions into the oxide.[6]

## **Troubleshooting Guide**

# Troubleshooting & Optimization

Check Availability & Pricing

| Problem                                                   | Possible Causes                                                                                                           | Suggested Solutions & Troubleshooting Steps                                                                                                                                                                                                                                                                                                                                                                                                                       |

|-----------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| High Interface Trap Density (Dit) after Thermal Oxidation | Incomplete passivation of carbon and silicon-related defects.                                                             | 1. Implement Post-Oxidation Annealing (POA): If not already done, introduce a POA step. NO annealing is a good starting point. 2. Optimize POA Parameters: Adjust the temperature and duration of the anneal. For NO, temperatures around 1175°C for 2 hours are common.[1] For N2, higher temperatures (e.g., 1500°C) may be necessary.[1] 3. Consider a Two-Step Anneal: A sequential anneal, for instance with POCI3 followed by NO, can be more effective.[5] |

| Low Channel Mobility in Fabricated MOSFETs                | High Dit is a primary cause of reduced channel mobility.[1][2]                                                            | 1. Address High Dit: Follow the steps outlined above to reduce interface trap density. 2. Characterize the Interface: Use techniques like Capacitance-Voltage (C-V) measurements to quantify Dit and correlate it with mobility measurements.                                                                                                                                                                                                                     |

| Threshold Voltage (Vth) Instability                       | Charge trapping and detrapping at the interface and in the near-interface oxide traps (NIOTs) during device operation.[4] | Improve Passivation:     Effective passivation with NO has been shown to reduce both interface states and NIOTs, leading to better Vth stability.[4] 2. Investigate Oxide Quality: Poor oxide quality can exacerbate Vth instability.                                                                                                                                                                                                                             |

|                                                            |                                                                                                                                                                                                   | Ensure a high-quality thermal oxide is grown.                                                                                                                                                                                                                                                                                                                                                                           |

|------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Inconsistent or Non-<br>Repeatable Experimental<br>Results | High-temperature processes at<br>the SiC/SiO2 interface can be<br>sensitive and difficult to<br>reproduce.[5]                                                                                     | 1. Strict Process Control:  Maintain tight control over all experimental parameters, including furnace temperature, gas flow rates, and annealing times. 2. Substrate Quality: Ensure consistent quality of the SiC wafers used. 3. Thorough Cleaning: Implement a rigorous pre-oxidation cleaning procedure (e.g., RCA clean followed by a dip in diluted hydrofluoric acid) to ensure a pristine starting surface.[7] |

| Lower than Expected Oxide<br>Breakdown Voltage             | High-temperature annealing can sometimes affect the oxide integrity. For example, N2 annealing at very high temperatures might lead to crystallization, which can lower the breakdown voltage.[1] | 1. Optimize Annealing Temperature: Find a balance between a temperature high enough for effective passivation and one that does not compromise the oxide's dielectric strength. 2. Characterize Breakdown: Perform current-voltage (I-V) measurements to determine the breakdown voltage of your MOS capacitors.[1]                                                                                                     |

## **Quantitative Data Summary**

The following table summarizes the impact of different post-oxidation annealing (POA) treatments on the interface trap density (Dit) at the 4H-SiC/SiO2 interface.

| Annealing Process              | Annealing<br>Temperature (°C) | Resulting Dit<br>(cm <sup>-2</sup> eV <sup>-1</sup> ) | Key Observations                                                                                        |

|--------------------------------|-------------------------------|-------------------------------------------------------|---------------------------------------------------------------------------------------------------------|

| NO Anneal                      | 1175                          | -                                                     | Standard and effective<br>method for reducing<br>Dit.[1]                                                |

| N2 Anneal                      | 1500                          | -                                                     | More effective at passivating traps near the valence band edge compared to the conduction band edge.[1] |

| POCI3 Anneal                   | 1000                          | Lower than NO anneal                                  | Can be more effective at reducing Dit than NO annealing.[5]                                             |

| POCI3 followed by NO<br>Anneal | POCI3 at 1000, NO at<br>1175  | ~2 x 10 <sup>11</sup>                                 | A sequential process can yield very low interface trap densities.[5]                                    |

## **Experimental Protocols**

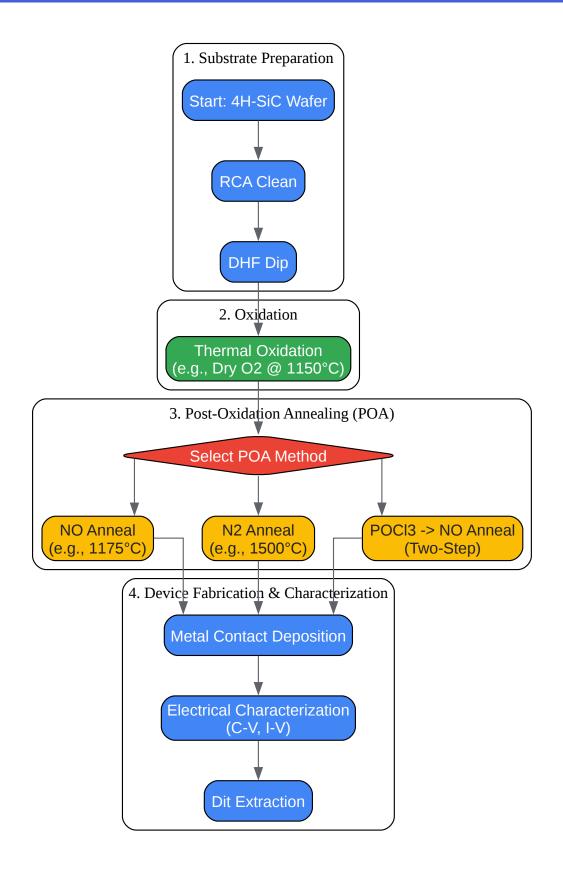

# Protocol 1: Standard Thermal Oxidation and Nitric Oxide (NO) Post-Oxidation Annealing

This protocol describes a typical process for growing a thermal oxide on a 4H-SiC wafer followed by a standard NO anneal to passivate interface traps.

- 1. Substrate Preparation (Pre-Cleaning): a. Perform a standard RCA clean to remove organic and metallic contaminants. b. Follow with a dip in diluted hydrofluoric acid (DHF) to remove any native oxide.[7] c. Rinse thoroughly with deionized (DI) water and dry with nitrogen.

- 2. Thermal Oxidation: a. Load the cleaned 4H-SiC wafer into a horizontal tube furnace. b. Perform the oxidation in a dry O2 environment at a temperature of 1150°C.[1] The oxidation time will depend on the desired oxide thickness.

- 3. Post-Oxidation Annealing (POA) in NO: a. After oxidation, without removing the wafer from the furnace, switch the gas to nitric oxide (NO). b. Anneal the wafer at 1175°C for 2 hours in a flowing NO ambient.[1] c. After the anneal, cool the furnace down in an inert atmosphere (e.g., N2 or Ar).

- 4. Metal Contact Deposition: a. Deposit metal contacts (e.g., aluminum) on the oxide surface to form MOS capacitors for electrical characterization. b. Deposit a large area ohmic contact on the backside of the wafer.

- 5. Characterization: a. Perform high-frequency Capacitance-Voltage (C-V) measurements to determine the flatband voltage and assess the interface quality. b. Use techniques like the Terman method or the high-low frequency C-V method to extract the interface trap density (Dit) as a function of energy in the bandgap.

# Protocol 2: Two-Step POCI3 and NO Post-Oxidation Annealing

This protocol details a more advanced two-step annealing process using POCl3 and NO for enhanced interface passivation.[5]

- 1. Substrate Preparation and Thermal Oxidation: a. Follow steps 1 and 2 from Protocol 1 to prepare the substrate and grow the initial thermal oxide.

- 2. POCI3 Annealing: a. In the same furnace, introduce phosphoryl chloride (POCI3) vapor at a temperature of 1000°C. The duration of this step will influence the phosphorus concentration at the interface.

- 3. NO Annealing: a. Following the POCI3 step, purge the furnace with an inert gas. b. Introduce nitric oxide (NO) and raise the temperature to 1175°C for the subsequent annealing step.

- 4. Metal Contact Deposition and Characterization: a. Follow steps 4 and 5 from Protocol 1 to complete the device fabrication and perform electrical characterization to determine the resulting Dit.

#### **Visualizations**

Click to download full resolution via product page

Caption: Experimental workflow for SiC/SiO2 interface passivation.

Click to download full resolution via product page

Caption: Logical relationship of passivation techniques to defect reduction.

#### **Need Custom Synthesis?**

BenchChem offers custom synthesis for rare earth carbides and specific isotopiclabeling.

Email: info@benchchem.com or Request Quote Online.

#### References

- 1. pubs.aip.org [pubs.aip.org]

- 2. pubs.aip.org [pubs.aip.org]

- 3. 4H-SiC/SiO2 Interface Degradation in 1.2 kV 4H-SiC MOSFETs Due to Power Cycling Tests [mdpi.com]

- 4. iris.cnr.it [iris.cnr.it]

- 5. mdpi.com [mdpi.com]

- 6. Alternative Growth and Interface Passivation Techniques for SiO2 on 4H-SiC [etd.auburn.edu]

- 7. scientific.net [scientific.net]

To cite this document: BenchChem. [Technical Support Center: Minimizing Interface Traps at the SiC/SiO2 Interface]. BenchChem, [2025]. [Online PDF]. Available at: [https://www.benchchem.com/product/b1214593#minimizing-interface-traps-at-the-sic-sio2-interface]

#### **Disclaimer & Data Validity:**

The information provided in this document is for Research Use Only (RUO) and is strictly not intended for diagnostic or therapeutic procedures. While BenchChem strives to provide accurate protocols, we make no warranties, express or implied, regarding the fitness of this product for every specific experimental setup.

**Technical Support:**The protocols provided are for reference purposes. Unsure if this reagent suits your experiment? [Contact our Ph.D. Support Team for a compatibility check]

Need Industrial/Bulk Grade? Request Custom Synthesis Quote

## BenchChem

Our mission is to be the trusted global source of essential and advanced chemicals, empowering scientists and researchers to drive progress in science and industry.

#### Contact

Address: 3281 E Guasti Rd

Ontario, CA 91761, United States

Phone: (601) 213-4426

Email: info@benchchem.com