# Technical Support Center: Minimizing Interface Defects Between Hafnium Silicide and Silicon

Author: BenchChem Technical Support Team. Date: December 2025

This technical support center provides troubleshooting guides and frequently asked questions (FAQs) for researchers, scientists, and drug development professionals working on minimizing interface defects during the formation of **hafnium silicide** (HfSi<sub>2</sub>) on silicon (Si) substrates.

## **Frequently Asked Questions (FAQs)**

Q1: What are the primary causes of interface defects between hafnium silicide and silicon?

A1: Interface defects at the HfSi<sub>2</sub>/Si junction primarily arise from:

- Lattice Mismatch: The difference in the crystal lattice structures of hafnium silicide and silicon can introduce strain and lead to the formation of dislocations and other structural defects at the interface.

- Interdiffusion of Atoms: The diffusion of hafnium (Hf) into the silicon substrate or silicon (Si) into the hafnium film during high-temperature processing can create point defects and disordered regions. Si is the dominant diffusing species during the formation of HfSi.[1][2][3]

- Contamination: Impurities on the silicon surface prior to hafnium deposition or contaminants in the processing environment can get trapped at the interface, creating electrically active defects.

- Unintentional Interfacial Layer Formation: The presence of a native silicon oxide (SiO<sub>2</sub>) layer or the unintentional formation of hafnium silicate (HfSiO<sub>x</sub>) can lead to a complex interface

### Troubleshooting & Optimization

with a higher density of states. While a controlled silicate layer can sometimes be beneficial, its thermal instability can lead to silicidation and degrade the interface.[4]

• High-Temperature Annealing: While necessary for silicide formation, high-temperature annealing can induce stress, cause phase separation in interfacial layers, and lead to the formation of crystalline defects.[4][5]

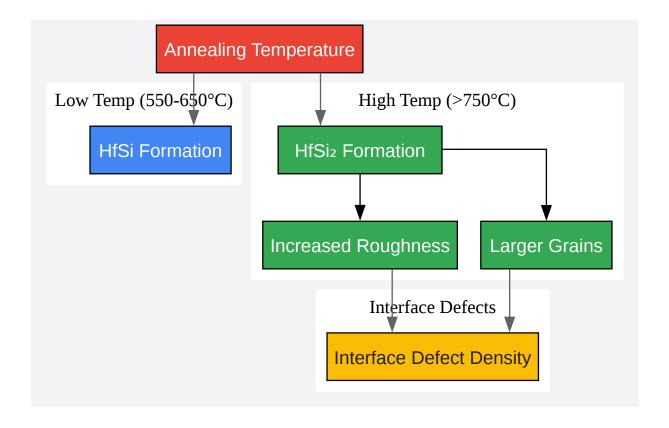

Q2: How does the annealing temperature affect the formation of **hafnium silicide** and the interface quality?

A2: Annealing temperature is a critical parameter. The stable HfSi phase typically forms in the temperature range of 550-650°C.[2][6] The desired HfSi2 phase forms at higher temperatures, generally above 750°C.[2][6] Increasing the annealing temperature promotes the reaction between hafnium and silicon to form a more uniform silicide layer. However, excessively high temperatures can lead to increased surface roughness, larger grain sizes, and higher stress, which can negatively impact the interface quality.[5] For instance, annealing HfO2 films at temperatures greater than 600°C is often desired for good quality films with larger crystalline and grain sizes.[5]

Q3: What is the role of the silicon surface preparation in minimizing interface defects?

A3: Proper silicon surface preparation is crucial for achieving a high-quality HfSi<sub>2</sub>/Si interface. The primary goal is to remove the native silicon oxide layer and any organic or metallic contaminants. A common procedure involves:

- Degreasing: Sonication in organic solvents to remove organic residues.

- Oxide Removal: Etching in a dilute hydrofluoric acid (HF) solution to strip the native SiO<sub>2</sub>.[1]

- Final Rinse and Dry: Rinsing in deionized water and drying with a stream of inert gas (e.g., nitrogen).

For more sensitive applications, an in-situ cleaning step within the deposition chamber, such as a thermal flash or a plasma etch, can be employed immediately before hafnium deposition to ensure a pristine silicon surface.

Q4: Can the annealing ambient influence the interface defect density?

A4: Yes, the annealing ambient plays a significant role. Annealing in an inert atmosphere, such as nitrogen (N<sub>2</sub>) or argon (Ar), is typically preferred to prevent the oxidation of the hafnium and the silicon substrate. Post-deposition annealing in an O<sub>2</sub> ambient can lead to the formation of hafnium oxide or silicate layers, which may be desirable in some applications but can complicate the direct HfSi<sub>2</sub>/Si interface.[5][7] For passivation of certain types of defects, a forming gas anneal (a mixture of N<sub>2</sub> and H<sub>2</sub>) at lower temperatures (e.g., 400-500°C) after silicide formation can be beneficial.

## **Troubleshooting Guides**

# Troubleshooting & Optimization

Check Availability & Pricing

| Issue                            | Potential Causes                                                                                                                                             | Troubleshooting Steps                                                                                                                                                                                                                                                                                                                                                         |

|----------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| High Leakage Current             | High density of interface traps, presence of pinholes or voids in the silicide film, unintentional formation of a leaky interfacial oxide or silicate layer. | 1. Optimize the silicon surface cleaning procedure to minimize initial contamination. 2. Verify the integrity of the deposited hafnium film before annealing. 3. Optimize the annealing temperature and time to ensure complete and uniform silicide formation without excessive roughness. 4.  Consider a post-silicidation forming gas anneal to passivate interface traps. |

| Poor Film Adhesion               | Incomplete removal of the native silicon oxide, surface contamination.                                                                                       | 1. Ensure the HF etching step completely removes the native oxide. Use ellipsometry to verify. 2. Minimize the time between surface cleaning and loading the substrate into the deposition chamber to reduce re-oxidation. 3. Consider an insitu pre-deposition cleaning step.                                                                                                |

| Non-uniform Silicide Formation   | Non-uniform hafnium deposition, temperature gradients across the wafer during annealing, presence of a patterned or non-uniform native oxide.                | 1. Calibrate the deposition system to ensure uniform film thickness. 2. Use a rapid thermal annealing (RTA) system for better temperature uniformity. 3. Ensure complete and uniform removal of any surface oxides before deposition.                                                                                                                                         |

| Unintentional Silicate Formation | Presence of residual oxygen in the annealing ambient,                                                                                                        | Use a high-purity inert gas     for annealing and ensure the                                                                                                                                                                                                                                                                                                                  |

### Troubleshooting & Optimization

Check Availability & Pricing

reaction with a native or chemically grown oxide layer.

annealing chamber has a low base pressure. 2. Thoroughly remove the native oxide from the silicon surface before hafnium deposition. 3. If a silicate layer is desired, precisely control the oxygen partial pressure and annealing temperature.

# Quantitative Data on Process Parameters and Interface Properties

The following table summarizes the impact of key experimental parameters on the properties of the **hafnium silicide**/silicon interface.

| Parameter                                         | Condition                                      | Effect on<br>HfSi <sub>2</sub> /Si<br>Interface                           | Interface State<br>Density (Dit)                      | Reference |

|---------------------------------------------------|------------------------------------------------|---------------------------------------------------------------------------|-------------------------------------------------------|-----------|

| Annealing<br>Temperature                          | 550-650°C                                      | Formation of HfSi phase.                                                  | -                                                     | [2][6]    |

| > 750°C                                           | Formation of HfSi <sub>2</sub> phase.          | -                                                                         | [2][6]                                                |           |

| 600°C (for HfO <sub>2</sub> )                     | Reduced film roughness.                        | -                                                                         | [5]                                                   |           |

| 800°C                                             | Increased<br>crystallite and<br>grain size.    | -                                                                         | [5]                                                   |           |

| Annealing<br>Ambient                              | O <sub>2</sub>                                 | Formation of hafnium oxide/silicate.                                      | Can increase for HfSi <sub>2</sub> /Si interface.     | [5][7]    |

| N <sub>2</sub> /Ar                                | Promotes pure silicide formation.              | Generally lower than O <sub>2</sub> anneal.                               | [8][9]                                                |           |

| Forming Gas (N <sub>2</sub><br>+ H <sub>2</sub> ) | Passivates dangling bonds and interface traps. | Can be significantly reduced.                                             | -                                                     | _         |

| Surface<br>Preparation                            | HF last                                        | Removes native<br>SiO <sub>2</sub> , provides<br>H-terminated<br>surface. | Lower initial<br>defect density.                      | [1]       |

| UV Ozone Clean                                    | Removes organic contamination.                 | Reduces carbon-<br>related defects.                                       | [10]                                                  |           |

| HfO <sub>2</sub> Passivation<br>Layer             | 15 nm HfO₂ on<br>p-Si                          | Effective surface passivation.                                            | $3.6 \times 10^{10} \text{ cm}^{-2}$ $\text{eV}^{-1}$ | [11]      |

# Experimental Protocols Protocol 1: Silicon Substrate Surface Preparation

- · Solvent Cleaning:

- Place the silicon wafer in a beaker with acetone and sonicate for 10 minutes.

- Repeat the sonication step with isopropyl alcohol for 10 minutes.

- Rinse the wafer thoroughly with deionized (DI) water.

- Piranha Clean (for heavy organic contamination use with extreme caution):

- Prepare a Piranha solution by mixing sulfuric acid (H<sub>2</sub>SO<sub>4</sub>) and hydrogen peroxide (H<sub>2</sub>O<sub>2</sub>)

in a 3:1 ratio.

- Immerse the wafer in the Piranha solution for 10-15 minutes.

- o Rinse the wafer extensively with DI water.

- Native Oxide Removal (HF Dip):

- Immerse the wafer in a dilute hydrofluoric acid (HF) solution (e.g., 2% HF in DI water) for

60 seconds to etch the native SiO<sub>2</sub>.

- Quench the etch by placing the wafer in a beaker of DI water.

- Rinse thoroughly with DI water.

- Drying:

- Dry the wafer using a stream of high-purity nitrogen gas.

- Immediate Transfer:

- Immediately transfer the cleaned wafer into the deposition system to minimize re-oxidation of the silicon surface.

### **Protocol 2: Hafnium Deposition and Silicide Formation**

- Hafnium Deposition:

- Load the cleaned silicon substrate into a high-vacuum deposition chamber (e.g., sputtering or e-beam evaporation system).

- $\circ$  Evacuate the chamber to a base pressure of at least  $10^{-6}$  Torr.

- Deposit a thin film of hafnium (e.g., 10-50 nm) onto the silicon substrate at a controlled rate.

- Rapid Thermal Annealing (RTA):

- Transfer the Hf-coated silicon wafer to an RTA chamber.

- Purge the chamber with a high-purity inert gas (e.g., N₂ or Ar).

- Ramp up the temperature to the desired silicide formation temperature (e.g., 800°C for HfSi<sub>2</sub>).

- Hold the temperature for a specific duration (e.g., 30-120 seconds).

- Cool down the wafer in the inert ambient.

#### **Visualizations**

Click to download full resolution via product page

Experimental workflow for **hafnium silicide** formation.

Click to download full resolution via product page

#### **Need Custom Synthesis?**

BenchChem offers custom synthesis for rare earth carbides and specific isotopiclabeling.

Email: info@benchchem.com or Request Quote Online.

#### References

- 1. arxiv.org [arxiv.org]

- 2. pubs.aip.org [pubs.aip.org]

- 3. pubs.aip.org [pubs.aip.org]

- 4. researchgate.net [researchgate.net]

- 5. arxiv.org [arxiv.org]

- 6. scholar.nycu.edu.tw [scholar.nycu.edu.tw]

- 7. cpb.iphy.ac.cn [cpb.iphy.ac.cn]

- 8. researchgate.net [researchgate.net]

- 9. waseda.elsevierpure.com [waseda.elsevierpure.com]

- 10. par.nsf.gov [par.nsf.gov]

- 11. Frontiers | Silicon Passivation by Ultrathin Hafnium Oxide Layer for Photoelectrochemical Applications [frontiersin.org]

- To cite this document: BenchChem. [Technical Support Center: Minimizing Interface Defects Between Hafnium Silicide and Silicon]. BenchChem, [2025]. [Online PDF]. Available at: [https://www.benchchem.com/product/b077831#minimizing-interface-defects-between-hafnium-silicide-and-silicon]

#### **Disclaimer & Data Validity:**

The information provided in this document is for Research Use Only (RUO) and is strictly not intended for diagnostic or therapeutic procedures. While BenchChem strives to provide accurate protocols, we make no warranties, express or implied, regarding the fitness of this product for every specific experimental setup.

**Technical Support:** The protocols provided are for reference purposes. Unsure if this reagent suits your experiment? [Contact our Ph.D. Support Team for a compatibility check]

Need Industrial/Bulk Grade? Request Custom Synthesis Quote

## BenchChem

Our mission is to be the trusted global source of essential and advanced chemicals, empowering scientists and researchers to drive progress in science and industry.

#### Contact

Address: 3281 E Guasti Rd

Ontario, CA 91761, United States

Phone: (601) 213-4426

Email: info@benchchem.com