# Technical Support Center: Integrating TbPc2 into Electronic Circuits

Author: BenchChem Technical Support Team. Date: December 2025

For Researchers, Scientists, and Drug Development Professionals

This technical support center provides troubleshooting guidance and frequently asked questions (FAQs) to address common challenges encountered during the integration of Terbium(III) phthalocyanine (**TbPc**<sub>2</sub>) into electronic circuits.

# Section 1: Frequently Asked Questions (FAQs)

Q1: What are the primary challenges in fabricating high-quality **TbPc**<sup>2</sup> thin films?

A1: The primary challenges in fabricating high-quality **TbPc**<sup>2</sup> thin films revolve around controlling the film's morphology, crystal structure, and purity. Key issues include:

- Substrate Compatibility: The choice of substrate significantly influences the growth and orientation of TbPc<sub>2</sub> films. Different substrates can lead to variations in crystallinity and film morphology.

- Deposition Parameters: Achieving optimal film characteristics is highly dependent on deposition parameters such as substrate temperature, deposition rate, and vacuum pressure.

- Film Defects: Like many thin-film deposition processes, **TbPc**<sup>2</sup> films can suffer from defects such as pinholes, voids, and contamination, which can degrade device performance.[1][2]

Purity of Source Material: The purity of the TbPc2 powder used for deposition is critical.

Impurities can be incorporated into the thin film, affecting its electronic and magnetic properties.

Q2: How does the morphology of the **TbPc**<sup>2</sup> film affect device performance?

A2: The morphology of the **TbPc**<sup>2</sup> thin film, including grain size and molecular orientation, has a profound impact on charge transport and overall device performance.[3][4] A well-ordered film with large, interconnected crystalline grains generally leads to higher carrier mobility. Conversely, an amorphous or disordered film with many grain boundaries can trap charge carriers and reduce conductivity. The orientation of the **TbPc**<sup>2</sup> molecules relative to the substrate also plays a crucial role in determining the electronic coupling and charge injection efficiency at the interface.

Q3: What are the common causes of high contact resistance in **TbPc**<sub>2</sub>-based devices?

A3: High contact resistance is a frequent issue in molecular electronic devices and can stem from several factors:

- Interface Contamination: The presence of a thin insulating layer or contaminants at the interface between the TbPc2 film and the metal electrode can significantly impede charge injection.

- Energy Level Mismatch: A significant energy barrier between the work function of the electrode material and the molecular orbitals of **TbPc**<sup>2</sup> can lead to poor charge injection, resulting in high contact resistance.

- Poor Adhesion: Weak adhesion between the **TbPc**<sup>2</sup> film and the electrode can result in a physically discontinuous interface, limiting the effective contact area.[5]

- Film Thickness: The thickness of the **TbPc**<sup>2</sup> film can also influence the contact resistance.

Q4: What are the typical degradation mechanisms for **TbPc**<sub>2</sub>-based electronic devices?

A4: Degradation of **TbPc**<sup>2</sup> devices can occur through several mechanisms, leading to a decline in performance over time. These include:

- Oxidation: Exposure to air and moisture can lead to the oxidation of the TbPc2 molecules or the electrodes, altering their electronic properties.

- Electromigration: Under high current densities, metal atoms from the electrodes can migrate into the **TbPc**<sup>2</sup> layer, creating shorts or altering the device characteristics.

- Thermal Stress: Repeated thermal cycling can induce stress in the thin film, leading to cracking or delamination.

- Interfacial Reactions: Chemical reactions at the interface between **TbPc**<sup>2</sup> and the substrate or electrodes can lead to the formation of new, often insulating, layers.

# **Section 2: Troubleshooting Guides**

This section provides practical troubleshooting steps for common issues encountered during the fabrication and characterization of **TbPc**<sub>2</sub>-based electronic devices.

### **Guide 1: Poor Thin Film Quality**

# Troubleshooting & Optimization

Check Availability & Pricing

| Symptom                              | Possible Causes                                                                                                             | Troubleshooting Steps                                                                                                                                                                                                                                                               |

|--------------------------------------|-----------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Non-uniform film thickness           | - Inconsistent deposition rate-<br>Sub-optimal substrate-to-<br>source distance- Uneven<br>substrate heating                | - Calibrate and stabilize the deposition source Optimize the distance between the source and the substrate Ensure uniform temperature distribution across the substrate holder.                                                                                                     |

| High density of pinholes or voids    | - Contamination on the substrate- Particulate contamination in the deposition chamber- Inappropriate deposition temperature | - Implement a thorough substrate cleaning procedure Maintain a clean deposition environment Optimize the substrate temperature to enhance adatom mobility and promote denser film growth.[1]                                                                                        |

| Poor film adhesion                   | - Incompatible substrate<br>material- Surface<br>contamination- Internal stress<br>in the film                              | - Select a substrate with good surface energy matching for TbPc2 Utilize plasma cleaning or other surface treatments to improve adhesion Optimize deposition parameters to minimize film stress.[5]                                                                                 |

| Amorphous or poorly crystalline film | - Substrate temperature too<br>low- Deposition rate too high-<br>Unsuitable substrate                                       | - Increase the substrate temperature to provide more thermal energy for crystallization Reduce the deposition rate to allow more time for molecules to arrange in an ordered structure Experiment with different substrates known to promote crystalline growth of phthalocyanines. |

# **Guide 2: Device Performance Issues**

| Symptom                                   | Possible Causes                                                                                             | Troubleshooting Steps                                                                                                                                                                                                            |

|-------------------------------------------|-------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Low charge carrier mobility               | - Disordered film morphology-<br>High density of traps at grain<br>boundaries- Poor contact<br>quality      | - Optimize deposition parameters (substrate temperature, deposition rate) to improve film crystallinity and grain size Consider post- deposition annealing to improve film order See Troubleshooting Guide 3 for contact issues. |

| High off-state current (low on/off ratio) | - Presence of impurities in the TbPc2 film- Gate leakage through the dielectric layer-Short channel effects | - Use high-purity TbPc2 source material Verify the integrity and thickness of the gate dielectric Optimize device geometry to mitigate short channel effects.                                                                    |

| Device instability or rapid degradation   | - Exposure to oxygen and<br>moisture- Electromigration at<br>the contacts- Delamination of<br>layers        | - Encapsulate the device to protect it from the ambient environment Use more stable electrode materials Improve adhesion between layers.                                                                                         |

## **Guide 3: Electrical Measurement Problems**

| Symptom                             | Possible Causes                                                                                                                                                    | Troubleshooting Steps                                                                                                                                                                                     |

|-------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| No measurable current               | - Open circuit in the device<br>(e.g., cracked film or<br>electrode)- Faulty electrical<br>connection to the<br>measurement setup- Very high<br>contact resistance | - Visually inspect the device for any physical damage Check the integrity of all electrical connections and probes Fabricate devices with different electrode materials or use a contact treatment layer. |

| Short circuit                       | - Pinholes in the dielectric layer- Metal penetration through the organic film-Contamination causing a conductive path                                             | - Improve the quality of the dielectric deposition Optimize the metal deposition process to prevent "punch-through" Ensure a clean fabrication environment.                                               |

| Noisy or unstable electrical signal | - Poor grounding of the<br>measurement setup- External<br>electromagnetic interference-<br>Intrinsic noise from the device                                         | - Ensure proper grounding of<br>all equipment Use a shielded<br>probe station Perform<br>measurements at different<br>temperatures to identify the<br>source of noise.                                    |

# Section 3: Experimental Protocols Protocol 1: TbPc2 Thin Film Deposition via Organic Molecular Beam Epitaxy (OMBE)

- Substrate Preparation:

- Select a suitable substrate (e.g., Si/SiO<sub>2</sub>, glass, or single-crystal substrates).

- Clean the substrate sequentially in an ultrasonic bath with acetone, isopropanol, and deionized water.

- Dry the substrate with a stream of dry nitrogen gas.

- For Si/SiO<sub>2</sub> substrates, a final oxygen plasma treatment can be used to remove any remaining organic residues.

- Source Material Preparation:

- Use high-purity TbPc₂ powder (≥99.9%).

- Degas the **TbPc**<sup>2</sup> powder in a Knudsen cell inside the OMBE chamber at a temperature below the sublimation point for several hours to remove adsorbed water and other volatile impurities.

- Deposition Process:

- Mount the cleaned substrate onto the sample holder in the OMBE chamber.

- Evacuate the chamber to a base pressure of  $< 1 \times 10^{-8}$  Torr.

- Heat the substrate to the desired deposition temperature (typically in the range of 150-300 °C).

- Gradually heat the Knudsen cell containing the **TbPc**<sup>2</sup> powder to its sublimation temperature.

- Monitor the deposition rate using a quartz crystal microbalance. A typical deposition rate is 0.1-0.5 Å/s.

- Deposit the TbPc<sub>2</sub> film to the desired thickness.

- After deposition, cool down the substrate and the Knudsen cell to room temperature before venting the chamber.

# Protocol 2: Device Fabrication - Top-Contact, Bottom-Gate Thin-Film Transistor (TFT)

- Substrate and Gate Electrode:

- Start with a heavily doped silicon wafer (p<sup>++</sup>-Si) which acts as the gate electrode, with a thermally grown silicon dioxide (SiO<sub>2</sub>) layer (typically 200-300 nm) as the gate dielectric.

- TbPc2 Deposition:

- Deposit the **TbPc**<sup>2</sup> thin film onto the SiO<sub>2</sub>/Si substrate using the OMBE protocol described above. The film thickness is typically in the range of 30-50 nm.

- Source and Drain Electrode Deposition:

- Use a shadow mask to define the source and drain electrode patterns.

- Deposit the electrode material (e.g., Gold) through the shadow mask using thermal evaporation. The electrode thickness is typically 50-100 nm. The channel length and width are defined by the shadow mask dimensions.

**Section 4: Visualizations**

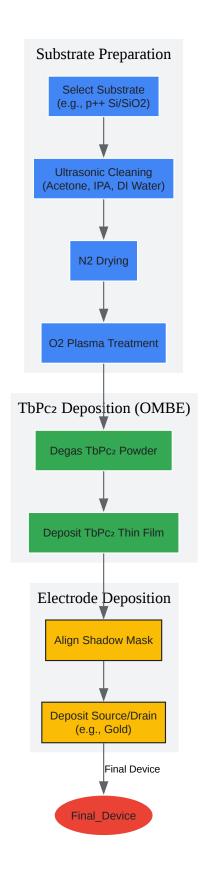

Diagram 1: Experimental Workflow for TbPc2 TFT

**Fabrication**

Click to download full resolution via product page

A flowchart illustrating the key steps in fabricating a top-contact, bottom-gate **TbPc**<sup>2</sup> thin-film transistor.

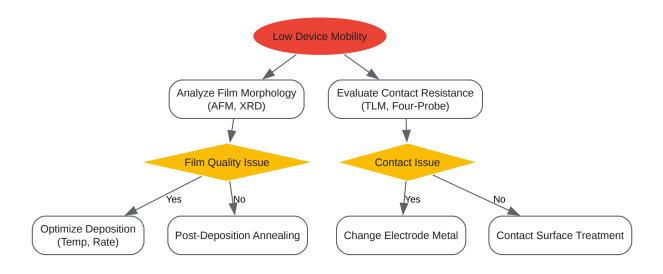

# Diagram 2: Troubleshooting Logic for Low Device Mobility

Click to download full resolution via product page

A decision tree for troubleshooting low charge carrier mobility in **TbPc**<sub>2</sub>-based electronic devices.

#### **Need Custom Synthesis?**

BenchChem offers custom synthesis for rare earth carbides and specific isotopiclabeling.

Email: info@benchchem.com or Request Quote Online.

### References

- 1. plexbio.com [plexbio.com]

- 2. researchgate.net [researchgate.net]

- 3. ruben-group.de [ruben-group.de]

- 4. bdt.semi.ac.cn [bdt.semi.ac.cn]

- 5. researchgate.net [researchgate.net]

- 6. buyat.ppg.com [buyat.ppg.com]

- To cite this document: BenchChem. [Technical Support Center: Integrating TbPc₂ into Electronic Circuits]. BenchChem, [2025]. [Online PDF]. Available at: [https://www.benchchem.com/product/b1634351#challenges-in-integrating-tbpc-intoelectronic-circuits]

### **Disclaimer & Data Validity:**

The information provided in this document is for Research Use Only (RUO) and is strictly not intended for diagnostic or therapeutic procedures. While BenchChem strives to provide accurate protocols, we make no warranties, express or implied, regarding the fitness of this product for every specific experimental setup.

**Technical Support:** The protocols provided are for reference purposes. Unsure if this reagent suits your experiment? [Contact our Ph.D. Support Team for a compatibility check]

Need Industrial/Bulk Grade? Request Custom Synthesis Quote

# BenchChem

Our mission is to be the trusted global source of essential and advanced chemicals, empowering scientists and researchers to drive progress in science and industry.

#### Contact

Address: 3281 E Guasti Rd

Ontario, CA 91761, United States

Phone: (601) 213-4426

Email: info@benchchem.com