# Technical Support Center: Improving SiC Wafer Processing and Yield

Author: BenchChem Technical Support Team. Date: December 2025

| Compound of Interest |                 |           |

|----------------------|-----------------|-----------|

| Compound Name:       | Silicon carbide |           |

| Cat. No.:            | B1214593        | Get Quote |

This technical support center provides troubleshooting guides and frequently asked questions (FAQs) to assist researchers, scientists, and drug development professionals in optimizing their silicon carbide (SiC) wafer processing experiments to enhance yield and minimize defects.

## **Troubleshooting Guides**

This section provides solutions to common problems encountered during SiC wafer processing.

1. Crystallographic Defects

Question: What are the common crystallographic defects in SiC wafers and how can they be minimized?

#### Answer:

Crystallographic defects are disruptions in the perfect crystal lattice of the SiC wafer. They are often initiated during crystal growth and can propagate through subsequent processing steps, significantly impacting device performance and yield.[1][2] Key crystallographic defects include:

- Micropipes: These are hollow tube-like defects that can extend through the entire wafer.

They are considered "killer defects" as they cause device failure.[1]

- Troubleshooting:

- Optimize the physical vapor transport (PVT) growth process by controlling the temperature gradient and pressure.

- Use high-quality seed crystals with low defect densities.

- Threading Screw Dislocations (TSDs) and Threading Edge Dislocations (TEDs): These are

line defects that propagate through the crystal. TSDs are more detrimental to device

performance than TEDs.[1][3] The typical density of TEDs is significantly higher than that of

TSDs.[1]

- Troubleshooting:

- Careful control of the initial stages of crystal growth is crucial.

- Employing advanced growth techniques like High-Temperature Chemical Vapor Deposition (HTCVD) can reduce dislocation densities.

- Basal Plane Dislocations (BPDs): These dislocations lie on the basal plane of the SiC crystal. While less harmful than micropipes, they can degrade the performance of certain devices.[1]

- Troubleshooting:

- BPDs can be converted to less harmful TEDs through specific epitaxial growth processes.

- Increasing the thickness of the SiC substrate has been shown to reduce BPD density.[1]

- Stacking Faults (SFs): These are errors in the stacking sequence of the SiC atomic layers.

They can be introduced during crystal growth or subsequent processing steps like epitaxy and ion implantation.

- Troubleshooting:

- Precise control over the C/Si ratio during epitaxial growth is critical.

- Post-implantation annealing at high temperatures is necessary to repair crystal damage and reduce stacking faults.

#### 2. Surface Defects and Contamination

Question: My processed SiC wafers show a high density of surface defects. What are the likely causes and how can I improve the surface quality?

#### Answer:

Surface defects are imperfections on the wafer surface that can arise from various processing steps, including polishing, cleaning, and handling. Common surface defects include:

- Scratches: These are mechanical damages typically introduced during wafer handling, grinding, lapping, or chemical mechanical polishing (CMP).[1][4] Scratches can act as nucleation sites for other defects during subsequent epitaxial growth.[1]

- Troubleshooting:

- Ensure proper wafer handling protocols are followed, using appropriate tools and minimizing manual contact.[4]

- Optimize the CMP process by selecting the appropriate polishing pad, slurry, and process parameters.

- Inspect wafers for scratches after each mechanical processing step.

- Surface Pits and Bumps: These can be caused by issues during epitaxial growth or incomplete removal of polishing damage.

- Troubleshooting:

- Optimize epitaxial growth conditions such as temperature, pressure, and gas flow rates.

- Ensure the CMP process effectively removes all subsurface damage from grinding and lapping.

- Particulate Contamination: Particles on the wafer surface can originate from the processing environment, equipment, or chemicals.

- Troubleshooting:

- Perform all processing in a cleanroom environment with appropriate air filtration.

- Implement rigorous cleaning procedures for all equipment and wafer handling tools.

- Use high-purity chemicals and gases.

- Organic and Metallic Contamination: Residues from photoresists, cleaning solvents, or handling can adversely affect device performance.

- Troubleshooting:

- Employ standardized cleaning protocols such as the RCA clean to effectively remove organic and metallic contaminants.

- Use high-purity solvents and acids for cleaning.

- 3. Chemical Mechanical Polishing (CMP) Issues

Question: I am experiencing low material removal rates (MRR) and high surface roughness after CMP of my SiC wafers. How can I optimize the process?

#### Answer:

Chemical Mechanical Polishing (CMP) is a critical step for achieving an atomically smooth and damage-free SiC surface. However, due to the hardness and chemical inertness of SiC, achieving high MRR and low surface roughness can be challenging.

- Low Material Removal Rate (MRR):

- Troubleshooting:

- Slurry Composition: The choice of abrasive (e.g., alumina, silica) and its concentration, as well as the pH and type of oxidizer in the slurry, significantly impact MRR.[5]

- Process Parameters: Increasing the polishing pressure and platen rotational speed can enhance the MRR.

- Polishing Pad: The type of polishing pad (e.g., polyurethane) and its conditioning are crucial for maintaining a consistent removal rate. Softer pads may lead to lower MRR.

- High Surface Roughness (Ra):

- Troubleshooting:

- Abrasive Particle Size: Using a slurry with a smaller and more uniform abrasive particle size can lead to lower surface roughness.

- Polishing Pad: Harder pads generally result in better planarization but can cause higher defectivity if not optimized. The choice of pad material can significantly impact the final surface finish.[6]

- Final Polishing Step: A final, gentle polishing step with a low-abrasive or abrasive-free slurry can be used to achieve an ultra-smooth surface.

## Frequently Asked Questions (FAQs)

#### **Epitaxial Growth**

- Q1: What is the purpose of an off-axis substrate for SiC epitaxial growth?

- A1: Using a substrate cut at a slight angle (typically 4°) to the crystal's basal plane promotes step-flow growth. This technique helps to replicate the crystal structure of the substrate in the grown epitaxial layer, reducing the formation of certain defects like 3C-SiC polytype inclusions in 4H-SiC epitaxy.[2]

- Q2: How does the C/Si ratio affect the quality of the epitaxial layer?

- A2: The ratio of carbon to silicon precursor gases during CVD is a critical parameter. A

C/Si ratio of approximately 0.72 has been shown to result in a smoother surface with fewer defects.

An improper C/Si ratio can lead to the formation of surface morphological defects.

#### Wafer Cleaning

Q3: What is the RCA clean and why is it important for SiC wafers?

- A3: The RCA clean is a two-step wet chemical cleaning process designed to remove organic contaminants (SC-1) and metallic impurities (SC-2).[8][9] It is crucial for preparing a clean SiC wafer surface before high-temperature processes like oxidation and epitaxy, as any contaminants can lead to defects and poor device performance.[9]

- Q4: Can I use the same cleaning procedure for Si and SiC wafers?

- A4: While the principles of wafer cleaning are similar, the chemical resistance and surface properties of SiC differ from silicon. Therefore, cleaning processes should be optimized specifically for SiC to ensure effective contaminant removal without damaging the wafer surface.

#### Annealing

- Q5: What is the purpose of post-implantation annealing for SiC?

- A5: Ion implantation, used for doping SiC, causes significant damage to the crystal lattice.

High-temperature annealing (typically above 1600°C) is essential to repair this damage,

electrically activate the implanted dopants, and reduce the formation of secondary defects.

[10]

- Q6: What are the different types of annealing techniques used for SiC?

- A6: Several annealing methods are used, including furnace annealing, rapid thermal annealing (RTA), laser annealing, and microwave annealing.[11] The choice of technique depends on the specific application, such as dopant activation or ohmic contact formation.

[11]

#### Wafer Handling and Storage

- Q7: What are the best practices for handling and storing SiC wafers?

- A7: SiC wafers are brittle and susceptible to contamination.[12] They should be handled only by their edges using clean, non-metallic tweezers.[12] Storage should be in a clean, dry environment, typically within a nitrogen-purged desiccator or a dedicated wafer carrier, to prevent moisture and particulate contamination.[13] The recommended storage temperature is between 18-25°C with a relative humidity of 30-50%.[14]

## **Quantitative Data Tables**

Table 1: Typical Defect Densities in Different Grades of 4H-SiC Wafers

| Defect Type                       | Dummy Grade Wafer<br>(cm <sup>-2</sup> ) | Production Grade Wafer<br>(cm <sup>-2</sup> ) |

|-----------------------------------|------------------------------------------|-----------------------------------------------|

| Micropipe (MP)                    | Present                                  | Very Low to Zero                              |

| Threading Screw Dislocation (TSD) | ~10³ - 10⁴                               | < 10 <sup>3</sup>                             |

| Threading Edge Dislocation (TED)  | ~104 - 105                               | < 104                                         |

| Basal Plane Dislocation (BPD)     | ~10³ - 10⁴                               | < 103                                         |

Data synthesized from multiple sources indicating typical ranges.[1][3]

Table 2: Example of CMP Process Parameters and Their Impact on 4H-SiC (Si-face)

| Parameter | Slurry<br>Compositio<br>n                    | Polishing<br>Pressure<br>(PSI) | Platen<br>Speed<br>(RPM) | Resulting<br>MRR<br>(µm/hr) | Resulting<br>Surface<br>Roughness<br>(Ra, nm) |

|-----------|----------------------------------------------|--------------------------------|--------------------------|-----------------------------|-----------------------------------------------|

| Process A | Alumina-<br>based, pH 4,<br>5 wt%<br>Oxidant | 5                              | 60                       | 1.2                         | 0.093                                         |

| Process B | Colloidal<br>Silica                          | 4                              | 50                       | ~0.5                        | < 0.1                                         |

| Process C | Diamond-<br>based slurry                     | 6                              | 70                       | > 5                         | < 0.2                                         |

This table presents illustrative data from various studies to show the impact of different CMP parameters. Actual results will vary based on specific experimental conditions.[5][15]

## **Experimental Protocols**

1. Molten KOH Etching for Defect Delineation

This protocol is used to reveal crystallographic defects on the SiC wafer surface for inspection.

- Materials:

- SiC wafer sample

- Potassium hydroxide (KOH) pellets

- Nickel or platinum crucible

- High-temperature furnace

- Deionized (DI) water

- Nitrogen gas for purging

- Procedure:

- Place the SiC wafer sample in the crucible.

- Add KOH pellets to the crucible, ensuring the sample will be fully immersed when the KOH is molten.

- Place the crucible in the furnace.

- Heat the furnace to the desired etching temperature (typically 450-500°C) under a nitrogen atmosphere.

- Hold at the etching temperature for a specific duration (e.g., 10-30 minutes). The etching time will depend on the desired etch depth.

- After etching, cool down the furnace.

- Carefully remove the crucible and allow it to cool to room temperature.

- Rinse the wafer thoroughly with DI water to remove any residual KOH.

- Dry the wafer using a nitrogen gun.

- Inspect the wafer surface using an optical microscope or scanning electron microscope

(SEM) to identify the revealed defect etch pits.

#### 2. Standard RCA Clean for SiC Wafers

This protocol is a standard method for removing organic and metallic contaminants.

- Materials:

- SiC wafers

- SC-1 solution: 5 parts DI water, 1 part 27% ammonium hydroxide (NH<sub>4</sub>OH), 1 part 30% hydrogen peroxide (H<sub>2</sub>O<sub>2</sub>)

- SC-2 solution: 6 parts DI water, 1 part 37% hydrochloric acid (HCl), 1 part 30% hydrogen peroxide (H<sub>2</sub>O<sub>2</sub>)

- Hydrofluoric acid (HF) solution (e.g., 2% HF)

- Teflon wafer carrier

- Heated quartz baths

- DI water rinse tank

- Procedure:

- SC-1 Clean (Organic Removal):

- Prepare the SC-1 solution in a quartz bath and heat to 70-80°C.

- Immerse the SiC wafers in the Teflon carrier into the SC-1 solution for 10-15 minutes.[8]

- Rinse the wafers thoroughly in a DI water overflow bath for 5-10 minutes.

- o (Optional) HF Dip:

- To remove the thin native oxide layer, dip the wafers in a 2% HF solution for 1-2 minutes at room temperature.

- Rinse thoroughly with DI water.

- SC-2 Clean (Metallic Removal):

- Prepare the SC-2 solution in a separate quartz bath and heat to 70-80°C.

- Immerse the wafers into the SC-2 solution for 10-15 minutes.

- Rinse the wafers thoroughly in a DI water overflow bath for 5-10 minutes.

- Final Rinse and Dry:

- Perform a final rinse in high-purity DI water.

- Dry the wafers using a spin rinse dryer or a nitrogen gun.

## **Visualizations**

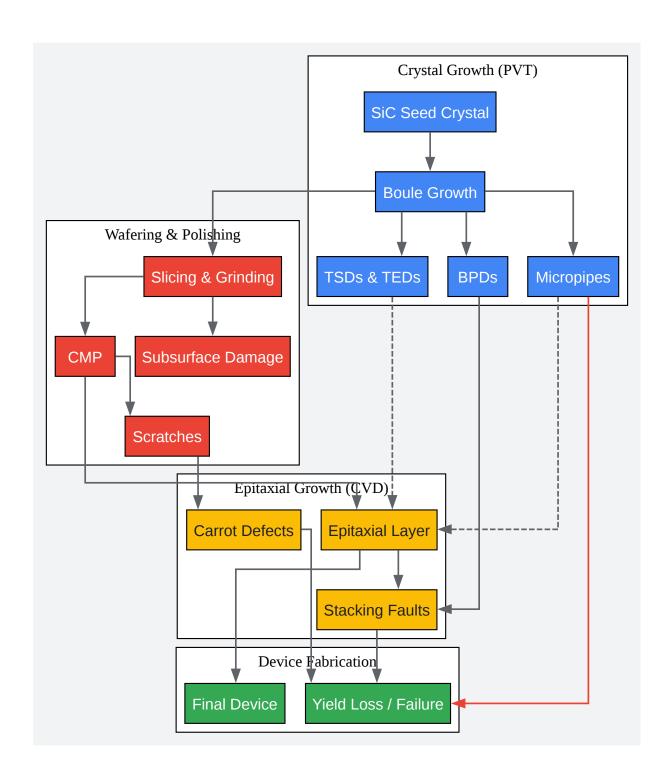

Click to download full resolution via product page

Caption: Propagation of defects through SiC wafer processing stages.

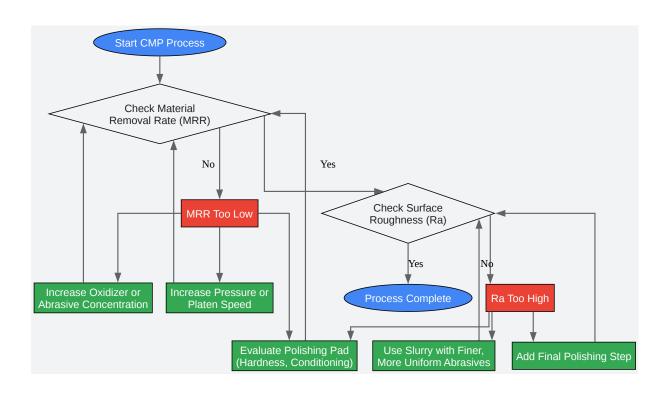

Click to download full resolution via product page

Caption: Troubleshooting workflow for SiC Chemical Mechanical Polishing.

#### **Need Custom Synthesis?**

BenchChem offers custom synthesis for rare earth carbides and specific isotopiclabeling.

Email: info@benchchem.com or Request Quote Online.

### References

- 1. Defect Inspection Techniques in SiC PMC [pmc.ncbi.nlm.nih.gov]

- 2. pubs.aip.org [pubs.aip.org]

- 3. sensors.myu-group.co.jp [sensors.myu-group.co.jp]

- 4. foamtecintlwcc.com [foamtecintlwcc.com]

- 5. mdpi.com [mdpi.com]

- 6. researchgate.net [researchgate.net]

- 7. mdpi.com [mdpi.com]

- 8. inrf.uci.edu [inrf.uci.edu]

- 9. biolinscientific.com [biolinscientific.com]

- 10. warse.org [warse.org]

- 11. A Breakdown of Wafer Annealing Methods [waferworld.com]

- 12. universitywafer.com [universitywafer.com]

- 13. Mastering Silicon Wafer Handling and Storage in Semiconductor Facilities [waferworld.com]

- 14. waferpro.com [waferpro.com]

- 15. mdpi.com [mdpi.com]

- To cite this document: BenchChem. [Technical Support Center: Improving SiC Wafer Processing and Yield]. BenchChem, [2025]. [Online PDF]. Available at: [https://www.benchchem.com/product/b1214593#improving-sic-wafer-processing-and-yield]

#### **Disclaimer & Data Validity:**

The information provided in this document is for Research Use Only (RUO) and is strictly not intended for diagnostic or therapeutic procedures. While BenchChem strives to provide accurate protocols, we make no warranties, express or implied, regarding the fitness of this product for every specific experimental setup.

**Technical Support:**The protocols provided are for reference purposes. Unsure if this reagent suits your experiment? [Contact our Ph.D. Support Team for a compatibility check]

Need Industrial/Bulk Grade? Request Custom Synthesis Quote

## BenchChem

Our mission is to be the trusted global source of essential and advanced chemicals, empowering scientists and researchers to drive progress in science and industry. Contact

Address: 3281 E Guasti Rd

Ontario, CA 91761, United States

Phone: (601) 213-4426

Email: info@benchchem.com