Check Availability & Pricing

# Technical Support Center: Gallium Arsenide (GaAs) Transistor Performance Enhancement

Author: BenchChem Technical Support Team. Date: December 2025

| Compound of Interest |                  |           |

|----------------------|------------------|-----------|

| Compound Name:       | Gallium arsenide |           |

| Cat. No.:            | B074776          | Get Quote |

This technical support center provides troubleshooting guides and frequently asked questions (FAQs) to assist researchers, scientists, and drug development professionals in optimizing the performance of **gallium arsenide**-based transistors during their experiments.

## Frequently Asked Questions (FAQs)

Q1: What are the most common factors limiting the performance of our GaAs transistors?

A1: The performance of **Gallium Arsenide** (GaAs) transistors is often limited by a few key factors. High contact resistance at the source and drain terminals can significantly impede current flow and reduce overall device efficiency.[1] Surface-related issues, such as a high density of surface states, can lead to Fermi level pinning, increased surface recombination, and consequently, lower gain and higher noise.[2][3] Additionally, the inherent properties of GaAs, such as its relatively low thermal conductivity, can lead to self-heating effects that degrade performance, especially in high-power applications.[4][5] Degradation of the gate contact, sometimes referred to as "gate sinking," where the gate metal diffuses into the semiconductor, can also be a significant failure mechanism.

Q2: We are observing a high contact resistance in our devices. What are the likely causes and how can we mitigate this?

A2: High contact resistance in GaAs transistors is a common issue that can often be traced back to the formation of the ohmic contacts. The interface between the metal stack (commonly Au-Ge-Ni based) and the GaAs substrate is critical. An incomplete or non-uniform reaction

### Troubleshooting & Optimization

during the annealing process can leave behind a resistive layer. The annealing temperature and duration are crucial parameters; suboptimal values can lead to poor contact quality.[6][7] Surface preparation before metal deposition is also vital. Any residual native oxide on the GaAs surface can inhibit the formation of a low-resistance ohmic contact.

To mitigate this, it is essential to optimize the annealing process. This involves finding the ideal temperature and time for the specific metal stack and GaAs structure being used.[7][8] Additionally, ensuring a thorough surface cleaning and oxide removal step immediately before loading the samples into the deposition chamber is critical for achieving a good metal-semiconductor interface.

Q3: Our transistors show low gain and high noise. Could surface passivation help, and what are the recommended methods?

A3: Yes, surface passivation is a highly effective method for addressing issues of low gain and high noise in GaAs transistors. These problems are often caused by a high density of surface states that trap charge carriers and act as recombination centers.[2][3] Passivation aims to chemically treat the GaAs surface to reduce these detrimental states.

Several passivation techniques have proven effective. Sulfur-based treatments, using solutions like ammonium sulfide ((NH<sub>4</sub>)<sub>2</sub>S) or sodium sulfide (Na<sub>2</sub>S), are widely used and have been shown to significantly improve the electronic properties of the GaAs surface.[2][9] Another approach is the deposition of a dielectric layer, such as silicon nitride (SiN) or aluminum oxide (Al<sub>2</sub>O<sub>3</sub>), often using techniques like Plasma-Enhanced Chemical Vapor Deposition (PECVD). More recent methods also include wet nitridation.[10] The choice of passivation method will depend on the specific device structure and the available processing capabilities.

Q4: We are experiencing a gradual degradation in transistor performance over time, especially at elevated temperatures. What could be the cause?

A4: The gradual degradation of GaAs transistor performance, particularly at higher temperatures, is often due to solid-state diffusion and intermixing of the contact metals with the underlying GaAs substrate.[11] This can lead to a degradation of both the ohmic and Schottky contacts. For instance, the out-diffusion of Gallium (Ga) into the metal contacts can alter the stoichiometry of the GaAs near the interface and adversely affect device performance.[11][12] This is a common wear-out mechanism in GaAs devices. To minimize this, it is important to use

thermally stable metallization schemes and to operate the devices within their specified temperature limits.

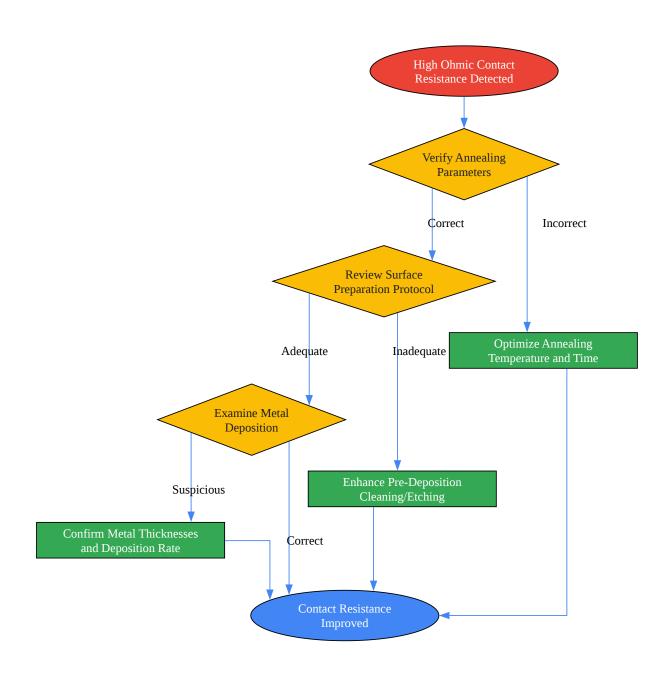

## **Troubleshooting Guides Issue 1: High Ohmic Contact Resistance**

This guide provides a systematic approach to troubleshooting and resolving high ohmic contact resistance in GaAs transistors.

#### Symptoms:

- High source and drain resistance.

- Low drain current.

- Poor overall device performance.

Troubleshooting Workflow:

Click to download full resolution via product page

Troubleshooting Workflow for High Ohmic Contact Resistance.

#### **Experimental Protocols:**

- Protocol for Optimizing Annealing of Au-Ge-Ni Ohmic Contacts:

- Prepare a series of identical GaAs samples with the deposited Au-Ge-Ni metal stack.

- Use a rapid thermal annealing (RTA) system.

- Anneal the samples at a range of temperatures (e.g., 380°C to 450°C) for a fixed duration (e.g., 60 seconds).[6]

- For the optimal temperature, anneal another set of samples for varying durations (e.g., 30 to 120 seconds).

- Measure the contact resistance for each sample using the Transmission Line Model (TLM).

- Plot contact resistance versus annealing temperature and time to determine the optimal process window.

- Protocol for Surface Preparation prior to Metal Deposition:

- Degrease the GaAs wafer using standard solvents (e.g., acetone, isopropanol).

- Perform a native oxide etch using a solution such as hydrochloric acid (HCl) or ammonium hydroxide (NH<sub>4</sub>OH). A common procedure is to dip the sample in a HCl:H<sub>2</sub>O (1:1) solution for 1 minute.[13]

- Rinse thoroughly with deionized (DI) water.

- Dry the sample with a nitrogen gun.

- Immediately load the sample into the vacuum chamber for metal deposition to minimize re-oxidation of the surface.

#### Quantitative Data:

| Annealing Temperature (°C) | Specific Contact Resistivity (Ω·cm²) with Ni/Ge/Ni/Au |

|----------------------------|-------------------------------------------------------|

| 370                        | Schottky Contact                                      |

| 380                        | Ohmic, but high resistance                            |

| 420                        | $3.3 \times 10^{-5}$                                  |

| 430                        | Increased resistance                                  |

Table 1: Effect of annealing temperature on the specific contact resistivity of a Ni/Ge/Ni/Au multilayer on n-GaAs.[6]

| Annealing Temperature (°C) | Au/Ge/Ni/Au Contact<br>Resistivity (Ω·cm²) | Pd/Ge/Ti/Au Contact<br>Resistivity (Ω·cm²) |

|----------------------------|--------------------------------------------|--------------------------------------------|

| 300                        | High                                       | High                                       |

| 400                        | 5.0 x 10 <sup>-5</sup>                     | Moderate                                   |

| 450                        | 2.0 x 10 <sup>-6</sup>                     | Low                                        |

| 500                        | Increased                                  | Increased                                  |

Table 2: Comparison of contact resistivity for different metallization schemes on an AlGaAs/InGaAs PHEMT structure at various annealing temperatures.[8]

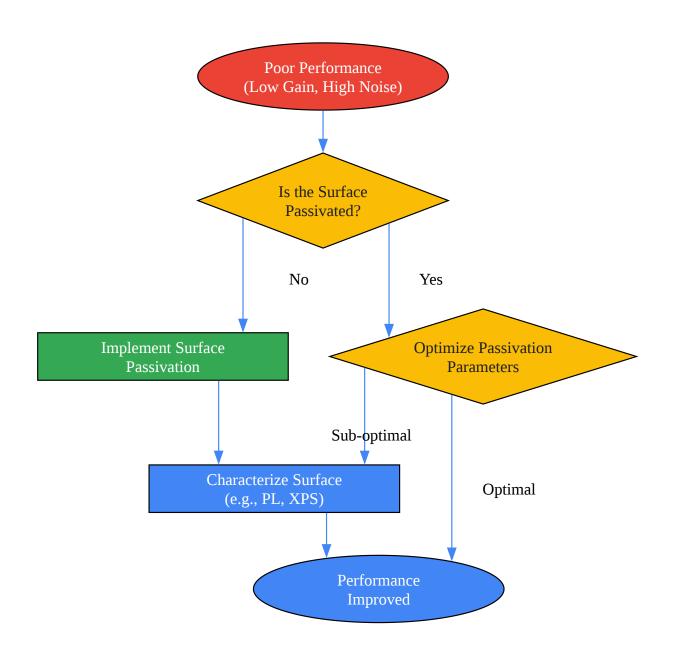

## Issue 2: Poor Transistor Performance due to Surface Effects

This guide outlines steps to diagnose and remedy performance issues related to the GaAs surface.

#### Symptoms:

- Low transistor gain (transconductance).

- High noise figure.

• Drift in drain current over time.[12]

Troubleshooting Workflow:

Click to download full resolution via product page

Troubleshooting Workflow for Surface-Related Performance Issues.

#### **Experimental Protocols:**

- Protocol for Ammonium Sulfide ((NH<sub>4</sub>)<sub>2</sub>S) Passivation:

- Begin with a clean GaAs sample (native oxide removed as described previously).

- Immerse the sample in a solution of (NH₄)₂S. The concentration and presence of excess sulfur can be varied.

- The immersion time can range from a few minutes to several hours at room temperature.

- After immersion, rinse the sample with DI water and dry with nitrogen.

- For improved stability, a subsequent annealing step in a nitrogen atmosphere may be performed.

- Protocol for SF<sub>6</sub> Plasma Passivation:

- Place the GaAs sample in a radio frequency (RF) plasma system.

- Introduce SF<sub>6</sub> gas into the chamber.

- Optimize the RF power, chamber pressure, and treatment time. A typical starting point could be a 5-minute treatment.[14]

- After treatment, a thin layer of SiO<sub>2</sub> can be deposited to enhance the stability of the passivation layer.[14]

#### Quantitative Data:

| Passivation Method                | Carrier Lifetime<br>Improvement                                          | Reference |

|-----------------------------------|--------------------------------------------------------------------------|-----------|

| Unpassivated (annealed LT:GaAs)   | ~2 ps                                                                    | [15]      |

| Unpassivated (unannealed LT:GaAs) | <200 fs                                                                  | [15]      |

| Wet Nitridation                   | Hole-trapping rate reduced by 2.6x, electron-trapping rate reduced by 3x | [10]      |

| SF <sub>6</sub> Plasma Treatment  | Photoluminescence intensity increased by ~1.8 times                      | [14]      |

Table 3: Comparison of the effectiveness of different passivation techniques on carrier lifetime and photoluminescence.

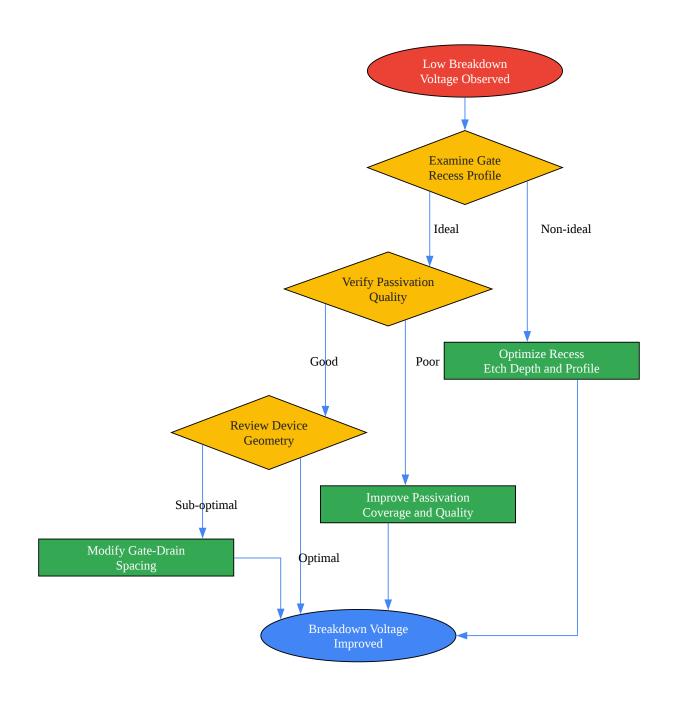

### **Issue 3: Low Breakdown Voltage**

This guide addresses the issue of premature breakdown in GaAs transistors.

#### Symptoms:

- Sharp increase in drain current at a lower than expected drain-source voltage.

- Catastrophic device failure at high voltage bias.

Troubleshooting Workflow:

Click to download full resolution via product page

#### **Need Custom Synthesis?**

BenchChem offers custom synthesis for rare earth carbides and specific isotopiclabeling.

Email: info@benchchem.com or Request Quote Online.

### References

- 1. opticaapplicata.pwr.edu.pl [opticaapplicata.pwr.edu.pl]

- 2. chalcogen.ro [chalcogen.ro]

- 3. BJNANO Impact of GaAs(100) surface preparation on EQE of AZO/Al2O3/p-GaAs photovoltaic structures [beilstein-journals.org]

- 4. Common Problems With GaAs Wafers | Wafer World [waferworld.com]

- 5. microwavejournal.com [microwavejournal.com]

- 6. researchgate.net [researchgate.net]

- 7. researchgate.net [researchgate.net]

- 8. jkps.or.kr [jkps.or.kr]

- 9. researchgate.net [researchgate.net]

- 10. pubs.acs.org [pubs.acs.org]

- 11. mdpi.com [mdpi.com]

- 12. apps.dtic.mil [apps.dtic.mil]

- 13. docs.lib.purdue.edu [docs.lib.purdue.edu]

- 14. mdpi.com [mdpi.com]

- 15. scispace.com [scispace.com]

- To cite this document: BenchChem. [Technical Support Center: Gallium Arsenide (GaAs)

Transistor Performance Enhancement]. BenchChem, [2025]. [Online PDF]. Available at:

[https://www.benchchem.com/product/b074776#improving-the-performance-of-gallium-arsenide-based-transistors]

#### **Disclaimer & Data Validity:**

The information provided in this document is for Research Use Only (RUO) and is strictly not intended for diagnostic or therapeutic procedures. While BenchChem strives to provide accurate protocols, we make no warranties, express or implied, regarding the fitness of this product for every specific experimental setup.

**Technical Support:** The protocols provided are for reference purposes. Unsure if this reagent suits your experiment? [Contact our Ph.D. Support Team for a compatibility check]

Need Industrial/Bulk Grade? Request Custom Synthesis Quote

## BenchChem

Our mission is to be the trusted global source of essential and advanced chemicals, empowering scientists and researchers to drive progress in science and industry.

#### Contact

Address: 3281 E Guasti Rd

Ontario, CA 91761, United States

Phone: (601) 213-4426

Email: info@benchchem.com