# Technical Support Center: Erbium Silicide Contacts on Silicon

Author: BenchChem Technical Support Team. Date: December 2025

| Compound of Interest |                 |           |

|----------------------|-----------------|-----------|

| Compound Name:       | Erbium silicide |           |

| Cat. No.:            | B1143583        | Get Quote |

This technical support center provides troubleshooting guidance and frequently asked questions (FAQs) for researchers, scientists, and drug development professionals working on reducing the contact resistance of **erbium silicide** (ErSi<sub>x</sub>) on silicon (Si) substrates.

# Frequently Asked Questions (FAQs) & Troubleshooting

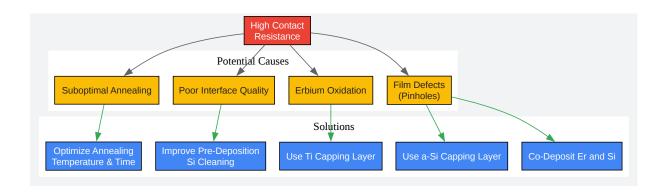

Issue 1: High Contact Resistance after Annealing

- Question: We observe high contact resistance from our erbium silicide contacts on n-type silicon after the annealing step. What are the potential causes and solutions?

- Answer: High contact resistance in ErSi<sub>x</sub>/n-Si contacts can stem from several factors. A primary cause can be an suboptimal annealing temperature. The formation of the desired low-resistance ErSi<sub>2-x</sub> phase is temperature-dependent. Annealing at temperatures below 500°C may result in incomplete silicide formation, while excessively high temperatures can lead to film agglomeration or defect formation.[1][2] Another significant factor is the interface quality between the **erbium silicide** and the silicon. Interfacial oxides or contaminants can impede current flow. Additionally, dopant segregation at the interface, while potentially beneficial, can also be influenced by annealing conditions, affecting the Schottky barrier height (SBH).[3][4]

Troubleshooting Steps:

## Troubleshooting & Optimization

- Optimize Annealing Temperature: Experiment with a range of annealing temperatures, typically between 450°C and 600°C, to form the desired ErSi<sub>2-x</sub> phase without causing film degradation.[2]

- Improve Interface Cleanliness: Ensure a pristine silicon surface before erbium deposition by employing a thorough cleaning procedure, such as an RCA clean followed by a dilute HF dip to remove the native oxide.

- Utilize a Capping Layer: The deposition of a thin capping layer, such as titanium (Ti), on top of the erbium film before annealing can prevent oxidation of the erbium and the underlying silicon during the thermal processing.[2]

- Consider Dopant Segregation Engineering: For advanced applications, techniques like Silicidation-Induced Dopant Segregation (SIDS) or Silicide As Diffusion Source (SADS) can be employed to intentionally modulate the dopant concentration at the silicide-silicon interface to lower the Schottky barrier height.[3]

### Issue 2: Poor Film Morphology and Pinhole Formation

- Question: Our erbium silicide films exhibit poor surface morphology, including the presence of pinholes after annealing. How can we mitigate this?

- Answer: Pinhole and pyramidal defect formation in erbium silicide films is a known issue that can significantly increase contact resistance and degrade device performance.[1][2][5]

These defects often arise from the diffusion of silicon atoms during the silicidation process.

The initial thickness of the deposited erbium layer plays a crucial role; thicker films are more prone to defect formation.[1][2]

### Troubleshooting Steps:

- Optimize Erbium Thickness: Carefully control the thickness of the initial deposited erbium film. Thinner layers generally lead to better film morphology.

- Amorphous Silicon Capping: A proven technique to suppress pinhole formation is to deposit a thin layer of amorphous silicon (a-Si) on top of the erbium film before annealing. This a-Si layer acts as a silicon source, minimizing the consumption of silicon atoms from the substrate and thus reducing the likelihood of void and pinhole formation.[2]

Co-deposition of Erbium and Silicon: Instead of sequential deposition, co-sputtering or coevaporation of erbium and silicon to form the silicide layer can result in a more uniform film with a smoother interface.

## Issue 3: Inconsistent Schottky Barrier Height (SBH)

- Question: We are measuring inconsistent Schottky barrier heights across our samples. What factors contribute to this variability?

- Answer: Inconsistent Schottky barrier heights can be attributed to variations in the interfacial properties of the ErSi<sub>x</sub>/Si contact. The SBH is highly sensitive to the phase of the erbium silicide formed, the presence of an interfacial layer (like a thin oxide), and the dopant concentration at the interface.[1][2] Inhomogeneities in the SBH across the contact area can also arise from material defects.[2]

#### Troubleshooting Steps:

- Ensure Consistent Silicide Phase Formation: Use characterization techniques like X-ray Diffraction (XRD) to verify the formation of the desired ErSi<sub>2-x</sub> phase and ensure your annealing process is reproducible.

- Rigorous Surface Preparation: Implement a stringent and consistent pre-deposition

cleaning process for the silicon wafers to minimize variations in the native oxide thickness.

- Control Annealing Ambient: Perform annealing in a controlled environment, such as a high-vacuum chamber or in a forming gas (N<sub>2</sub>/H<sub>2</sub>) ambient, to prevent unintended oxidation during the thermal step.[2]

- Characterize Dopant Profiles: Use techniques like Secondary Ion Mass Spectrometry (SIMS) to analyze the dopant profile near the interface, as dopant segregation can significantly impact the effective SBH.[6][7]

## **Quantitative Data Summary**

Table 1: Annealing Temperature vs. Schottky Barrier Height (SBH) for ErSi<sub>2-x</sub> on Silicon

| Silicon Type   | Annealing<br>Temperature (°C) | Mean SBH (eV) | Ideality Factor (n)        |

|----------------|-------------------------------|---------------|----------------------------|

| p-type Si(100) | As-deposited                  | 0.694         | -                          |

| p-type Si(100) | 500 - 900                     | 0.783 - 0.805 | Increases with temperature |

| n-type Si(100) | 500                           | ~0.343        | -                          |

| n-type Si(100) | 600                           | ~0.350        | -                          |

| n-type Si(100) | 700                           | ~0.427        | -                          |

| n-type Si(100) | 800                           | ~0.410        | -                          |

| n-type Si(100) | 900                           | ~0.390        | -                          |

Data synthesized from multiple sources.[1][2]

Table 2: Contact Resistivity of **Erbium Silicide** on n-type Silicon

| Doping Density (cm <sup>-3</sup> ) | Contact Resistivity (Ω·cm²)    |

|------------------------------------|--------------------------------|

| 1018 - 1020                        | As low as $1.7 \times 10^{-8}$ |

This extremely low resistivity is achievable with optimized structures and annealing.[8]

## **Experimental Protocols**

Protocol 1: Formation of Erbium Silicide Contacts with a Ti Capping Layer

- Substrate Cleaning:

- Perform a standard RCA clean on the Si(100) substrate.

- Immediately prior to loading into the deposition chamber, dip the substrate in a dilute hydrofluoric acid (HF) solution (e.g., 2% HF) for 60 seconds to remove the native oxide.

- Rinse with deionized (DI) water and dry with nitrogen gas.

### • Thin Film Deposition:

- Load the cleaned substrate into a high-vacuum sputtering or electron-beam evaporation system.

- Deposit a 30 nm layer of Erbium (Er).

- Without breaking vacuum, deposit a 10 nm Titanium (Ti) capping layer.

- Rapid Thermal Annealing (RTA):

- Transfer the sample to an RTA chamber.

- Anneal at a temperature between 450°C and 600°C for 30 to 60 seconds in a forming gas (e.g., 95% N<sub>2</sub>, 5% H<sub>2</sub>) or nitrogen ambient.[2]

- Capping Layer Removal (if necessary):

- The Ti capping layer may be selectively etched away using a suitable wet etchant that does not attack the erbium silicide.

- Characterization:

- Electrical: Use a four-point probe to measure sheet resistance and the transmission line method (TLM) to determine contact resistance.

- Physical: Employ X-ray Diffraction (XRD) to confirm the ErSi<sub>2-x</sub> phase, Scanning Electron Microscopy (SEM) to inspect surface morphology, and Atomic Force Microscopy (AFM) to quantify surface roughness.[1]

## **Visualizations**

Click to download full resolution via product page

### **Need Custom Synthesis?**

BenchChem offers custom synthesis for rare earth carbides and specific isotopiclabeling.

Email: info@benchchem.com or Request Quote Online.

## References

- 1. pubs.aip.org [pubs.aip.org]

- 2. researchgate.net [researchgate.net]

- 3. researchgate.net [researchgate.net]

- 4. Metal Silicidation in Conjunction with Dopant Segregation: A Promising Strategy for Fabricating High-Performance Silicon-Based Photoanodes - PubMed [pubmed.ncbi.nlm.nih.gov]

- 5. Making sure you're not a bot! [tib.eu]

- 6. d-nb.info [d-nb.info]

- 7. Dopant Segregation at Silicon-oxide Interfaces [repository.lib.ncsu.edu]

- 8. pubs.aip.org [pubs.aip.org]

- To cite this document: BenchChem. [Technical Support Center: Erbium Silicide Contacts on Silicon]. BenchChem, [2025]. [Online PDF]. Available at: [https://www.benchchem.com/product/b1143583#reducing-contact-resistance-of-erbium-silicide-on-silicon]

#### **Disclaimer & Data Validity:**

The information provided in this document is for Research Use Only (RUO) and is strictly not intended for diagnostic or therapeutic procedures. While BenchChem strives to provide accurate protocols, we make no warranties, express or implied, regarding the fitness of this product for every specific experimental setup.

**Technical Support:** The protocols provided are for reference purposes. Unsure if this reagent suits your experiment? [Contact our Ph.D. Support Team for a compatibility check]

Need Industrial/Bulk Grade? Request Custom Synthesis Quote

## BenchChem

Our mission is to be the trusted global source of essential and advanced chemicals, empowering scientists and researchers to drive progress in science and industry. Contact

Address: 3281 E Guasti Rd

Ontario, CA 91761, United States

Phone: (601) 213-4426

Email: info@benchchem.com