## Technical Support Center: Enhancing the Long-Term Stability of Decamethylruthenocene-Based Devices

Author: BenchChem Technical Support Team. Date: December 2025

| Compound of Interest |                       |           |

|----------------------|-----------------------|-----------|

| Compound Name:       | Decamethylruthenocene |           |

| Cat. No.:            | B15500432             | Get Quote |

This technical support center provides researchers, scientists, and drug development professionals with troubleshooting guides and frequently asked questions (FAQs) to address common challenges encountered during the fabrication and characterization of **decamethylruthenocene**-based electronic devices. The information is presented in a question-and-answer format to directly address specific issues.

### **Frequently Asked Questions (FAQs)**

Q1: What are the primary environmental factors that affect the stability of **decamethylruthenocene**-based devices?

A1: **Decamethylruthenocene**-based devices are primarily susceptible to degradation from atmospheric exposure, particularly to oxygen and moisture.[1][2] These environmental factors can lead to changes in the material's electronic properties and device performance over time. High humidity can be particularly detrimental to the performance of sensors based on organometallic compounds.[3]

Q2: How does atmospheric exposure manifest in device performance degradation?

A2: Exposure to ambient air can lead to several detrimental effects on device performance. For graphene transistors, which share some environmental sensitivities with organometallic devices, aging in ambient air has been shown to decrease carrier mobility and increase contact

resistance.[4] In many organic thin-film transistors (TFTs), this degradation can be observed as a rapid decrease in charge-carrier mobility.[5]

Q3: What are common failure modes observed in organometallic-based thin-film transistors?

A3: Common failure modes in organic and organometallic TFTs include:

- Increased Leakage Current: This can be due to various factors, including reverse-bias pn

junction leakage and subthreshold leakage.[6]

- Threshold Voltage Shift: The threshold voltage can shift over time, especially under bias stress, affecting the switching characteristics of the transistor.

- Decreased Mobility: The charge carrier mobility can decrease due to structural reorganization of the thin film or trapping of charges at the semiconductor-dielectric interface.

[5]

- Contact Resistance Degradation: The resistance at the metal-organometallic interface can increase, leading to poor device performance. This can be exacerbated by fretting and corrosion at the contact interface.[4][7][8]

# Troubleshooting Guides Issue 1: Inconsistent or non-functional transistor

- Question: I have fabricated a decamethylruthenocene-based thin-film transistor, but I am

not observing the expected output and transfer characteristics. The gate and drain currents

are very low. What could be the issue?

- Possible Causes & Solutions:

characteristics.

- Poor Film Quality: The decamethylruthenocene film may have unconnected grains or poor morphology.

- Solution: Optimize the deposition parameters. Consider thermal annealing to increase grain size and improve film connectivity.[9] The substrate temperature during deposition can significantly impact film structure and charge carrier mobility.[10]

- High Contact Resistance: There may be a poor interface between the decamethylruthenocene layer and the source/drain electrodes.

- Solution: Ensure proper cleaning of the substrate and electrodes before depositing the organometallic layer. The choice of contact metal is also crucial.

- Traps at the Dielectric Interface: Charge traps at the semiconductor-dielectric interface can hinder channel formation.

- Solution: Utilize a high-quality gate dielectric. Surface treatment of the dielectric before

decamethylruthenocene deposition can help in reducing trap states.

- Incorrect Gate Voltage Range: The applied gate voltage may not be sufficient to turn the transistor on, especially with thicker gate dielectrics.

- Solution: Try applying higher gate voltages. For a 200nm SiO2 dielectric, voltages as high as 40V may be necessary.[9]

## Issue 2: Device performance degrades rapidly after fabrication.

- Question: My decamethylruthenocene device shows good initial performance, but the mobility and on/off ratio decrease significantly after a short period in ambient conditions. How can I improve its stability?

- Possible Causes & Solutions:

- Atmospheric Degradation: Exposure to oxygen and moisture is a primary cause of degradation in many organic and organometallic electronic devices.[1][2]

- Solution: Passivation/Encapsulation. Encapsulating the device with a barrier layer can protect it from the environment. Common passivation materials include polymethyl methacrylate (PMMA) and silicon dioxide (SiO2).[11][12][13] PMMA offers the advantage of being solution-processable.[11]

- Structural Reorganization of the Thin Film: Ultrathin films of organic semiconductors can undergo spontaneous morphological changes that lead to performance degradation.[5]

Solution: In-situ encapsulation immediately after deposition of the

decamethylruthenocene film can help decelerate this structural reorganization.[5]

## Data Presentation: Passivation Effects on Device Stability

While specific quantitative data for **decamethylruthenocene** is limited in the available literature, the following table summarizes the general effects of common passivation layers on the stability of organic and metal-oxide thin-film transistors, which can serve as a guideline for experiments with **decamethylruthenocene**-based devices.

| Passivation<br>Material         | Deposition Method                                 | Key Advantages                                                                             | Reported Stability<br>Improvements                                                                                             |

|---------------------------------|---------------------------------------------------|--------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------|

| РММА                            | Spin-coating                                      | Solution-processable, good barrier against moisture and oxygen. [11]                       | Prevents threshold<br>voltage shifts, reduces<br>hump, and maintains<br>mobility and on/off<br>ratio under bias<br>stress.[11] |

| Silicon Dioxide (SiO2)          | Chemical Vapor<br>Deposition (CVD),<br>Sputtering | Excellent barrier properties, well-established deposition techniques.                      | Can effectively passivate silicon surfaces, though high- temperature annealing may be required for optimal performance. [13]   |

| Triple Layer<br>(PMMA/SiO2/ZnO) | Spin-coating & Sputtering                         | High dielectric constant, excellent performance and stability, minimal hysteresis.[12][14] | Achieved high mobility<br>and stability on both<br>rigid and flexible<br>substrates.[14]                                       |

## **Experimental Protocols**

### **Protocol 1: PMMA Passivation by Spin-Coating**

This protocol provides a general procedure for encapsulating a **decamethylruthenocene**-based device with a PMMA passivation layer.

#### Materials:

- PMMA powder

- Anisole or other suitable solvent

- Substrate with fabricated decamethylruthenocene device

- Spin-coater

- Hotplate

#### Procedure:

- Prepare PMMA Solution: Dissolve PMMA powder in anisole to the desired concentration (e.g., 4% by weight). Stir the solution overnight to ensure complete dissolution.

- Substrate Preparation: Ensure the device substrate is clean and dry.

- Spin-Coating:

- Place the substrate on the spin-coater chuck.

- Dispense the PMMA solution onto the center of the substrate.

- Spin the substrate at a desired speed (e.g., 2000-4000 rpm) for a set time (e.g., 30-60 seconds) to achieve the desired film thickness.

- Baking:

- Carefully transfer the substrate to a hotplate.

- Bake at a temperature below the glass transition temperature of PMMA (e.g., 80-100 °C)

for a specified time (e.g., 10-30 minutes) to remove the solvent.

## Protocol 2: Thermal Annealing of Decamethylruthenocene Thin Films

Thermal annealing can be used to improve the crystallinity and morphology of the active layer, potentially enhancing device performance and stability.

#### Materials:

- Substrate with deposited decamethylruthenocene film

- Tube furnace or rapid thermal annealing (RTA) system

- Inert gas supply (e.g., Nitrogen or Argon)

#### Procedure:

- Setup: Place the substrate in the center of the furnace or RTA chamber.

- Inert Atmosphere: Purge the chamber with an inert gas for a sufficient time to remove oxygen.

- Heating:

- Ramp up the temperature to the desired annealing temperature at a controlled rate (e.g., 5-10 °C/min). The optimal annealing temperature needs to be determined experimentally for decamethylruthenocene.

- Hold the substrate at the annealing temperature for a specific duration (e.g., 30-60 minutes).

- Cooling:

- Allow the substrate to cool down slowly to room temperature under the inert atmosphere.

## **Mandatory Visualizations**

Click to download full resolution via product page

Caption: Experimental workflow for fabricating and testing passivated **decamethylruthenocene** devices.

Click to download full resolution via product page

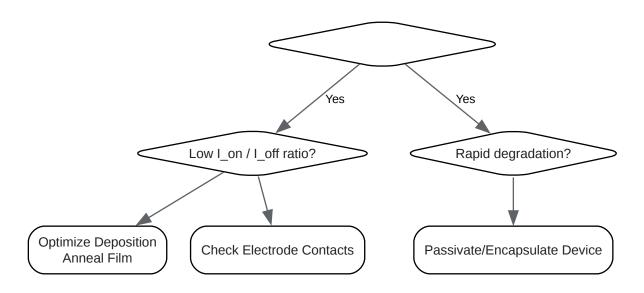

Caption: A simplified troubleshooting flowchart for common issues in **decamethylruthenocene** devices.

#### **Need Custom Synthesis?**

BenchChem offers custom synthesis for rare earth carbides and specific isotopiclabeling.

Email: info@benchchem.com or Request Quote Online.

#### References

1. researchgate.net [researchgate.net]

- 2. researchgate.net [researchgate.net]

- 3. Degradation of high-molar-mass hyaluronan and characterization of fragments PubMed [pubmed.ncbi.nlm.nih.gov]

- 4. arxiv.org [arxiv.org]

- 5. Stability of organic thin-film transistors based on ultrathin films of dinaphtho[2,3-b:2',3'-f]thieno[3,2-b]thiophene (DNTT) Journal of Materials Chemistry C (RSC Publishing) [pubs.rsc.org]

- 6. web.mit.edu [web.mit.edu]

- 7. Item Degradation of electrical contacts under low frequency fretting conditions Loughborough University Figshare [repository.lboro.ac.uk]

- 8. mdpi.com [mdpi.com]

- 9. researchgate.net [researchgate.net]

- 10. new-air-stable-n-channel-organic-thin-film-transistors Ask this paper | Bohrium [bohrium.com]

- 11. researchgate.net [researchgate.net]

- 12. researchgate.net [researchgate.net]

- 13. researchportalplus.anu.edu.au [researchportalplus.anu.edu.au]

- 14. preprints.org [preprints.org]

- To cite this document: BenchChem. [Technical Support Center: Enhancing the Long-Term Stability of Decamethylruthenocene-Based Devices]. BenchChem, [2025]. [Online PDF]. Available at: [https://www.benchchem.com/product/b15500432#enhancing-the-long-term-stability-of-decamethylruthenocene-based-devices]

#### **Disclaimer & Data Validity:**

The information provided in this document is for Research Use Only (RUO) and is strictly not intended for diagnostic or therapeutic procedures. While BenchChem strives to provide accurate protocols, we make no warranties, express or implied, regarding the fitness of this product for every specific experimental setup.

**Technical Support:** The protocols provided are for reference purposes. Unsure if this reagent suits your experiment? [Contact our Ph.D. Support Team for a compatibility check]

#### Need Industrial/Bulk Grade? Request Custom Synthesis Quote

## BenchChem

Our mission is to be the trusted global source of essential and advanced chemicals, empowering scientists and researchers to drive progress in science and industry. Contact

Address: 3281 E Guasti Rd

Ontario, CA 91761, United States

Phone: (601) 213-4426

Email: info@benchchem.com