# Technical Support Center: Enhancing Power Conversion Efficiency of SubPc-Based Solar Cells

Author: BenchChem Technical Support Team. Date: December 2025

| Compound of Interest |                                  |           |

|----------------------|----------------------------------|-----------|

| Compound Name:       | Boron subphthalocyanine chloride |           |

| Cat. No.:            | B3068306                         | Get Quote |

This technical support center provides researchers, scientists, and drug development professionals with comprehensive troubleshooting guides and frequently asked questions (FAQs) to address common issues encountered during the fabrication and characterization of SubPc-based solar cells.

## **Frequently Asked Questions (FAQs)**

Q1: What is a typical device architecture for a SubPc-based solar cell?

A1: A common device architecture is a planar bilayer heterojunction structure. This typically consists of the following layers stacked on a substrate like Indium Tin Oxide (ITO) coated glass:

- Anode: Indium Tin Oxide (ITO) serves as the transparent conductor for light to enter and for hole collection.

- Hole Transport Layer (HTL): A material like PEDOT:PSS or Molybdenum Trioxide (MoO₃) is used to facilitate the efficient movement of holes from the active layer to the anode.

- Active Layer (Donor): The Chloroboron(III) subphthalocyanine (SubPc) layer absorbs photons to generate excitons.

- Active Layer (Acceptor): A fullerene derivative, such as C60 or C70, is used to accept electrons.

#### Troubleshooting & Optimization

- Electron Transport Layer (ETL): A material like Bathophenanthroline (BPhen) helps in transporting electrons from the active layer to the cathode.

- Cathode: A metal with a low work function, such as Aluminum (Al) or Silver (Ag), is used as the top electrode for electron collection.

Q2: What are the key performance parameters I should be measuring for my SubPc solar cell?

A2: The performance of your solar cell is evaluated using several key parameters derived from the current density-voltage (J-V) curve measured under simulated sunlight (AM 1.5G, 100 mW/cm<sup>2</sup>):

- Open-Circuit Voltage (Voc): The maximum voltage the solar cell can produce when there is no current flowing.

- Short-Circuit Current Density (Jsc): The maximum current density the solar cell can produce when the voltage across it is zero.

- Fill Factor (FF): A measure of the "squareness" of the J-V curve, representing the ratio of the maximum power from the solar cell to the product of Voc and Jsc.

- Power Conversion Efficiency (PCE): The overall efficiency of the solar cell in converting light energy into electrical energy. It is calculated as: PCE (%) = (Voc × Jsc × FF) / Pin, where Pin is the power of the incident light.

Q3: How does the thickness of the SubPc layer affect device performance?

A3: The thickness of the SubPc donor layer is a critical parameter that significantly impacts the Power Conversion Efficiency (PCE). An optimal thickness is required to balance light absorption and charge carrier collection. If the layer is too thin, it won't absorb enough light, leading to a low short-circuit current density (Jsc). Conversely, if the layer is too thick, the charge carriers (holes) may not be able to travel to the electrode before recombining, which also reduces Jsc and the fill factor (FF). Studies have shown that for SubPc/C60 based solar cells, the PCE is maximized at a SubPc layer thickness of approximately 130 Å (13 nm)[1].

Q4: What is the purpose of thermal annealing in the fabrication process?

A4: Thermal annealing after the deposition of the active layers can significantly improve the performance of SubPc-based solar cells. The heat treatment can lead to a more ordered molecular morphology in the SubPc film. This improved crystallinity can enhance the optical absorption in the 550-630 nm spectral range. Consequently, a thermally treated solar cell can exhibit a higher power conversion efficiency (PCE) compared to a non-annealed device, with improvements of almost 10% being reported[2][3].

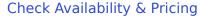

# **Troubleshooting Guide**

This guide addresses common problems that can lead to suboptimal performance in your SubPc-based solar cells.

Problem 1: Low Short-Circuit Current Density (Jsc)

| Potential Cause               | Recommended Solution                                                                                                                                                                                                              |

|-------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Inadequate Light Absorption   | Optimize the thickness of the SubPc active layer. A thickness of around 13 nm has been found to be optimal for SubPc/C60 devices[1].                                                                                              |

| Poor Film Morphology          | Increase the deposition rate of the SubPc layer.  A higher deposition rate (up to 5 Å/s) can lead to a rougher surface, which increases the interfacial area between the SubPc and C60 layers, improving charge separation[2][3]. |

| High Series Resistance        | Ensure good contact between the active layer and the electrodes. Consider annealing the device to improve charge carrier mobility.                                                                                                |

| Inefficient Charge Collection | A SubPc layer that is too thick can hinder hole collection. Ensure the thickness is not significantly greater than the exciton diffusion length of the material.                                                                  |

| Contamination                 | Thoroughly clean the ITO substrate before depositing the layers. Contaminants can act as recombination centers.                                                                                                                   |

#### Problem 2: Low Open-Circuit Voltage (Voc)

| Potential Cause             | Recommended Solution                                                                                                                                                                                               |

|-----------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| High Recombination Rate     | High rates of charge recombination at the donor-acceptor interface or within the bulk material can lower Voc. Improve the quality of the active layer films through optimized deposition and annealing conditions. |

| Poor Energy Level Alignment | The Voc is related to the energy difference between the HOMO of the donor (SubPc) and the LUMO of the acceptor (e.g., C60). Ensure the chosen acceptor material provides a suitable energy level offset.           |

| Shunt Resistance            | Pinholes or defects in the active layer can create alternative current paths (shunts), which lower the Voc. Ensure uniform and pinhole-free film deposition.                                                       |

Problem 3: Low Fill Factor (FF)

| Potential Cause                                    | Recommended Solution                                                                                                                                                                               |

|----------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| High Series Resistance                             | High resistance in the bulk layers or at the contacts impedes current flow and reduces the FF. Optimize the thickness of all layers and ensure high-quality electrode deposition.                  |

| Low Shunt Resistance                               | As with low Voc, shunt pathways due to defects will significantly decrease the FF. Improve film quality and uniformity.                                                                            |

| Charge Carrier Recombination                       | High recombination rates mean that fewer charge carriers are collected, leading to a less "square" J-V curve and a lower FF. Annealing the device can improve morphology and reduce recombination. |

| Poor Morphology at the Donor-Acceptor<br>Interface | A non-optimal interface can hinder efficient charge separation and extraction. Increasing the SubPc deposition rate can create a more corrugated interface, which is beneficial[2][3].             |

# **Data Presentation**

Table 1: Effect of SubPc Layer Thickness on Photovoltaic Performance

| SubPc Layer<br>Thickness (Å) | Jsc (mA/cm²) | Voc (V) | FF (%) | PCE (%) |

|------------------------------|--------------|---------|--------|---------|

| 70                           | 3.8          | 0.85    | 0.55   | 1.78    |

| 110                          | 4.2          | 0.85    | 0.60   | 2.14    |

| 130                          | 4.5          | 0.85    | 0.57   | 2.18    |

| 160                          | 3.5          | 0.85    | 0.39   | 1.16    |

| 250                          | 2.5          | 0.85    | 0.28   | 0.60    |

Data adapted

from a study on

SubPc/C60

based OPV cells.

Table 2: Impact of Thermal Annealing on SubPc/C60 Solar Cell Performance

| Annealing<br>Condition                                                            | Jsc (mA/cm²) | Voc (V) | FF (%) | PCE (%) |

|-----------------------------------------------------------------------------------|--------------|---------|--------|---------|

| Non-annealed                                                                      | 4.1          | 0.85    | 0.55   | 1.92    |

| Annealed at 100°C                                                                 | 4.3          | 0.85    | 0.58   | 2.12    |

| Data suggests that thermal annealing can lead to a ~10% improvement in PCE.[2][3] |              |         |        |         |

# **Experimental Protocols**

Protocol 1: Fabrication of a Planar Bilayer SubPc/C60 Solar Cell

• Substrate Cleaning:

- Sequentially sonicate ITO-coated glass substrates in deionized water, acetone, and isopropyl alcohol for 15 minutes each.

- Dry the substrates with a stream of dry nitrogen.

- Treat the substrates with UV-Ozone for 15-20 minutes to remove organic residues and improve the ITO work function.

- Hole Transport Layer (HTL) Deposition:

- Deposit a thin layer of MoO₃ (typically 5-10 nm) onto the cleaned ITO substrate via thermal evaporation in a high-vacuum chamber (pressure < 1x10-6 mbar).</li>

- Active Layer Deposition (Thermal Evaporation):

- SubPc Deposition: Evaporate SubPc onto the MoO₃ layer at a deposition rate of 0.1-0.2 nm/s to achieve the desired thickness (e.g., 13 nm).

- C60 Deposition: Without breaking the vacuum, evaporate C60 onto the SubPc layer to the desired thickness (e.g., 40 nm).

- Electron Transport Layer (ETL) Deposition:

- Deposit a thin layer of BCP (typically 5-10 nm) onto the C60 layer via thermal evaporation.

- Cathode Deposition:

- Deposit a layer of Aluminum (Al) or Silver (Ag) (typically 80-100 nm) through a shadow mask to define the active area of the device.

- Annealing (Optional):

- Post-fabrication, anneal the device on a hotplate in a nitrogen-filled glovebox at a specified temperature (e.g., 100°C) for a set duration (e.g., 10 minutes).

- Encapsulation:

- For improved stability, encapsulate the device in an inert atmosphere using a UV-curable epoxy and a glass coverslip.

- Characterization:

- Measure the current density-voltage (J-V) characteristics of the device using a solar simulator under AM 1.5G illumination (100 mW/cm²).

## **Visualizations**

Click to download full resolution via product page

Caption: Experimental workflow for the fabrication of a SubPc-based solar cell.

Click to download full resolution via product page

#### **Need Custom Synthesis?**

BenchChem offers custom synthesis for rare earth carbides and specific isotopiclabeling.

Email: info@benchchem.com or Request Quote Online.

## References

- 1. researchgate.net [researchgate.net]

- 2. researchgate.net [researchgate.net]

- 3. researchgate.net [researchgate.net]

- To cite this document: BenchChem. [Technical Support Center: Enhancing Power Conversion Efficiency of SubPc-Based Solar Cells]. BenchChem, [2025]. [Online PDF]. Available at: [https://www.benchchem.com/product/b3068306#enhancing-the-power-conversion-efficiency-of-subpc-based-solar-cells]

#### **Disclaimer & Data Validity:**

The information provided in this document is for Research Use Only (RUO) and is strictly not intended for diagnostic or therapeutic procedures. While BenchChem strives to provide accurate protocols, we make no warranties, express or implied, regarding the fitness of this product for every specific experimental setup.

**Technical Support:**The protocols provided are for reference purposes. Unsure if this reagent suits your experiment? [Contact our Ph.D. Support Team for a compatibility check]

Need Industrial/Bulk Grade? Request Custom Synthesis Quote

# BenchChem

Our mission is to be the trusted global source of essential and advanced chemicals, empowering scientists and researchers to drive progress in science and industry. Contact

Address: 3281 E Guasti Rd

Ontario, CA 91761, United States

Phone: (601) 213-4426

Email: info@benchchem.com