# Technical Support Center: Enhancing InAs-Based Transistor Performance

Author: BenchChem Technical Support Team. Date: December 2025

| Compound of Interest |                 |           |

|----------------------|-----------------|-----------|

| Compound Name:       | Indium arsenide |           |

| Cat. No.:            | B073376         | Get Quote |

This technical support center provides troubleshooting guides and frequently asked questions (FAQs) to assist researchers, scientists, and drug development professionals in optimizing the performance of **Indium Arsenide** (InAs)-based transistors. The information is presented in a user-friendly question-and-answer format, addressing specific experimental challenges.

## **Troubleshooting Guides**

This section offers step-by-step guidance to diagnose and resolve common issues encountered during the fabrication and characterization of InAs-based transistors.

### **Issue 1: High Leakage Current**

Q: My InAs transistor exhibits high off-state leakage current. What are the potential causes and how can I troubleshoot this?

A: High leakage current in InAs transistors is frequently attributed to poor surface passivation, leading to surface states and parasitic conduction pathways.

#### **Troubleshooting Steps:**

Verify Surface Cleaning: Ensure that the InAs surface was adequately cleaned to remove native oxides before subsequent processing steps. Residual oxides can create trap states and leakage paths.

## Troubleshooting & Optimization

- Evaluate Passivation Layer: The choice and quality of the surface passivation layer are critical. Different passivation materials have varying effectiveness in reducing surface leakage. Consider the following:

- Material Selection: Materials like Aluminum Nitride (AlN), Aluminum Oxide (Al2O3), and certain polymers have shown success in passivating InAs surfaces.

- Deposition Quality: The deposition method and parameters significantly impact the quality of the passivation layer. Techniques like Atomic Layer Deposition (ALD) offer excellent conformality and thickness control.

- Mesa Sidewall Passivation: For mesa-isolated devices, ensure that the sidewalls are properly passivated, as this is a common source of leakage current.

- Gate Dielectric Integrity: In MOSFETs, a leaky gate dielectric can contribute to the off-state current. Characterize the dielectric to check for high defect density or pinholes.

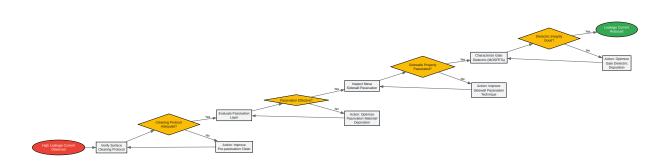

Troubleshooting Workflow for High Leakage Current

Click to download full resolution via product page

Caption: Troubleshooting workflow for high leakage current in InAs transistors.

## **Issue 2: Low Electron Mobility**

Q: The measured electron mobility in my InAs quantum well (QW) transistor is lower than expected. How can I identify the cause and improve it?

A: Low electron mobility in InAs QWs is often a result of scattering from various sources, including interface roughness, impurities, and crystalline defects.

#### **Troubleshooting Steps:**

- Assess Interface Roughness: The interfaces of the InAs QW are critical. Rough interfaces can lead to significant scattering.

- Growth Conditions: Optimize the molecular beam epitaxy (MBE) or metal-organic chemical vapor deposition (MOCVD) growth parameters, such as temperature and growth rate.

- Surface Smoothing: Employing surface smoothing techniques during growth, such as growth interruptions, can lead to flatter interfaces and improved mobility.

- Examine Impurity Scattering: Both intentional dopants and unintentional impurities can act as scattering centers.

- Remote Doping: If using modulation doping, optimize the spacer layer thickness to balance carrier density and scattering from remote ionized donors.

- Background Impurities: Ensure high-purity source materials and a clean growth environment to minimize background impurity incorporation.

- Investigate Crystalline Quality: Dislocations and other crystal defects can degrade mobility.

- Buffer Layer Optimization: The design of the buffer layer is crucial for accommodating lattice mismatch and reducing the density of threading dislocations that can propagate into the active region.

- Structural Characterization: Use techniques like transmission electron microscopy (TEM)

to assess the crystalline quality of the heterostructure.

## **Issue 3: High Contact Resistance**

Q: I am observing high contact resistance in my InAs HEMT, which is limiting its high-frequency performance. What are the common causes and solutions?

A: High contact resistance at the source and drain is a common bottleneck in the performance of InAs transistors. This can be due to an inadequate metal-semiconductor interface or issues with the contact annealing process.

#### **Troubleshooting Steps:**

- Surface Preparation: The InAs surface must be pristine before metal deposition. Any native

oxide will create a barrier and increase resistance. Ensure a thorough surface cleaning and

oxide removal step is performed immediately before loading the sample into the deposition

chamber.

- Metallization Scheme: The choice of metals and their thicknesses is critical for forming a good ohmic contact.

- Common Schemes: Ti/Al/Ni/Au and Ti/Pt/Au are commonly used metallization stacks for InAs.

- Adhesion Layer: A thin layer of Titanium (Ti) is often used to promote adhesion and react with the InAs surface to form a low-resistance contact.

- Annealing Conditions: The post-deposition annealing step is crucial for forming the desired intermetallic compounds and achieving low contact resistance.

- Temperature and Time: The annealing temperature and duration must be carefully optimized. Insufficient annealing may not form the desired alloys, while excessive annealing can lead to metal spiking or degradation of the contact morphology.

- Annealing Ambient: The annealing is typically performed in an inert atmosphere, such as nitrogen (N<sub>2</sub>), to prevent oxidation.

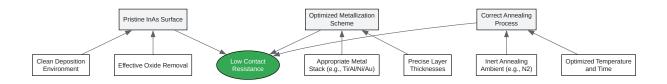

Logical Relationship for Achieving Low Contact Resistance

Click to download full resolution via product page

Caption: Key factors for achieving low contact resistance in InAs transistors.

## Frequently Asked Questions (FAQs)

Q1: What are the most common failure modes for InAs transistors during fabrication?

A1: Common failure modes include:

- Gate-to-Source/Drain Shorts: This can be caused by issues during the gate lithography and etching process, leading to a direct electrical connection between the gate and the source or drain.

- Open Contacts: Incomplete etching of the contact windows or poor metal lift-off can result in an open circuit at the source or drain contacts.

- High Leakage/Low Breakdown Voltage: Often related to inadequate surface passivation or defects in the semiconductor material.

- Cracked Wafers or Layers: Due to the brittle nature of III-V materials, mechanical stress during handling and processing can lead to cracks.

Q2: How does the choice of gate dielectric affect the performance of an InAs MOSFET?

A2: The gate dielectric is crucial for controlling the channel of a MOSFET. For InAs, high-k dielectrics such as Al<sub>2</sub>O<sub>3</sub> and Hafnium Oxide (HfO<sub>2</sub>) are often used to achieve a high gate capacitance without excessively thinning the dielectric, which would lead to high gate leakage current. A high-quality dielectric with a low density of interface traps is essential for achieving a steep subthreshold swing, high on-current, and good threshold voltage stability.

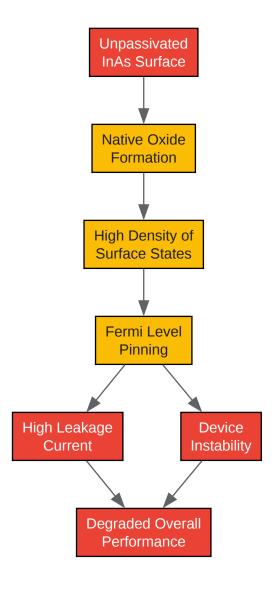

Q3: Why is surface passivation so critical for InAs devices?

A3: The surface of InAs is inherently reactive and prone to the formation of native oxides that are of poor electrical quality. These oxides and the associated surface states can pin the Fermi level, leading to a high surface recombination velocity and creating a conductive surface inversion layer. This results in high leakage currents, device instability, and degraded overall performance. Effective surface passivation neutralizes these surface states and prevents the formation of detrimental native oxides.

Signaling Pathway: Impact of Surface States on Transistor Performance

Click to download full resolution via product page

Caption: Effect of an unpassivated InAs surface on transistor performance.

# **Quantitative Data Summary**

Table 1: Comparison of Surface Passivation Techniques on InAs-based Photodiodes

| Passivation<br>Material        | Deposition Method | R₀A Product<br>(Ω·cm²) at 77 K | Reference |

|--------------------------------|-------------------|--------------------------------|-----------|

| None                           | -                 | 5.7 x 10 <sup>2</sup>          | [1]       |

| Si <sub>3</sub> N <sub>4</sub> | PECVD             | 8.8 x 10 <sup>1</sup>          | [1]       |

| ZnO                            | ALD               | $3.1 \times 10^2$              | [1]       |

| TiO <sub>2</sub>               | ALD               | 1.7 x 10 <sup>3</sup>          | [1]       |

| HfO <sub>2</sub>               | ALD               | 2.8 x 10 <sup>4</sup>          | [1]       |

| SiO <sub>2</sub>               | PECVD             | 3.6 x 10 <sup>5</sup>          | [1]       |

| Al <sub>2</sub> O <sub>3</sub> | ALD               | 2.5 x 10 <sup>6</sup>          | [1]       |

Table 2: Specific Contact Resistance for Different Metallization Schemes on InAs

| Metallization<br>Scheme     | Specific Contact Resistance ( $\Omega$ ·cm <sup>2</sup> ) | Annealing<br>Temperature (°C) | Reference |

|-----------------------------|-----------------------------------------------------------|-------------------------------|-----------|

| Ti/Ni/Au (as-<br>deposited) | 3.0 x 10 <sup>-6</sup>                                    | -                             | [2]       |

| Ti/Pt/Au (as-<br>deposited) | 1.0 x 10 <sup>-6</sup>                                    | -                             | [2]       |

| Ti/Ni/Au (annealed)         | Decreases initially,<br>then degrades above<br>250°C      | 250                           | [2]       |

| Ti/Pt/Au (annealed)         | Stable up to 350°C                                        | 350                           | [2]       |

Table 3: Performance of InAs Nanowire FETs with Different High-k Gate Dielectrics (Simulated)

| Gate Dielectric                | Dielectric<br>Constant (k) | Subthreshold<br>Swing<br>(mV/dec) | On-Current<br>(I_on) (A/μm) | Reference |

|--------------------------------|----------------------------|-----------------------------------|-----------------------------|-----------|

| SiO <sub>2</sub>               | 3.9                        | ~80                               | Lower                       | [3]       |

| Al <sub>2</sub> O <sub>3</sub> | 9                          | ~70                               | Higher                      | [3]       |

| HfO <sub>2</sub>               | 25                         | ~65                               | Higher                      | [3]       |

| La <sub>2</sub> O <sub>3</sub> | 30                         | ~62                               | Higher                      | [3]       |

| TiO <sub>2</sub>               | 80                         | ~60                               | Highest                     | [3]       |

# **Experimental Protocols**

# Protocol 1: Plasma-Enhanced Atomic Layer Deposition (PEALD) of AIN for Surface Passivation

- Substrate Preparation:

- Perform a solvent clean of the InAs substrate using acetone, methanol, and isopropanol.

- Immediately prior to loading into the ALD chamber, perform a native oxide etch using a buffered oxide etch (BOE) or a dilute HCl solution.

- Rinse with deionized water and dry with N<sub>2</sub>.

- ALD Process:

- Transfer the substrate to the PEALD chamber.

- Pre-deposition Plasma Clean: Expose the substrate to a hydrogen (H<sub>2</sub>) or nitrogen (N<sub>2</sub>)

plasma to further clean and prepare the surface.

- Deposition Cycle:

- TMA Pulse: Introduce Trimethylaluminum (TMA) precursor into the chamber.

- Purge: Purge the chamber with an inert gas (e.g., Argon or Nitrogen) to remove unreacted precursor and byproducts.

- Plasma Exposure: Introduce a mixture of N<sub>2</sub> and H<sub>2</sub> gas and ignite the plasma to form the AIN layer.

- Purge: Purge the chamber again with the inert gas.

- Repeat Cycles: Repeat the deposition cycle until the desired AIN thickness is achieved.

- Process Parameters (Example):

- Deposition Temperature: 300-400 °C

- TMA Pulse Time: ~0.06 s

- Plasma Power: ~300 W

- Plasma Duration: ~20 s

- Note: These parameters should be optimized for the specific ALD system being used.

#### Protocol 2: Fabrication of Ti/Al/Ni/Au Ohmic Contacts

- Surface Preparation:

- Perform photolithography to define the source and drain contact areas.

- Immediately before metal deposition, perform an in-situ or ex-situ surface clean to remove the native oxide. An ammonium sulfide ((NH<sub>4</sub>)<sub>2</sub>S) dip is often effective.

- Metal Deposition:

- Load the patterned substrate into an electron-beam or thermal evaporator.

- Ensure a high vacuum (<  $1 \times 10^{-6}$  Torr) to minimize contamination.

- Sequentially deposit the following metal layers:

■ Titanium (Ti): ~20 nm

■ Aluminum (Al): ~100 nm

■ Nickel (Ni): ~40 nm

■ Gold (Au): ~150 nm

#### Lift-off:

- After deposition, perform a lift-off process in a suitable solvent (e.g., acetone) to remove the photoresist and the overlying metal, leaving the desired contact pads.

- Rapid Thermal Annealing (RTA):

- Anneal the sample in an RTA system under a nitrogen (N₂) atmosphere.

- Annealing Parameters (Example):

■ Temperature: 800-950 °C

■ Time: 30-60 seconds

Note: The optimal annealing temperature and time are highly dependent on the specific

AlGaN/GaN heterostructure and should be determined experimentally.[4]

# Protocol 3: High-k Dielectric Deposition using Atomic Layer Deposition (ALD)

- Substrate Preparation:

- Clean the InAs substrate using a standard solvent cleaning procedure.

- Perform a native oxide removal step using a dilute acid (e.g., HCl) or an ammonium-based solution.

- ALD Process:

- Transfer the substrate to the ALD chamber.

- Deposition Cycle (Example for Al<sub>2</sub>O<sub>3</sub>):

- TMA Pulse: Introduce the Trimethylaluminum (TMA) precursor.

- Purge: Purge with an inert gas.

- Oxidant Pulse: Introduce the oxidant precursor (e.g., H<sub>2</sub>O, O<sub>3</sub>).

- Purge: Purge with an inert gas.

- Repeat Cycles: Repeat the cycle to achieve the target dielectric thickness.

- Process Parameters (Example):

- Deposition Temperature: 200-300 °C

- Note: Precursors and deposition temperatures will vary depending on the desired high-k material (e.g., HfO<sub>2</sub>, ZrO<sub>2</sub>).

- Post-Deposition Annealing (PDA):

- A PDA step in a forming gas or nitrogen ambient is often performed to improve the dielectric quality and the interface with the semiconductor. The temperature and duration of the PDA should be optimized.

#### **Need Custom Synthesis?**

BenchChem offers custom synthesis for rare earth carbides and specific isotopiclabeling.

Email: info@benchchem.com or Request Quote Online.

### References

- 1. mdpi.com [mdpi.com]

- 2. researchgate.net [researchgate.net]

- 3. What Causes High Contact Resistance Readings During Testing and How to Resolve Them [kritester.com]

- 4. Mechanism of Ti/Al/Ni/Au ohmic contacts to AlGaN/GaN heterostructures via laser annealing [cpb.iphy.ac.cn]

- To cite this document: BenchChem. [Technical Support Center: Enhancing InAs-Based Transistor Performance]. BenchChem, [2025]. [Online PDF]. Available at: [https://www.benchchem.com/product/b073376#improving-the-performance-of-inas-based-transistors]

#### **Disclaimer & Data Validity:**

The information provided in this document is for Research Use Only (RUO) and is strictly not intended for diagnostic or therapeutic procedures. While BenchChem strives to provide accurate protocols, we make no warranties, express or implied, regarding the fitness of this product for every specific experimental setup.

**Technical Support:** The protocols provided are for reference purposes. Unsure if this reagent suits your experiment? [Contact our Ph.D. Support Team for a compatibility check]

Need Industrial/Bulk Grade? Request Custom Synthesis Quote

# BenchChem

Our mission is to be the trusted global source of essential and advanced chemicals, empowering scientists and researchers to drive progress in science and industry. Contact

Address: 3281 E Guasti Rd

Ontario, CA 91761, United States

Phone: (601) 213-4426

Email: info@benchchem.com