# Technical Support Center: Enhancing Electron Mobility of Perylene Diimides (PDIs) in OFETs

Author: BenchChem Technical Support Team. Date: December 2025

This technical support center provides troubleshooting guidance and answers to frequently asked questions for researchers, scientists, and drug development professionals working with **perylene** diimide (PDI)-based organic field-effect transistors (OFETs). Our goal is to help you overcome common experimental challenges and optimize the electron mobility of your devices.

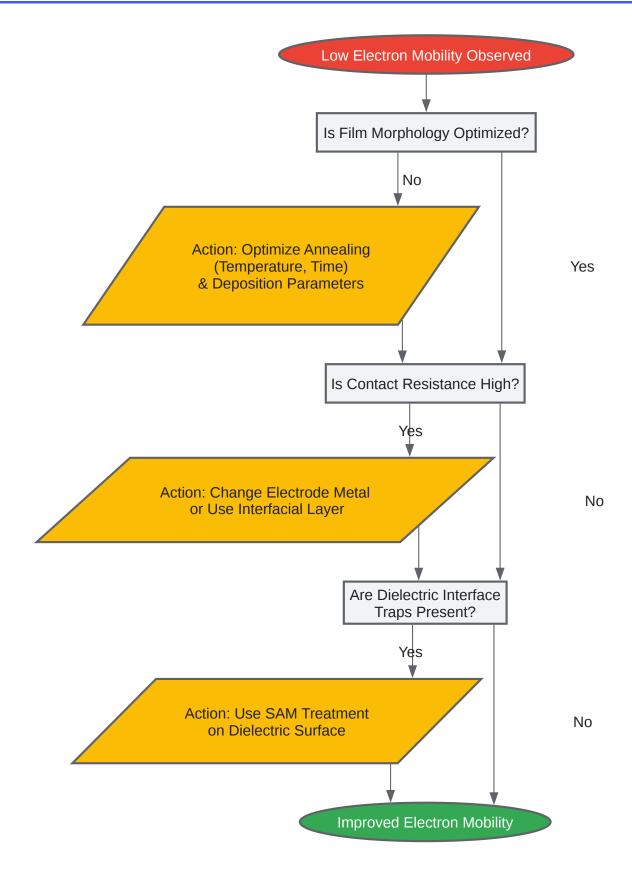

## **Troubleshooting Guide**

This guide addresses specific issues you may encounter during the fabrication and characterization of PDI-based OFETs.

Issue 1: Low Electron Mobility

Question: My OFET device is showing significantly lower electron mobility than expected. What are the potential causes and how can I fix this?

#### Answer:

Low electron mobility in PDI-based OFETs can stem from several factors, ranging from the material's intrinsic properties to the device fabrication process. Here are the most common causes and their solutions:

• Poor Film Morphology: The arrangement of PDI molecules in the thin film is crucial for efficient charge transport. Disordered films with many grain boundaries can trap or scatter electrons, reducing mobility.

### Troubleshooting & Optimization

- Solution: Optimize the deposition conditions. Techniques like thermal annealing or solvent vapor annealing after film deposition can improve crystallinity and molecular packing.[1]

The choice of solvent and substrate temperature during spin-coating also plays a critical role in controlling film morphology.[2]

- High Contact Resistance: A large energy barrier between the source/drain electrodes and the PDI semiconductor layer can impede electron injection, leading to an underestimation of the intrinsic mobility.[3][4] This is especially problematic in short-channel devices.[4]

- Solution: Select appropriate electrode materials with work functions that align with the LUMO level of the PDI derivative to minimize the injection barrier. Surface treatment of the electrodes with self-assembled monolayers (SAMs) can also reduce contact resistance.[5]

The thickness of the organic semiconductor layer can also influence contact properties.[6]

- Dielectric Interface Traps: Traps at the interface between the PDI semiconductor and the gate dielectric can immobilize charge carriers, reducing the measured mobility.[7][8]

- Solution: Engineering the dielectric interface is a key strategy. Using a polymer buffer layer

or treating the dielectric surface with a SAM can passivate traps and improve the

semiconductor film growth, leading to better device performance.[8][9]

- Impurities: Chemical impurities in the PDI material or residual solvent in the thin film can act as charge traps.

- Solution: Ensure the PDI material is of high purity. Use high-purity solvents for solution preparation and ensure the film is thoroughly dried under vacuum to remove any residual solvent.

Issue 2: High "Off" Current and Low On/Off Ratio

Question: My PDI-based OFET has a high off-current, resulting in a poor on/off ratio. What could be the cause?

#### Answer:

A high off-current, which leads to a low on/off ratio, is a common issue that compromises the switching performance of an OFET.[10] Potential causes include:

- Gate Leakage Current: A significant current flowing through the gate dielectric can contribute to a high off-current. This can be due to a very thin or poor-quality dielectric layer.[5]

- Solution: Increase the thickness of the gate dielectric or use a dielectric material with a

higher dielectric constant and better insulating properties.[5][11] Ensure the dielectric layer

is free of pinholes or defects.

- Bulk Conductivity of the Semiconductor: If the PDI film is too thick or has a high bulk conductivity, it can lead to a current that is not effectively modulated by the gate voltage.

- Solution: Optimize the thickness of the semiconductor layer. A thinner film can sometimes lead to better gate modulation and a lower off-current.

- Unintentional Doping: Contaminants from the processing environment, such as oxygen or moisture, can act as dopants and increase the off-current.

- Solution: Process and characterize the devices in an inert atmosphere (e.g., a nitrogenfilled glovebox) to minimize exposure to air and moisture.

## **Frequently Asked Questions (FAQs)**

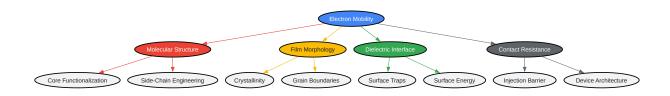

Question 1: What are the most effective strategies to chemically modify PDIs for higher electron mobility?

#### Answer:

Several chemical modification strategies can be employed to enhance the electron mobility of PDI derivatives:

- Core Functionalization: Introducing electron-withdrawing groups, such as halogens or cyano groups, to the **perylene** core can lower the LUMO energy level, which can improve electron injection and air stability.[12]

- Thionation: Replacing the imide oxygen atoms with sulfur (thionation) has been shown to be

a highly effective method for enhancing electron mobility.[13] For instance, a fully thionated

PDI derivative exhibited an average mobility two orders of magnitude larger than its nonthionated counterpart.[13]

- $\pi$ -Conjugation Extension: Expanding the  $\pi$ -conjugated core of the PDI molecule can promote intermolecular  $\pi$ - $\pi$  stacking and improve charge transport pathways.[14]

- Side-Chain Engineering: The choice of N-alkyl or N-aryl substituents on the imide positions significantly influences the molecular packing and film morphology, which in turn affects electron mobility.[15] Bulky or branched side chains can be used to tune the intermolecular distance and packing motif.

Question 2: How does film morphology impact electron mobility, and how can it be controlled?

#### Answer:

The morphology of the PDI thin film, including its crystallinity, grain size, and molecular orientation, is a critical factor determining the OFET's performance.[9][16] Well-ordered, highly crystalline films with large grains and strong  $\pi$ - $\pi$  stacking facilitate efficient charge transport, leading to higher electron mobility.

Strategies for controlling film morphology include:

- Annealing:

- Thermal Annealing: Heating the film after deposition can provide the thermal energy needed for molecules to rearrange into a more ordered, crystalline structure.

- Solvent Vapor Annealing: Exposing the film to a solvent vapor can also induce recrystallization and improve molecular ordering.

- Solution Processing Parameters:

- Solvent Choice: The choice of solvent affects the solubility of the PDI derivative and the drying rate of the film, both of which influence the final morphology.

- Deposition Technique: Different deposition techniques, such as spin-coating, drop-casting, or solution shearing, can result in different film morphologies.[14]

- Substrate Surface Treatment: Modifying the dielectric surface with a self-assembled monolayer (SAM) can alter the surface energy, which influences the growth mode and

morphology of the PDI film.[8][9]

Question 3: Why is the dielectric interface important, and how can it be engineered?

#### Answer:

The interface between the organic semiconductor and the gate dielectric is where the charge transport channel is formed in an OFET.[7] Therefore, the quality of this interface has a profound impact on device performance. A poor interface with a high density of trap states can lead to charge carrier trapping, reduced mobility, and device instability.[7][8]

Dielectric interface engineering techniques include:

- Using Polymer Dielectrics: Using polymer dielectrics can create a more favorable interface with the organic semiconductor compared to inorganic dielectrics like SiO<sub>2</sub>.

- Surface Modification: Treating the dielectric surface with a self-assembled monolayer (SAM), such as octadecyltrichlorosilane (OTS), can passivate surface traps, reduce surface energy, and promote the growth of a more ordered semiconductor film.[8]

- Using High-k Dielectrics: Employing high-k dielectrics can enable low-voltage operation and improve device performance.[11]

Question 4: What is contact resistance, and how can it be minimized in PDI-based OFETs?

#### Answer:

Contact resistance is the resistance to charge injection from the source/drain electrodes into the semiconductor channel.[3] It can be a significant limiting factor for OFET performance, especially in devices with short channel lengths.[4]

Methods to reduce contact resistance include:

Electrode Material Selection: Choosing metals with work functions that are well-matched with the LUMO of the n-type PDI semiconductor can lower the energy barrier for electron injection.

- Device Architecture: Top-contact architectures often exhibit lower contact resistance compared to bottom-contact architectures for PDI-based OFETs.[1]

- Interfacial Layers: Introducing a thin injection layer between the electrode and the semiconductor can reduce the contact barrier.

- Measurement Techniques: The transfer-line method (TLM) is a common technique used to accurately measure and quantify the contact resistance in OFETs.[17]

## **Data Presentation**

Table 1: Effect of Chemical Modifications on PDI Electron Mobility

| PDI Derivative                  | Modification<br>Strategy          | Electron Mobility<br>(cm²/V·s) | Reference |

|---------------------------------|-----------------------------------|--------------------------------|-----------|

| Parent PDI                      | -                                 | ~10 <sup>-4</sup>              | [13]      |

| Fully Thionated PDI             | Thionation                        | 0.16                           | [13]      |

| Tetra-bromo-<br>substituted PDI | Core Halogenation (surface doped) | 1.19 x 10 <sup>-2</sup>        | [18]      |

| P(PDI-DTT) Polymer              | Polymerization                    | 0.013                          | [19]      |

Table 2: Influence of Device Processing on Electron Mobility

| PDI Derivative | Processing<br>Condition            | Electron Mobility<br>(cm²/V·s) | Reference |

|----------------|------------------------------------|--------------------------------|-----------|

| PDI-C8,7       | As-prepared, bottom-<br>contact    | ~10 <sup>-6</sup>              | [1]       |

| PDI-C8,7       | Thermally annealed, bottom-contact | 7.4 x 10 <sup>-6</sup>         | [1]       |

| PDI-C8,7       | As-prepared, top-<br>contact       | 3.4 x 10 <sup>-5</sup>         | [1]       |

## **Experimental Protocols**

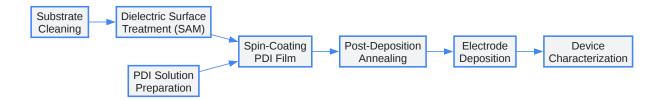

Protocol 1: Standard OFET Fabrication (Bottom-Gate, Top-Contact)

- Substrate Cleaning:

- Sequentially sonicate the Si/SiO<sub>2</sub> substrates in deionized water, acetone, and isopropanol for 15 minutes each.

- Dry the substrates with a stream of nitrogen gas.

- Treat the substrates with UV-ozone for 10 minutes to remove organic residues and create a hydrophilic surface.

- Dielectric Surface Modification (Optional but Recommended):

- Prepare a solution of a self-assembled monolayer (SAM), such as OTS, in an anhydrous solvent like toluene.

- Immerse the cleaned substrates in the SAM solution for the desired time (e.g., 12 hours)

in an inert atmosphere.

- Rinse the substrates with fresh solvent and anneal at a specified temperature (e.g., 120°C) to form a dense monolayer.

- PDI Solution Preparation:

- Dissolve the PDI derivative in a suitable high-purity organic solvent (e.g., chloroform, chlorobenzene) at a specific concentration (e.g., 5 mg/mL).

- Gently heat and stir the solution to ensure complete dissolution.

- Filter the solution through a 0.2 μm PTFE filter before use.

- Thin-Film Deposition:

- Spin-coat the PDI solution onto the prepared substrates at a specific spin speed and duration to achieve the desired film thickness.

- Transfer the substrates to a hotplate and anneal at a predetermined temperature (e.g., 100-150°C) to remove residual solvent and improve film morphology.

- Source/Drain Electrode Deposition:

- Use a shadow mask to define the source and drain electrodes.

- Thermally evaporate the desired metal (e.g., gold, silver) onto the PDI film under high vacuum. The deposition rate and final thickness should be carefully controlled.

- Device Characterization:

- Perform electrical characterization of the OFETs in an inert atmosphere or vacuum using a semiconductor parameter analyzer.

- Measure the output and transfer characteristics to extract key parameters like electron mobility, threshold voltage, and on/off ratio.

## **Visualizations**

Click to download full resolution via product page

Caption: Troubleshooting workflow for low electron mobility in PDI-based OFETs.

Click to download full resolution via product page

Caption: Experimental workflow for OFET fabrication and characterization.

Click to download full resolution via product page

Caption: Key factors influencing the electron mobility of PDI-based OFETs.

#### **Need Custom Synthesis?**

BenchChem offers custom synthesis for rare earth carbides and specific isotopiclabeling.

Email: info@benchchem.com or Request Quote Online.

## References

- 1. pubs.acs.org [pubs.acs.org]

- 2. researchgate.net [researchgate.net]

## Troubleshooting & Optimization

- 3. researchgate.net [researchgate.net]

- 4. researchgate.net [researchgate.net]

- 5. researchgate.net [researchgate.net]

- 6. fkf.mpg.de [fkf.mpg.de]

- 7. Engineering of the dielectric—semiconductor interface in organic field-effect transistors -Journal of Materials Chemistry (RSC Publishing) [pubs.rsc.org]

- 8. researchgate.net [researchgate.net]

- 9. researchgate.net [researchgate.net]

- 10. pubs.aip.org [pubs.aip.org]

- 11. tohoku.elsevierpure.com [tohoku.elsevierpure.com]

- 12. researchgate.net [researchgate.net]

- 13. researchgate.net [researchgate.net]

- 14. researchgate.net [researchgate.net]

- 15. nbinno.com [nbinno.com]

- 16. Morphology control strategies for solution-processed organic semiconductor thin films -Energy & Environmental Science (RSC Publishing) [pubs.rsc.org]

- 17. researchgate.net [researchgate.net]

- 18. Enhancing optoelectronic performance of organic phototransistors through surface doping of tetra-bromo perylene diimide single crystals Journal of Materials Chemistry C (RSC Publishing) [pubs.rsc.org]

- 19. pubs.acs.org [pubs.acs.org]

- To cite this document: BenchChem. [Technical Support Center: Enhancing Electron Mobility

of Perylene Diimides (PDIs) in OFETs]. BenchChem, [2025]. [Online PDF]. Available at:

[https://www.benchchem.com/product/b046583#enhancing-the-electron-mobility-of-perylenediimides-in-ofets]

#### **Disclaimer & Data Validity:**

The information provided in this document is for Research Use Only (RUO) and is strictly not intended for diagnostic or therapeutic procedures. While BenchChem strives to provide accurate protocols, we make no warranties, express or implied, regarding the fitness of this product for every specific experimental setup.

**Technical Support:**The protocols provided are for reference purposes. Unsure if this reagent suits your experiment? [Contact our Ph.D. Support Team for a compatibility check]

Need Industrial/Bulk Grade? Request Custom Synthesis Quote

## BenchChem

Our mission is to be the trusted global source of essential and advanced chemicals, empowering scientists and researchers to drive progress in science and industry. Contact

Address: 3281 E Guasti Rd

Ontario, CA 91761, United States

Phone: (601) 213-4426

Email: info@benchchem.com