# Technical Support Center: Enhancing Charge Carrier Mobility in Naphthalenediimide-Based OFETs

Author: BenchChem Technical Support Team. Date: December 2025

| Compound of Interest |                                             |           |

|----------------------|---------------------------------------------|-----------|

| Compound Name:       | 1,4,5,8-<br>Naphthalenetetracarboxylic acid |           |

| Cat. No.:            | B089546                                     | Get Quote |

This technical support center provides troubleshooting guides, frequently asked questions (FAQs), and detailed experimental protocols for researchers, scientists, and drug development professionals working with naphthalenediimide (NDI)-based Organic Field-Effect Transistors (OFETs). Our goal is to help you overcome common experimental challenges and systematically improve the electron mobility of your devices.

# Frequently Asked Questions (FAQs)

Q1: What are the primary factors that determine charge carrier mobility in NDI-based OFETs?

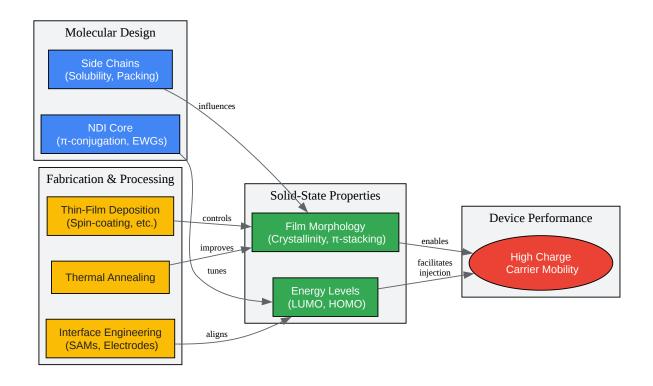

A1: The performance of NDI-based OFETs, particularly electron mobility ( $\mu$ ), is governed by a combination of factors at different scales. These can be broadly categorized as:

- Molecular Design: The intrinsic electronic properties of the NDI molecule or polymer are crucial. This includes extending π-conjugation, enhancing molecular planarity, and optimizing donor-acceptor structures.[1][2] Introducing electron-withdrawing groups can lower the LUMO energy level, which is beneficial for electron injection.[1][3]

- Thin-Film Morphology: The arrangement of molecules in the solid state is critical for efficient charge transport between molecules. Well-ordered structures, strong intermolecular aggregation, and reduced distances between molecules enhance mobility.[1][2] The degree

## Troubleshooting & Optimization

of crystallinity and the orientation of  $\pi$ - $\pi$  stacking relative to the charge transport direction significantly impact performance.

• Device Architecture and Interfaces: The choice of device geometry (e.g., bottom-gate, top-contact), the quality of the dielectric interface, and the charge injection barrier between the electrodes and the organic semiconductor are all important.[1][2] Proper alignment of the semiconductor's LUMO energy level with the work function of the electrodes is necessary to form an Ohmic contact and reduce the barrier for electron injection.[1]

Q2: How does modifying the NDI core and side chains affect electron mobility?

A2: Modifications to both the NDI core and its side chains provide powerful strategies for tuning device performance:

- Core Modification: Introducing electron-withdrawing groups (like fluorine or cyano groups) or

fusing other aromatic systems to the NDI core can lower the LUMO energy level, which

generally improves electron injection and ambient stability.[1][4] For instance, core-expanded

NDIs fused with 2-(1,3-dithiol-2-ylidene)malonitrile moieties have shown high electron

mobilities.[3]

- Side-Chain Engineering: Side chains play a critical role in balancing solubility and molecular packing. Long, branched alkyl chains can improve solubility for solution processing but may also hinder the close π-π stacking necessary for high mobility if they are too bulky.[5][6] The choice of side chain can influence the melting temperature and the overall crystallinity of the thin film.[7]

Q3: What is the importance of thermal annealing in the fabrication process?

A3: Thermal annealing is a critical post-deposition step that provides thermal energy to the molecules, allowing them to rearrange into a more ordered and thermodynamically stable morphology. For NDI-based polymers, annealing below the main chain melting temperature can improve the crystallinity of the thin film, leading to higher charge carrier mobility.[5] However, annealing at excessively high temperatures (above melting) can lead to amorphous morphologies and a complete loss of mobility.[5] The optimal annealing temperature and duration are material-specific and must be determined empirically.

Q4: Why is the choice of solvent crucial for solution-processed NDI-OFETs?

A4: For solution-processed films, the choice of solvent significantly influences the final thin-film morphology. The solvent's boiling point, viscosity, and its ability to dissolve the NDI material affect the drying rate and the degree of molecular aggregation during film formation. A solvent that promotes pre-aggregation in solution can sometimes lead to more ordered films and higher mobility. The solubility of the NDI derivative is a key practical consideration; for example, some derivatives exhibit excellent solubility of 30 mg/mL in solvents like 1,4-dioxane.[8]

## **Troubleshooting Guides**

This section addresses specific issues you may encounter during your experiments.

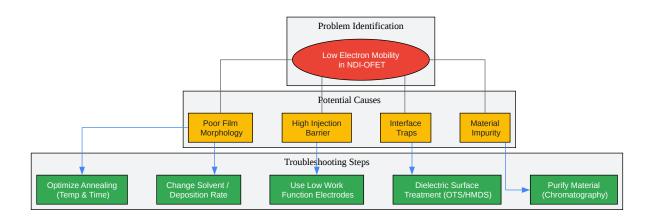

Issue 1: Very low or no measurable electron mobility.

## Troubleshooting & Optimization

Check Availability & Pricing

| Possible Cause                    | Suggested Solution                                                                                                                                                                                                                                                                                                          |

|-----------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Poor Film Morphology              | The organic semiconductor film may be amorphous or have a high density of grain boundaries. Optimize the deposition parameters (e.g., spin-coating speed, substrate temperature). Systematically vary the thermal annealing temperature and time to promote crystallinity.[5]                                               |

| High Injection Barrier            | There may be a large energy mismatch between the work function of your source/drain electrodes (e.g., Gold) and the LUMO of the NDI semiconductor. Use lower work function metals (e.g., Calcium, Aluminum) or treat the electrode surfaces with a suitable self-assembled monolayer (SAM) to reduce the injection barrier. |

| Traps at the Dielectric Interface | The surface of the SiO <sub>2</sub> dielectric can have charge-trapping sites (e.g., silanol groups).  Treat the dielectric surface with a hydrophobic layer like HMDS or OTS to passivate these traps and improve molecular ordering.                                                                                      |

| Material Degradation              | N-type organic semiconductors can be sensitive to ambient conditions (oxygen, moisture).  Ensure all fabrication and measurement steps are performed in an inert environment (e.g., a glovebox).[10]                                                                                                                        |

| Incorrect Gate Contact            | For bottom-gate devices using doped silicon wafers, ensure the native oxide on the backside is removed to establish a good electrical contact to the gate.[11]                                                                                                                                                              |

Issue 2: High OFF-current and low ON/OFF ratio.

## Troubleshooting & Optimization

Check Availability & Pricing

| Possible Cause       | Suggested Solution                                                                                                                                                                                                                                   |

|----------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Bulk Conduction      | The semiconductor film might be too thick, leading to significant current flow through the bulk of the material that is not modulated by the gate voltage. Reduce the film thickness by adjusting solution concentration or spin-coating parameters. |

| Gate Leakage Current | The dielectric layer may have pinholes or be of poor quality, allowing current to leak from the gate to the channel. Verify the quality of your dielectric layer. For thermally grown SiO <sub>2</sub> , ensure it is of high quality.               |

| Material Impurities  | Impurities in the synthesized NDI material can act as dopants, increasing the off-current. Purify your material thoroughly using techniques like column chromatography, sublimation, or recrystallization.                                           |

Issue 3: Poor film quality (cracks, dewetting).

| Possible Cause          | Suggested Solution                                                                                                                                                                                                                                                                                                                                                                        |  |

|-------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Surface Energy Mismatch | The NDI solution may not wet the substrate properly due to a mismatch in surface energies.  Clean the substrate meticulously (e.g., sonication in acetone, IPA, DI water) and consider a surface treatment (e.g., UV-Ozone, HMDS/OTS) to modify its surface energy.[12]                                                                                                                   |  |

| High Internal Stress    | Stress can build up in the film during solvent evaporation, leading to cracks, especially for highly crystalline materials. Slowing down the solvent evaporation rate (e.g., by using a solvent with a higher boiling point or by drying in a solvent vapor atmosphere) can help. Introducing more flexible moieties into the polymer backbone can also improve mechanical robustness.[7] |  |

# **Quantitative Data Summary**

The following tables summarize the performance of various NDI-based semiconductors reported in the literature.

Table 1: Performance of Selected NDI-based Polymers in OFETs

| Polymer<br>Name    | Electron<br>Mobility<br>(µe)<br>(cm²/Vs) | ON/OFF<br>Ratio | Deposition<br>Method | Annealing<br>Temp. (°C)  | Reference |

|--------------------|------------------------------------------|-----------------|----------------------|--------------------------|-----------|

| P(NDI2OD-<br>TVT)  | 2.31                                     | -               | -                    | -                        |           |

| P(NDI-IDT)         | ~10 <sup>-3</sup>                        | -               | -                    | Below main chain melting | [5]       |

| PCPCNI-Tz          | -                                        | -               | -                    | -                        |           |

| p(C3-gNDI-<br>gT2) | -                                        | -               | -                    | -                        | [12]      |

Table 2: Performance of Selected NDI-based Small Molecules in OFETs

| Molecule<br>Name            | Electron<br>Mobility<br>(µe)<br>(cm²/Vs) | ON/OFF<br>Ratio     | Deposition<br>Method                      | Annealing<br>Temp. (°C) | Reference |

|-----------------------------|------------------------------------------|---------------------|-------------------------------------------|-------------------------|-----------|

| Core-<br>chlorinated<br>NDI | Up to 8.6                                | -                   | -                                         | -                       | [3]       |

| NDI-4CI                     | 7.21 x 10 <sup>-3</sup>                  | -                   | Air-water<br>interfacial<br>self-assembly | -                       | [4]       |

| NDI-4F                      | 4.49 x 10 <sup>-3</sup>                  | -                   | Air-water<br>interfacial<br>self-assembly | -                       | [4]       |

| TQ-f-NDIs                   | 0.03                                     | 2 x 10 <sup>5</sup> | Dip-coating                               | -                       | [13]      |

| NDI-s-Bu                    | 0.16                                     | -                   | -                                         | -                       | [14]      |

| gNDI-Br <sub>2</sub>        | 6.4 x 10 <sup>-4</sup>                   | -                   | Drop-casting                              | 40                      | [12]      |

## **Experimental Protocols**

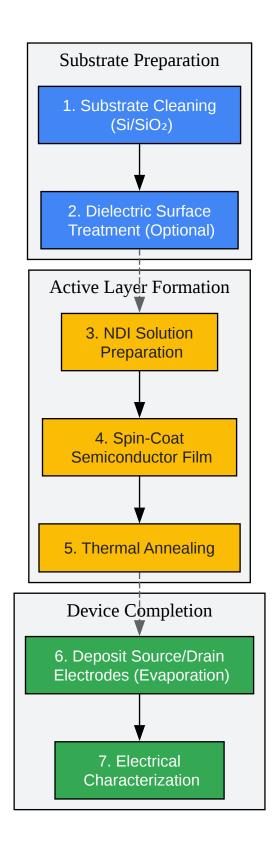

Protocol 1: Fabrication of a Bottom-Gate, Top-Contact (BGTC) OFET

- Substrate Cleaning: Use a heavily n-doped silicon wafer with a 300 nm thermally grown SiO<sub>2</sub> layer as the substrate, where the silicon acts as the gate and the SiO<sub>2</sub> as the dielectric.

Sonicate the substrate sequentially in acetone, isopropanol (IPA), and deionized (DI) water for 10-15 minutes each.[12] Dry the substrate with a stream of nitrogen gas.

- Dielectric Surface Treatment (Optional but Recommended): To improve the dielectric/semiconductor interface, treat the SiO<sub>2</sub> surface with a self-assembled monolayer (SAM) like octadecyltrichlorosilane (OTS) or hexamethyldisilazane (HMDS). This passivates surface traps and promotes better molecular ordering of the NDI film.

- Semiconductor Deposition: Dissolve the NDI-based material in a suitable high-purity organic solvent (e.g., chloroform, chlorobenzene) at a specific concentration (e.g., 5-10 mg/mL).

Deposit the thin film onto the substrate using spin-coating. The spin speed and time will determine the film thickness and should be optimized.

- Thermal Annealing: Transfer the sample to a hotplate in an inert atmosphere (e.g., inside a

nitrogen-filled glovebox). Anneal the film at a predetermined temperature and for a specific

duration to improve its crystallinity.[5] The optimal temperature is material-dependent and

should be below the material's melting point.

- Electrode Deposition: Using a shadow mask to define the source and drain electrodes, thermally evaporate 40-50 nm of Gold (or another suitable metal) on top of the semiconductor film. The channel length (L) and width (W) are defined by the shadow mask.

- Gate Contact: Carefully scratch a small area on the backside of the silicon wafer to remove the native oxide layer and ensure a good electrical contact for the gate probe.[11]

Protocol 2: OFET Characterization and Mobility Calculation

Measurement Setup: Place the fabricated device on the chuck of a semiconductor probe station inside an inert environment. Use micromanipulators to land probes on the source, drain, and gate contacts.

- Data Acquisition: Connect the probes to a semiconductor parameter analyzer (e.g., Keithley 4200-SCS).

- Output Characteristics: Measure the drain current (I\_D) as a function of the drain-source voltage (V\_DS) at various constant gate-source voltages (V\_GS). This will show the linear and saturation regimes of transistor operation.

- Transfer Characteristics: Measure I\_D as a function of V\_GS at a constant, high V\_DS (in the saturation regime). Plot both log(I\_D) vs. V\_GS (to determine the ON/OFF ratio) and (I\_D)^1/2 vs. V\_GS.

- Mobility Calculation: The field-effect mobility in the saturation regime (μ\_sat) can be calculated from the slope of the linear portion of the (I\_D)^1/2 vs. V\_GS plot using the following equation:

$$I_D = (W / 2L) * \mu_sat * C_i * (V_GS - V_th)^2$$

#### Where:

- W is the channel width.

- L is the channel length.

- o C\_i is the capacitance per unit area of the gate dielectric (for 300 nm SiO₂, C\_i ≈ 11.5 nF/cm²).

- V\_th is the threshold voltage, determined by extrapolating the linear fit of the (I\_D)^1/2 vs.

V\_GS plot to the V\_GS axis.

## **Visualizations**

Click to download full resolution via product page

Caption: Troubleshooting workflow for low electron mobility in NDI-OFETs.

Click to download full resolution via product page

Caption: Key relationships for enhancing NDI-OFET charge carrier mobility.

Click to download full resolution via product page

Caption: Experimental workflow for fabricating a BGTC NDI-based OFET.

#### **Need Custom Synthesis?**

BenchChem offers custom synthesis for rare earth carbides and specific isotopiclabeling.

Email: info@benchchem.com or Request Quote Online.

### References

- 1. mdpi.com [mdpi.com]

- 2. Molecular Design Concept for Enhancement Charge Carrier Mobility in OFETs: A Review PubMed [pubmed.ncbi.nlm.nih.gov]

- 3. Conjoint use of Naphthalene Diimide and Fullerene Derivatives to Generate Organic Semiconductors for n-type Organic Thin Film Transistors PMC [pmc.ncbi.nlm.nih.gov]

- 4. researchgate.net [researchgate.net]

- 5. Temperature-dependent morphology-electron mobility correlations of naphthalene diimide-indacenodithiophene copolymers prepared via direct arylation po ... Materials Advances (RSC Publishing) DOI:10.1039/D1MA00633A [pubs.rsc.org]

- 6. nbinno.com [nbinno.com]

- 7. osti.gov [osti.gov]

- 8. researchgate.net [researchgate.net]

- 9. pubs.acs.org [pubs.acs.org]

- 10. researchgate.net [researchgate.net]

- 11. reddit.com [reddit.com]

- 12. Naphthalene diimide-based n-type small molecule organic mixed conductors for accumulation mode organic electrochemical transistors - PMC [pmc.ncbi.nlm.nih.gov]

- 13. pubs.acs.org [pubs.acs.org]

- 14. Electron Transport in Naphthalene Diimide Derivatives PMC [pmc.ncbi.nlm.nih.gov]

- To cite this document: BenchChem. [Technical Support Center: Enhancing Charge Carrier Mobility in Naphthalenediimide-Based OFETs]. BenchChem, [2025]. [Online PDF]. Available at: [https://www.benchchem.com/product/b089546#enhancing-the-charge-carrier-mobility-in-naphthalenediimide-based-ofets]

#### **Disclaimer & Data Validity:**

The information provided in this document is for Research Use Only (RUO) and is strictly not intended for diagnostic or therapeutic procedures. While BenchChem strives to provide accurate protocols, we make no warranties, express or implied, regarding the fitness of this product for every specific experimental setup.

**Technical Support:** The protocols provided are for reference purposes. Unsure if this reagent suits your experiment? [Contact our Ph.D. Support Team for a compatibility check]

Need Industrial/Bulk Grade? Request Custom Synthesis Quote

# BenchChem

Our mission is to be the trusted global source of essential and advanced chemicals, empowering scientists and researchers to drive progress in science and industry.

#### Contact

Address: 3281 E Guasti Rd

Ontario, CA 91761, United States

Phone: (601) 213-4426

Email: info@benchchem.com