# Technical Support Center: Dibenzo[g,p]chrysene (DBC) Electronic Devices

Author: BenchChem Technical Support Team. Date: December 2025

| Compound of Interest |                                 |           |  |  |  |

|----------------------|---------------------------------|-----------|--|--|--|

| Compound Name:       | Tetraphenyldibenzoperiflanthene |           |  |  |  |

| Cat. No.:            | B1602332                        | Get Quote |  |  |  |

This technical support center provides troubleshooting guidance and frequently asked questions (FAQs) for researchers and scientists working with dibenzo[g,p]chrysene (DBC) and its derivatives in electronic devices.

## Frequently Asked Questions (FAQs)

Q1: What are the typical charge transport characteristics of dibenzo[g,p]chrysene (DBC)?

Dibenzo[g,p]chrysene (DBC) is a polycyclic aromatic hydrocarbon with a twisted molecular structure that is being explored for applications in organic electronics.[1][2] Depending on the specific derivative and device architecture, DBC-based materials can exhibit p-type, n-type, or ambipolar behavior. Their twisted nature can influence molecular packing, which in turn significantly affects charge transport properties.[1] For instance, certain derivatives of a related compound, dibenzo[a,e]pentalene, have demonstrated high hole mobility.[3]

Q2: How does the molecular structure of DBC derivatives affect device performance?

The electronic properties of DBC derivatives can be tuned by chemical modification. The position and nature of substituent groups on the DBC core can significantly alter the frontier molecular orbital (HOMO/LUMO) energy levels, which directly impacts the efficiency of charge injection from the electrodes.[1][4] Additionally, substituents influence the intermolecular interactions and solid-state packing, which are crucial for efficient charge transport through the thin film.[5] For example, alkyl chain engineering in similar polycyclic aromatic hydrocarbons

has been shown to influence the molecular arrangement and, consequently, the charge carrier mobility.[5]

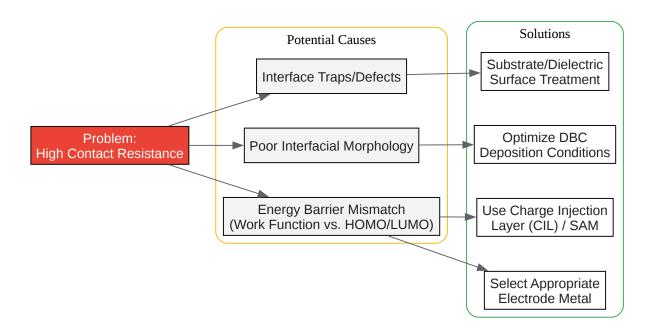

Q3: What is a major factor limiting the performance of my DBC-based Organic Field-Effect Transistor (OFET)?

A primary limiting factor in OFET performance is often the contact resistance at the interface between the source/drain electrodes and the organic semiconductor.[6] This resistance can impede charge injection and lead to an underestimation of the material's intrinsic mobility. The energy barrier for charge injection is determined by the difference between the work function of the electrode metal and the corresponding frontier orbital (HOMO for p-type, LUMO for n-type) of the DBC derivative.[7]

Q4: Can thermal annealing improve the performance of my DBC devices?

Yes, thermal annealing is a common post-processing step used to improve the performance of organic electronic devices.[8][9] Annealing can enhance the crystallinity and molecular ordering within the DBC thin film, leading to improved charge transport pathways and higher carrier mobility.[8][9] The optimal annealing temperature and duration are material-specific and need to be determined experimentally, as excessive heat can lead to device degradation.[10][11]

## **Troubleshooting Guide**

## Troubleshooting & Optimization

Check Availability & Pricing

| Issue                                                                  | Potential Cause                                                                                                                                                                                  | Suggested Solution                                                                                                                                                                                                                                                                                     |

|------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Low Carrier Mobility                                                   | Poor molecular ordering in the DBC thin film.                                                                                                                                                    | Optimize the deposition parameters (e.g., substrate temperature, deposition rate).  Perform post-deposition thermal annealing to improve crystallinity.[8][9]                                                                                                                                          |

| High density of trap states at the dielectric-semiconductor interface. | Choose a dielectric with a low density of surface traps. Treat the dielectric surface with a self-assembled monolayer (SAM) to reduce traps and improve molecular ordering.  [12]                |                                                                                                                                                                                                                                                                                                        |

| High Contact Resistance                                                | Large energy barrier for charge injection between the electrode and the DBC layer.                                                                                                               | Select an electrode material with a work function that closely matches the HOMO (for p-type) or LUMO (for n-type) level of your DBC derivative.[7] Insert a thin charge injection layer (e.g., a self-assembled monolayer) to modify the electrode work function and reduce the injection barrier.[13] |

| Poor physical contact between the electrode and the semiconductor.     | In bottom-contact devices, ensure the DBC film effectively covers the electrode edges. For top-contact devices, optimize the metal deposition to prevent penetration into the organic layer.[14] |                                                                                                                                                                                                                                                                                                        |

| High "Off" Current / Low<br>On/Off Ratio                               | Impurities in the DBC material.                                                                                                                                                                  | Purify the DBC material using techniques like sublimation or                                                                                                                                                                                                                                           |

|                                                                                   |                                                                                                                                                        | chromatography before device fabrication.                                                                                                                                                                           |

|-----------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Gate leakage through the dielectric layer.                                        | Ensure the integrity of the gate dielectric layer. Optimize the dielectric deposition process to minimize pinholes.                                    |                                                                                                                                                                                                                     |

| Device Instability in Air                                                         | Sensitivity of the DBC material to oxygen and/or moisture.                                                                                             | Encapsulate the device to protect it from the ambient environment. For n-type materials, which are often more sensitive, ensure that the LUMO level is sufficiently low (< -4 eV) to improve ambient stability.[15] |

| Poor Film Morphology (e.g., dewetting, island formation)                          | Mismatch between the surface energy of the substrate and the DBC material.                                                                             | Modify the substrate surface with a suitable self-assembled monolayer (SAM) to improve wettability and promote uniform film growth.[16][17]                                                                         |

| Sub-optimal solution-<br>processing parameters (for<br>solution-deposited films). | Adjust the solvent, solution concentration, and deposition technique (e.g., spin coating speed, blade coating speed) to achieve a uniform film.[5][18] |                                                                                                                                                                                                                     |

## **Quantitative Data Summary**

The performance of DBC-based OFETs is highly dependent on the specific molecular derivative, device architecture, and fabrication conditions. The following table summarizes reported performance metrics for some DBC derivatives and related compounds to provide a general benchmark.

| Material                                                    | Device<br>Architecture                  | Hole Mobility<br>(µh) (cm²/V·s) | On/Off Ratio | Reference |

|-------------------------------------------------------------|-----------------------------------------|---------------------------------|--------------|-----------|

| TEP (a Dibenzo[a,e]pent alene derivative)                   | Single-crystal<br>OFET                  | up to 1.02                      | -            | [3]       |

| OSDP (a<br>Dibenzo[a,e]pent<br>alene derivative)            | Single-crystal<br>OFET                  | ~0.1                            | -            | [3]       |

| C12-DBA-C12 (a<br>Dibenzo[a,h]anth<br>racene<br>derivative) | Solution-<br>processed,<br>blade-coated | up to 2.97                      | > 106        | [5]       |

| Cy5-DBA-Cy5 (a<br>Dibenzo[a,h]anth<br>racene<br>derivative) | Solution-<br>processed,<br>blade-coated | ~0.45                           | -            | [5]       |

Note: This table includes data from related polycyclic aromatic hydrocarbons to provide a broader context for expected performance, due to the limited availability of comprehensive data specifically for dibenzo[g,p]chrysene OFETs.

## **Experimental Protocols**

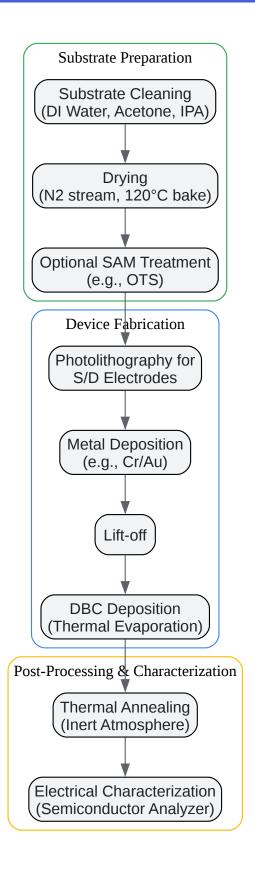

## General Protocol for Bottom-Contact, Top-Gate DBC OFET Fabrication

This protocol provides a general framework. Optimal parameters such as layer thicknesses, deposition rates, and annealing conditions should be determined experimentally for each specific DBC derivative.

#### a. Substrate Preparation:

• Start with a heavily doped silicon wafer with a thermally grown silicon dioxide (SiO<sub>2</sub>) layer (e.g., 300 nm), which will serve as the gate electrode and gate dielectric, respectively.

- Clean the substrate sequentially in an ultrasonic bath with deionized water, acetone, and isopropanol for 15 minutes each.

- Dry the substrate with a stream of dry nitrogen and then bake on a hotplate at 120°C for 10 minutes to remove residual moisture.

- (Optional but recommended) Treat the SiO<sub>2</sub> surface with a self-assembled monolayer (SAM), such as octadecyltrichlorosilane (OTS), to improve the dielectric-semiconductor interface and promote better molecular ordering of the DBC film.

- b. Source/Drain Electrode Patterning:

- Use standard photolithography to define the source and drain electrode patterns.

- Deposit a thin adhesion layer (e.g., 5 nm of Cr or Ti) followed by the electrode metal (e.g., 30-50 nm of Au) using thermal or e-beam evaporation.

- Perform a lift-off process in a suitable solvent (e.g., acetone) to remove the photoresist and define the electrodes.

- c. DBC Thin Film Deposition:

- Place the patterned substrate in a high-vacuum thermal evaporator.

- Deposit the DBC material at a controlled rate (e.g., 0.1-0.5 Å/s) onto the substrate, which is held at a specific temperature (e.g., room temperature or an elevated temperature to improve film morphology). The final film thickness is typically in the range of 30-60 nm.

- d. Post-Deposition Annealing:

- Transfer the substrate to a glovebox or another inert environment.

- Anneal the sample on a hotplate at a temperature below the material's decomposition or significant phase transition temperature (e.g., 80-150°C) for a specified time (e.g., 30-60 minutes).

- e. Device Characterization:

- Use a semiconductor parameter analyzer to measure the transfer and output characteristics of the OFETs in an inert atmosphere or vacuum.

- Extract key performance metrics such as carrier mobility, on/off ratio, and threshold voltage from the electrical characteristics.

## **Visualizations**

Click to download full resolution via product page

Caption: Workflow for fabricating bottom-contact DBC OFETs.

Click to download full resolution via product page

Caption: Troubleshooting logic for high contact resistance in DBC devices.

#### **Need Custom Synthesis?**

BenchChem offers custom synthesis for rare earth carbides and specific isotopiclabeling.

Email: info@benchchem.com or Request Quote Online.

### References

- 1. pubs.rsc.org [pubs.rsc.org]

- 2. BJOC Electrochemical and spectroscopic properties of twisted dibenzo[g,p]chrysene derivatives [beilstein-journals.org]

- 3. researchgate.net [researchgate.net]

## Troubleshooting & Optimization

- 4. π-Extended dibenzo[g,p]chrysenes Organic Chemistry Frontiers (RSC Publishing) [pubs.rsc.org]

- 5. Dialkylated dibenzo[a,h]anthracenes for solution-processable organic thin-film transistors PMC [pmc.ncbi.nlm.nih.gov]

- 6. fkf.mpg.de [fkf.mpg.de]

- 7. researchgate.net [researchgate.net]

- 8. researchgate.net [researchgate.net]

- 9. Evolving Morphology and Excited State Dynamics During Deposition and Thermal Annealing of Organic Thin Films [scholarsbank.uoregon.edu]

- 10. OASIS Repository@POSTECHLIBRARY: Thermally Stable Dibenzo[def,mno]chrysene-Based Polymer Solar Cells: Effect of Thermal Annealing on the Morphology and Photovoltaic Performances [poasis.postech.ac.kr]

- 11. researchgate.net [researchgate.net]

- 12. scispace.com [scispace.com]

- 13. yonsei.elsevierpure.com [yonsei.elsevierpure.com]

- 14. pubs.acs.org [pubs.acs.org]

- 15. Ambient stable solution-processed organic field effect transistors from electron deficient planar aromatics: effect of end-groups on ambient stability PMC [pmc.ncbi.nlm.nih.gov]

- 16. researchgate.net [researchgate.net]

- 17. scispace.com [scispace.com]

- 18. Solution-processed organic transistors based on semiconducting blends Journal of Materials Chemistry (RSC Publishing) [pubs.rsc.org]

- To cite this document: BenchChem. [Technical Support Center: Dibenzo[g,p]chrysene (DBC)

Electronic Devices]. BenchChem, [2025]. [Online PDF]. Available at:

[https://www.benchchem.com/product/b1602332#improving-charge-injection-and-transport-in-dbp-electronic-devices]

#### **Disclaimer & Data Validity:**

The information provided in this document is for Research Use Only (RUO) and is strictly not intended for diagnostic or therapeutic procedures. While BenchChem strives to provide accurate protocols, we make no warranties, express or implied, regarding the fitness of this product for every specific experimental setup.

**Technical Support:**The protocols provided are for reference purposes. Unsure if this reagent suits your experiment? [Contact our Ph.D. Support Team for a compatibility check]

Need Industrial/Bulk Grade? Request Custom Synthesis Quote

## BenchChem

Our mission is to be the trusted global source of essential and advanced chemicals, empowering scientists and researchers to drive progress in science and industry. Contact

Address: 3281 E Guasti Rd

Ontario, CA 91761, United States

Phone: (601) 213-4426

Email: info@benchchem.com