# Technical Support Center: Characterization of Trap States in Btqbt Semiconductors

Author: BenchChem Technical Support Team. Date: December 2025

This technical support center provides troubleshooting guidance and answers to frequently asked questions for researchers, scientists, and drug development professionals working on the characterization of trap states in dibenzo[b,i]thianthrene (**Btqbt**) and other related organic semiconductors.

### Frequently Asked Questions (FAQs)

Q1: What are trap states in organic semiconductors, and why are they important?

A1: Trap states are localized electronic states within the bandgap of a semiconductor that can immobilize charge carriers (electrons or holes).[1][2] These states arise from various sources, including structural defects, chemical impurities, and disorder at interfaces.[3][4][5] The presence, density, and energetic distribution of trap states are critically important as they strongly influence the electrical characteristics of devices like organic field-effect transistors (OFETs).[4] They can reduce charge carrier mobility, increase the subthreshold swing, cause hysteresis in current-voltage characteristics, and limit the overall performance and stability of the device.[2][5][6]

Q2: What are the common origins of trap states in solution-processed **Btqbt** semiconductor films?

A2: Trap states in organic semiconductors can be broadly categorized as intrinsic or extrinsic.

### Troubleshooting & Optimization

- Intrinsic traps are related to the inherent structural disorder of the material. In polycrystalline films, grain boundaries are a major source of trap states.[3] Thermal motion of the molecules can also introduce dynamic disorder, leading to shallow trap states.[3][4]

- Extrinsic traps originate from external sources. These include chemical impurities within the semiconductor material, adsorbed molecules like water and oxygen from the ambient environment, and defects at the interface between the semiconductor and the gate dielectric.

[3][5] The surface treatment of the dielectric layer can significantly impact the density of these interfacial traps.

Q3: Which experimental techniques are most suitable for characterizing trap states?

A3: A variety of experimental techniques can be used to indirectly probe the density of trap states (DOS).[4] Commonly used methods include:

- Electrical measurements on Field-Effect Transistors (FETs): Analyzing the transfer characteristics (drain current vs. gate voltage) of an OFET, particularly its temperature dependence, can be used to calculate the trap DOS.[3][8]

- Thermally Stimulated Current (TSC): This technique involves filling the trap states at a low temperature, and then heating the device at a constant rate while measuring the current released from the traps.[2][9] TSC is effective for determining trap density and their energetic distribution.[9]

- Impedance Spectroscopy (IS): By measuring the frequency-dependent capacitance and conductance of a device, the contribution of trap states can be identified, typically at low frequencies.[9][10][11]

- Space-Charge-Limited Current (SCLC) Measurements: This method involves analyzing the current-voltage characteristics of a device in the bulk-limited transport regime to extract information about trap density.[3]

- Other techniques include photoemission spectroscopy, Kelvin probe force microscopy, and electron spin resonance.[4]

Q4: My OFET transfer curve shows significant hysteresis. What are the likely causes?

A4: Hysteresis in the transfer characteristics of OFETs is a common issue and is often associated with charge trapping.[6] The most significant factor is often charge trapping and detrapping at or near the semiconductor/dielectric interface.[5] Other potential causes include mobile ions within the gate dielectric or the presence of adsorbates like water at the interface.

[6]

Q5: The transfer curve of my device doesn't show a clear "off-state" or threshold voltage. What could be the problem?

A5: An OFET that does not properly turn off (i.e., the current starts to increase immediately upon sweeping the gate voltage) may have a high density of trap states or a high level of unintentional doping.[6] This can lead to a significant off-current and a threshold voltage that is shifted outside the measurement window. The issue might also be related to the device architecture or fabrication process.[6]

Q6: There are multiple analytical methods to calculate the trap DOS from transistor characteristics. Which one should I use?

A6: Several analytical methods exist to extract the trap DOS from the transfer characteristics of an OFET, such as those developed by Grünewald, Horowitz, and Lang.[8][12] It is crucial to understand that the choice of method can have a considerable effect on the final result.[3][8] [12] Some methods make simplifying assumptions, such as neglecting the temperature dependence of the band mobility or assuming a constant accumulation layer thickness, which can lead to significant errors in the calculated trap DOS.[8][12] It is often advisable to use multiple methods and compare the results, or to use numerical simulations to validate the analytical extractions.[8][12]

## **Troubleshooting Common Issues**

## Troubleshooting & Optimization

Check Availability & Pricing

| Issue                                    | Possible Causes                                                                                                                                                          | Suggested Solutions                                                                                                                                                                                                                                                                                           |

|------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| High Subthreshold Swing (SS)             | High density of trap states at the semiconductor/dielectric interface or in the bulk of the semiconductor.[4][13]                                                        | - Improve the quality of the dielectric interface through surface treatments (e.g., using self-assembled monolayers).  [7]- Optimize the semiconductor deposition conditions to improve film morphology and reduce grain boundaries.[3]- Anneal the device post-fabrication to reduce structural defects.[14] |

| Low Charge Carrier Mobility              | High density of trap states that immobilize charge carriers. [2]Poor molecular ordering or morphology of the semiconductor film.[7]                                      | - Purify the Btqbt semiconductor material to reduce chemical impurities.[3]- Control the solvent evaporation rate during film deposition to enhance crystallinity.[14]- Perform measurements in an inert atmosphere (vacuum or nitrogen) to minimize the effect of environmental adsorbates. [6]              |

| Poor Device-to-Device<br>Reproducibility | Inconsistent film morphology across the substrate. Variations in the quality of the semiconductor/dielectric interface.[13]Contamination during the fabrication process. | - Ensure uniform substrate temperature during semiconductor deposition Standardize all fabrication steps, including cleaning procedures and surface treatments Fabricate and measure devices in a cleanroom environment to minimize contamination.                                                            |

|                                   |                             | - Use contact doping or       |

|-----------------------------------|-----------------------------|-------------------------------|

| Anomalous Kink in Output<br>Curve | Charge trapping at the      | appropriate metal work        |

|                                   | contacts or in the channel, | functions to improve charge   |

|                                   | especially at high drain    | injection Analyze the contact |

|                                   | voltages.Contact resistance | resistance using methods like |

|                                   | issues.                     | the transmission line method  |

|                                   |                             | (TLM).[13]                    |

## **Quantitative Data Summary**

The following tables summarize typical trap state parameters for small-molecule organic semiconductors, which can serve as a reference for evaluating results from **Btqbt**-based devices.

Table 1: Comparison of Parameters from Different Trap DOS Calculation Methods for Pentacene TFTs.[8]

| Method           | Characteristic<br>Energy (E₀) | Trap Density at<br>Band Edge (№)                              | Band Mobility (μο)      |

|------------------|-------------------------------|---------------------------------------------------------------|-------------------------|

| Grünewald et al. | 50 – 60 meV                   | $\sim$ 2 x 10 <sup>21</sup> eV <sup>-1</sup> cm <sup>-3</sup> | Estimated               |

| Horowitz et al.  | 50 – 60 meV                   | ~2 x 10 <sup>21</sup> eV <sup>-1</sup> cm <sup>-3</sup>       | Not directly determined |

| Lang et al.      | Underestimated slope          | Underestimated density                                        | Not directly determined |

| Simulation       | 50 – 60 meV                   | ~2 x 10 <sup>21</sup> eV <sup>-1</sup> cm <sup>-3</sup>       | ~2 cm²/Vs               |

Data adapted from a study on pentacene thin-film transistors and illustrates the variability between different analytical models.[8]

Table 2: Typical Trap State Parameters in Organic Semiconductors.

| Parameter                 | Typical Range                                                  | Semiconducto<br>r System                 | Technique                     | Reference |

|---------------------------|----------------------------------------------------------------|------------------------------------------|-------------------------------|-----------|

| Trap Density (Nt)         | > 8.7 x 10 <sup>16</sup> cm <sup>-3</sup>                      | DCV5T-Me:C <sub>60</sub><br>blend        | TSC                           | [9]       |

| Trap Density (Nt)         | $1.9 \pm 0.6 \times 10^{16}$ cm <sup>-3</sup> eV <sup>-1</sup> | ZnPc:C <sub>60</sub> bulk heterojunction | IS                            | [10]      |

| Activation<br>Energy (EA) | 16.1 meV                                                       | diF-TES ADT on<br>Cytop                  | Temperature-<br>dependent I-V | [13]      |

| Activation<br>Energy (EA) | 51.0 meV                                                       | diF-TES ADT on<br>SiO <sub>2</sub>       | Temperature-<br>dependent I-V | [13]      |

| Deep Trap<br>Energy (Et)  | 470 meV                                                        | DCV5T-Me:C <sub>60</sub><br>blend        | IS                            | [9]       |

## **Experimental Protocols**

Protocol 1: Trap DOS Extraction from Temperature-Dependent Transfer Characteristics

- Device Fabrication: Fabricate a bottom-gate, top-contact OFET with the **Btqbt** semiconductor.

- Measurement Setup: Place the device in a vacuum probe station with a temperature controller. Connect the source, drain, and gate terminals to a semiconductor parameter analyzer.

- Initial Measurement: Measure the transfer characteristics (ID vs. VGS) in the linear regime (low VDS) at room temperature.

- Temperature Cycling: Cool the device to a low temperature (e.g., 100 K) and allow it to stabilize.

- Data Acquisition: Measure the transfer characteristics at various temperatures as the device is slowly heated back to room temperature (e.g., in 20 K increments).

- Data Analysis:

- For each temperature, calculate the field-effect conductivity.

- Apply an appropriate analytical method (e.g., Grünewald's method) to the temperaturedependent data to extract the trap density of states N(E) as a function of energy E relative to the band edge.[4][8]

- The key principle is that as the gate voltage sweeps the Fermi level across the bandgap, charge carriers fill the trap states, and the temperature dependence reveals the energy distribution of these states.[4]

#### Protocol 2: Thermally Stimulated Current (TSC) Spectroscopy

- Device Preparation: The device (typically a metal-insulator-semiconductor structure) is mounted in a cryostat with electrical feedthroughs and a temperature controller.

- Trap Filling: Cool the device to a low starting temperature (e.g., 100 K). At this temperature, fill the trap states by applying a voltage pulse or by illuminating the sample with light of a specific wavelength.

- Stabilization: After the filling pulse, allow the device to stabilize in the dark to ensure that only trapped carriers remain.

- Thermal Ramp: Heat the sample at a constant, linear rate (e.g., 5-10 K/min).

- Current Measurement: While heating, measure the current flowing out of the device as a function of temperature. This current peak corresponds to the release of carriers from trap states.[2]

- Data Analysis: The shape and position of the peak in the TSC spectrum provide information about the trap parameters. The total charge extracted (the area under the peak) is proportional to the total trap density (Nt), and the peak temperature is related to the trap energy depth (Et).[2][9] The "initial rise" method can be used to determine the activation energy from the low-temperature side of the TSC peak.[9]

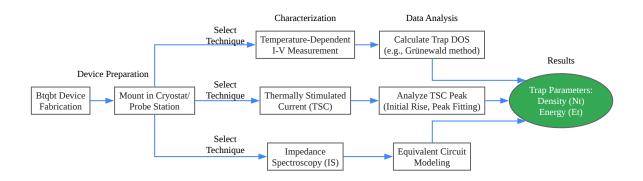

## **Diagrams and Visualizations**

Click to download full resolution via product page

Caption: Workflow for the characterization of trap states in **Btqbt** semiconductors.

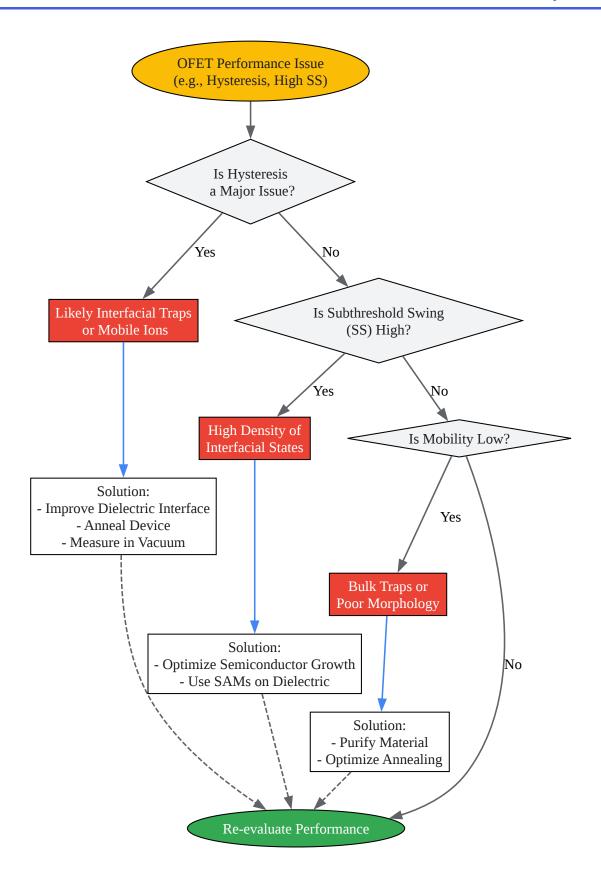

Click to download full resolution via product page

Caption: Decision tree for troubleshooting common OFET performance issues.

#### **Need Custom Synthesis?**

BenchChem offers custom synthesis for rare earth carbides and specific isotopiclabeling.

Email: info@benchchem.com or Request Quote Online.

#### References

- 1. apps.dtic.mil [apps.dtic.mil]

- 2. Quantifying Trap States in Perovskite & Organic Solar Cells | Fluxim Fluxim [fluxim.com]

- 3. journals.aps.org [journals.aps.org]

- 4. fkf.mpg.de [fkf.mpg.de]

- 5. mdpi.com [mdpi.com]

- 6. Reddit The heart of the internet [reddit.com]

- 7. Research Collection | ETH Library [research-collection.ethz.ch]

- 8. journals.aps.org [journals.aps.org]

- 9. tud.qucosa.de [tud.qucosa.de]

- 10. pubs.aip.org [pubs.aip.org]

- 11. researchgate.net [researchgate.net]

- 12. researchgate.net [researchgate.net]

- 13. pubs.aip.org [pubs.aip.org]

- 14. researchgate.net [researchgate.net]

- To cite this document: BenchChem. [Technical Support Center: Characterization of Trap States in Btqbt Semiconductors]. BenchChem, [2025]. [Online PDF]. Available at: [https://www.benchchem.com/product/b169727#characterization-of-trap-states-in-btqbt-semiconductors]

#### **Disclaimer & Data Validity:**

The information provided in this document is for Research Use Only (RUO) and is strictly not intended for diagnostic or therapeutic procedures. While BenchChem strives to provide

accurate protocols, we make no warranties, express or implied, regarding the fitness of this product for every specific experimental setup.

**Technical Support:** The protocols provided are for reference purposes. Unsure if this reagent suits your experiment? [Contact our Ph.D. Support Team for a compatibility check]

Need Industrial/Bulk Grade? Request Custom Synthesis Quote

### BenchChem

Our mission is to be the trusted global source of essential and advanced chemicals, empowering scientists and researchers to drive progress in science and industry. Contact

Address: 3281 E Guasti Rd

Ontario, CA 91761, United States

Phone: (601) 213-4426

Email: info@benchchem.com