# Technical Support Center: Anthra[2,3-b]thiophene-Based Organic Electronics

Author: BenchChem Technical Support Team. Date: December 2025

| Compound of Interest |                        |           |

|----------------------|------------------------|-----------|

| Compound Name:       | Anthra[2,3-b]thiophene |           |

| Cat. No.:            | B15350492              | Get Quote |

This technical support center provides troubleshooting guidance and frequently asked questions (FAQs) for researchers, scientists, and drug development professionals working with **Anthra[2,3-b]thiophene**-based organic electronics. The information is presented in a question-and-answer format to directly address common stability issues encountered during experimentation.

# **Troubleshooting Guides**

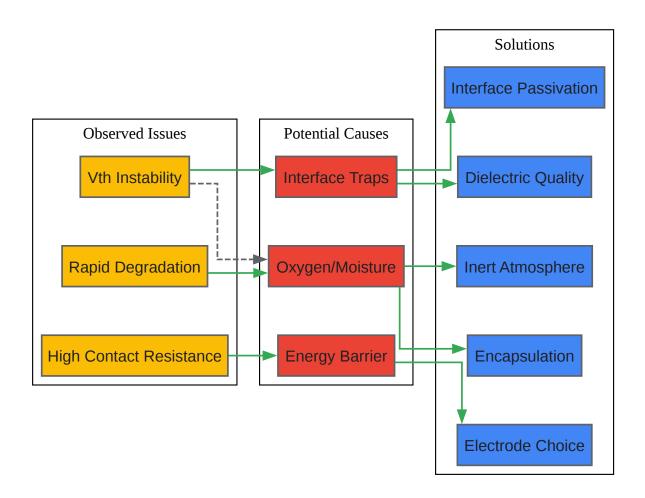

This section offers step-by-step guidance to diagnose and resolve common stability-related problems in your **Anthra[2,3-b]thiophene**-based organic field-effect transistors (OFETs).

## **Issue 1: Rapid Device Degradation in Ambient Air**

Q1: My OFET's performance (mobility, on/off ratio) degrades rapidly when exposed to air. What are the likely causes and how can I fix this?

A1: Rapid degradation in ambient air is a common issue for organic electronics and is primarily caused by environmental factors.

#### Possible Causes:

Oxygen Doping: Molecular oxygen can act as a p-dopant in organic semiconductors. While

this can sometimes initially increase conductivity, it often leads to an increase in the offcurrent and a positive shift in the threshold voltage, ultimately degrading device

performance.

- Moisture-Induced Traps: Water molecules from ambient humidity can be absorbed into the

organic semiconductor film or accumulate at the semiconductor-dielectric interface. This can

create charge traps, leading to a decrease in mobility and an increase in the subthreshold

swing.[1][2] In some cases, moisture can lead to a negative shift in the transfer curves,

suggesting the generation of hole traps.[1][2]

- Photo-oxidation: The combination of light and oxygen can lead to irreversible chemical degradation of the anthrathiophene core.

### **Troubleshooting Steps:**

- Encapsulation: The most effective solution is to prevent exposure to air and moisture.

Encapsulate your devices immediately after fabrication using materials with low water vapor and oxygen transmission rates, such as glass, metal foils, or specialized flexible barrier films.

- Inert Atmosphere: Whenever possible, fabricate and characterize your devices in an inert atmosphere, such as a nitrogen or argon-filled glovebox.

- Hydrophobic Dielectrics: Utilize hydrophobic gate dielectrics or surface treatments (e.g., self-assembled monolayers like OTS) to minimize moisture accumulation at the critical semiconductor-dielectric interface.

- Thermal Annealing: In some cases, thermal annealing in a vacuum or inert atmosphere after fabrication can help to remove absorbed water and improve the film morphology, which can enhance stability.

# Issue 2: High Contact Resistance and Non-Ideal Output Characteristics

Q2: My OFET shows "S-shaped" or non-linear output characteristics in the low Vds region, and the calculated mobility is lower than expected. What's causing this and how can I improve it?

A2: These are classic signs of high contact resistance at the source and drain electrodes. High contact resistance can significantly limit device performance, leading to an underestimation of the true charge carrier mobility.

#### Possible Causes:

- Energy Barrier: A significant energy barrier between the work function of the electrode metal and the HOMO level of the p-type anthrathiophene semiconductor can impede charge injection.

- Poor Interfacial Morphology: A rough or poorly defined interface between the organic semiconductor and the metal contacts can lead to inefficient charge injection.

- Contamination: Contaminants at the interface can create a barrier to charge injection.

#### **Troubleshooting Steps:**

- Electrode Material Selection: Choose electrode materials with a high work function (e.g., Gold (Au), Platinum (Pt), or PEDOT:PSS) to better match the HOMO level of the anthrathiophene derivative and facilitate hole injection.

- Contact Doping: Introduce a thin p-dopant layer between the semiconductor and the metal electrodes to reduce the charge injection barrier.

- Surface Treatment of Electrodes: Treating the electrode surfaces with self-assembled monolayers (SAMs) can improve the contact interface and reduce the injection barrier.

- Device Architecture: Top-contact, bottom-gate architectures often exhibit lower contact resistance compared to bottom-contact configurations because the semiconductor film is deposited first, allowing for a cleaner interface with the subsequently deposited electrodes.

- Annealing: Post-fabrication thermal annealing can sometimes improve the contact interface by promoting better adhesion and molecular ordering.

# Issue 3: Threshold Voltage Instability (Bias Stress Effect)

Q3: The threshold voltage of my device shifts significantly after prolonged operation (gate bias stress). How can I mitigate this instability?

A3: This phenomenon, known as the bias stress effect, is a common form of electronic instability in OFETs. It is often attributed to charge trapping in the dielectric, at the semiconductor-dielectric interface, or within the semiconductor itself.

#### Possible Causes:

- Charge Trapping in the Dielectric: Mobile ions or charge traps within the bulk of the gate dielectric can lead to a slow shift in the threshold voltage under a constant gate bias.

- Interfacial Traps: Defects and trap states at the semiconductor-dielectric interface are a primary cause of bias stress instability.

- Water and Oxygen: The presence of water and oxygen can exacerbate bias stress effects by creating additional trap states.[1][2]

## **Troubleshooting Steps:**

- High-Quality Dielectric: Use a high-quality, defect-free gate dielectric material. Amorphous fluoropolymers like CYTOP are often used to minimize charge trapping.

- Interface Passivation: Employ a passivation layer or a self-assembled monolayer (SAM) at the semiconductor-dielectric interface to reduce the density of trap states.

- Encapsulation and Inert Atmosphere: As with general degradation, preventing exposure to moisture and oxygen is crucial for improving bias stress stability.

- Pulsed Measurements: For characterization, consider using pulsed I-V measurements instead of continuous DC measurements to minimize the duration of the applied bias and reduce the impact of bias stress.

# Frequently Asked Questions (FAQs)

Q: What are typical mobility values for Anthra[2,3-b]thiophene-based OFETs?

A: The mobility can vary significantly depending on the specific derivative, device architecture, and fabrication conditions. Generally, mobilities in the range of 0.1 to over 1.0 cm²/Vs have been reported. For instance, 5,12-bis(tri-isopropylsilylethynyl)tetraceno[2,3-b]thiophene has shown mobilities as high as 1.25 cm²/Vs.[3]

Q: How does the thickness of the anthrathiophene film affect device stability and performance?

A: The film thickness is a critical parameter. Ultrathin films can be prone to morphological instabilities, where the film de-wets and forms disconnected islands, leading to a rapid decrease in mobility.[4] Thicker films are generally more stable morphologically. However, very thick films can sometimes lead to increased bulk resistance. An optimal thickness, typically in the range of 20-50 nm, is usually sought for a balance of good charge transport and stability.

Q: What is the effect of thermal annealing on device performance and stability?

A: Thermal annealing, typically performed in a vacuum or inert atmosphere, can have several positive effects. It can improve the crystallinity and molecular ordering of the semiconductor film, leading to higher mobility. It can also help to remove residual solvent and adsorbed water, which can improve device stability and reduce hysteresis. However, the annealing temperature and duration must be carefully optimized, as excessive heat can lead to film degradation or dewetting.

Q: How can I accurately measure and report the performance of my devices?

A: For accurate and reproducible results, it is crucial to follow best practices for OFET characterization. This includes:

- Reporting both the transfer (Id-Vg) and output (Id-Vds) characteristics.

- Clearly stating the method used to extract mobility (e.g., from the saturation or linear regime).

- Performing measurements on multiple devices and reporting the average and standard deviation of key parameters.

- Using a four-probe measurement technique, if possible, to eliminate the influence of contact resistance on mobility calculations.

## **Data Presentation**

Table 1: Impact of Environmental Conditions on DNTT-based OFET Performance

| Condition              | Change in On-<br>Current (I_on) | Threshold<br>Voltage (V_T)<br>Shift | Subthreshold<br>Swing (SS)               | Reference |

|------------------------|---------------------------------|-------------------------------------|------------------------------------------|-----------|

| Moist Air (in<br>dark) | ~10% decrease                   | Negative shift<br>(-2V to -4V)      | Increased (0.6<br>V/dec to 1.5<br>V/dec) | [2]       |

| Oxygen and<br>Light    | Stable in accumulation mode     | Positive shift in depletion mode    | -                                        | [1][2]    |

| Dry Air (in dark)      | Stable                          | Stable                              | Stable                                   | [1][2]    |

# **Experimental Protocols**

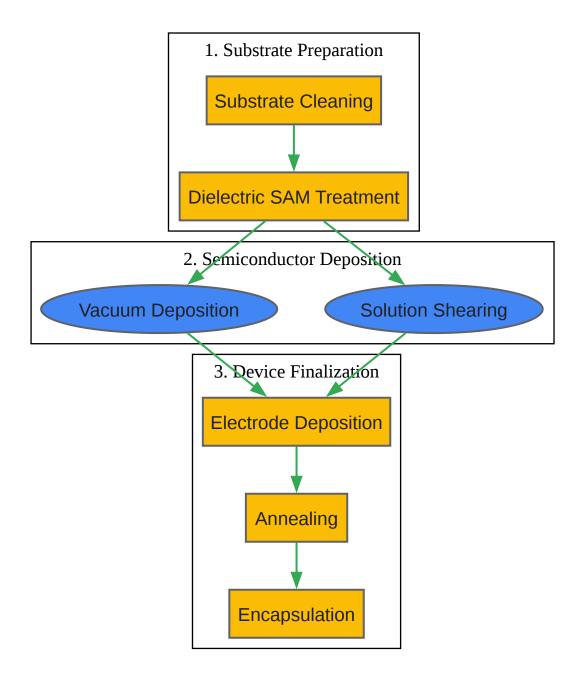

# Protocol 1: Fabrication of a Bottom-Gate, Top-Contact (BGTC) Anthra[2,3-b]thiophene-based OFET by Vacuum Deposition

- Substrate Cleaning:

- Begin with a heavily doped silicon wafer (acting as the gate electrode) with a thermally grown silicon dioxide (SiO<sub>2</sub>) layer (typically 200-300 nm) as the gate dielectric.

- Sonicate the substrate sequentially in deionized water, acetone, and isopropanol for 15 minutes each.

- Dry the substrate with a stream of dry nitrogen.

- Treat the SiO<sub>2</sub> surface with an oxygen plasma or a piranha solution to create a hydrophilic surface.

- Dielectric Surface Modification (Optional but Recommended):

- To improve the interface and promote ordered film growth, treat the SiO<sub>2</sub> surface with a self-assembled monolayer (SAM), such as octadecyltrichlorosilane (OTS). This is typically done by vapor or solution-phase deposition in a controlled environment.

#### · Semiconductor Deposition:

- Place the substrate in a high-vacuum thermal evaporator (base pressure  $< 10^{-6}$  Torr).

- Load the anthrathiophene material into a crucible.

- Heat the substrate to a desired temperature (e.g., 60-100 °C) to promote crystalline film growth.

- Deposit the anthrathiophene layer at a slow rate (e.g., 0.1-0.5 Å/s) to a final thickness of 30-50 nm, monitored by a quartz crystal microbalance.

- Source/Drain Electrode Deposition:

- Without breaking vacuum, allow the substrate to cool down.

- Place a shadow mask with the desired channel length and width over the substrate.

- Deposit the source and drain electrodes (e.g., 50 nm of Gold) through the shadow mask via thermal evaporation.

- Annealing and Encapsulation:

- Post-deposition, anneal the device in a vacuum or inert atmosphere at a moderate temperature (e.g., 80-120 °C) for 30-60 minutes.

- For enhanced stability, encapsulate the device before exposing it to ambient conditions.

# Protocol 2: Fabrication of a BGTC OFET by Solution Shearing

- Substrate and Dielectric Preparation:

- Prepare the Si/SiO<sub>2</sub> substrate and apply a surface modification (e.g., OTS) as described in Protocol 1. A hydrophobic surface is crucial for many solution-shearing processes.

- Solution Preparation:

- Dissolve the soluble anthrathiophene derivative in a suitable high-boiling-point organic solvent (e.g., chlorobenzene, dichlorobenzene) at a concentration of 5-10 mg/mL.

- Gently heat and stir the solution to ensure complete dissolution.

- Solution Shearing:

- Place the substrate on a heated stage (temperature will depend on the solvent and semiconductor).

- Dispense a small volume of the semiconductor solution onto the substrate near the edge of a shearing blade.

- Move the blade across the substrate at a constant, slow speed (e.g., 0.1-1.0 mm/s). The gap between the blade and the substrate is typically a few hundred micrometers.

- A thin, crystalline film of the organic semiconductor will be deposited as the solvent evaporates.

- Solvent Annealing and Thermal Annealing:

- After shearing, allow any residual solvent to evaporate.

- Perform a thermal anneal in an inert atmosphere to further improve film crystallinity.

- Electrode Deposition and Encapsulation:

- Deposit the source/drain electrodes through a shadow mask as described in Protocol 1.

- Encapsulate the final device.

# **Visualizations**

Click to download full resolution via product page

#### **Need Custom Synthesis?**

BenchChem offers custom synthesis for rare earth carbides and specific isotopiclabeling.

Email: info@benchchem.com or Request Quote Online.

# References

- 1. Organic Field-Effect Transistors (OFET) and Organic Electrochemical Transistors (OECT)

Fraunhofer IPMS [ipms.fraunhofer.de]

- 2. Unraveling Degradation Processes and Strategies for Enhancing Reliability in Organic Light-Emitting Diodes PMC [pmc.ncbi.nlm.nih.gov]

- 3. researchgate.net [researchgate.net]

- 4. pubs.aip.org [pubs.aip.org]

- To cite this document: BenchChem. [Technical Support Center: Anthra[2,3-b]thiophene-Based Organic Electronics]. BenchChem, [2025]. [Online PDF]. Available at: [https://www.benchchem.com/product/b15350492#stability-issues-in-anthra-2-3-b-thiophene-based-organic-electronics]

#### **Disclaimer & Data Validity:**

The information provided in this document is for Research Use Only (RUO) and is strictly not intended for diagnostic or therapeutic procedures. While BenchChem strives to provide accurate protocols, we make no warranties, express or implied, regarding the fitness of this product for every specific experimental setup.

**Technical Support:** The protocols provided are for reference purposes. Unsure if this reagent suits your experiment? [Contact our Ph.D. Support Team for a compatibility check]

Need Industrial/Bulk Grade? Request Custom Synthesis Quote

# BenchChem

Our mission is to be the trusted global source of essential and advanced chemicals, empowering scientists and researchers to drive progress in science and industry.

#### Contact

Address: 3281 E Guasti Rd

Ontario, CA 91761, United States

Phone: (601) 213-4426

Email: info@benchchem.com