# Technical Support Center: 2-Methoxytetracene Thin Films

Author: BenchChem Technical Support Team. Date: December 2025

| Compound of Interest |                    |           |

|----------------------|--------------------|-----------|

| Compound Name:       | 2-Methoxytetracene |           |

| Cat. No.:            | B2770009           | Get Quote |

Disclaimer: Scientific literature specifically detailing the reduction of trap states in **2- Methoxytetracene** thin films is limited. The following guide is based on established best practices for functionalized tetracenes and the broader class of organic semiconductors. These methodologies should serve as a robust starting point for your experimental design.

## Frequently Asked Questions (FAQs)

Q1: What are trap states and how do they affect my organic thin-film transistor (OTFT) performance?

A1: Trap states are localized electronic states within the band gap of a semiconductor material. In organic semiconductors like **2-Methoxytetracene**, they often arise from structural defects, impurities, or grain boundaries in the thin film. These states "trap" charge carriers (electrons or holes), immobilizing them and preventing them from contributing to the current. The primary effects of high trap state densities are:

- Reduced Carrier Mobility: Trapped charges scatter mobile carriers, lowering the overall device speed.

- Increased Threshold Voltage: A larger gate voltage is required to fill the trap states before the channel can accumulate free carriers and turn on.

- Large Subthreshold Swing: This indicates that a larger change in gate voltage is needed to switch the transistor from the "off" to the "on" state, leading to higher static power

consumption.

Q2: What is the most common cause of high trap state density in functionalized tetracene films?

A2: The most common cause is poor morphological control during the thin-film deposition process. Disordered molecular packing, small crystalline grain sizes, and the presence of numerous grain boundaries create a high density of structural defects that act as charge traps. Impurities from the source material or the deposition environment are also significant contributors.

Q3: Can the substrate surface influence trap states?

A3: Absolutely. The interface between the dielectric layer and the semiconductor is a critical region where trap states can form. A rough or chemically incompatible substrate surface can disrupt the initial layers of molecular growth, leading to a disordered film. Furthermore, hydroxyl groups (-OH) on untreated silicon dioxide (SiO2) surfaces are well-known charge trapping sites.

Q4: Is post-deposition annealing always effective for reducing trap states?

A4: While often beneficial, its effectiveness depends on the material and the specific annealing conditions (temperature, time, atmosphere). Thermal annealing can improve molecular ordering and increase grain size, which reduces the density of trap states at grain boundaries. However, excessively high temperatures can cause film dewetting or degradation. For some molecules, solvent vapor annealing may be a more effective, lower-temperature alternative for improving crystallinity.

## **Troubleshooting Guide**

| Observed Problem                                                | Potential Cause                                            | Suggested Solution                                                                                                                                                                                                                                             |

|-----------------------------------------------------------------|------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Low charge carrier mobility (< 0.1 cm²/Vs)                      | High density of bulk trap states; poor crystallinity.      | 1. Optimize deposition rate (< 0.5 Å/s) and substrate temperature. 2. Implement post-deposition thermal or solvent vapor annealing. 3. Verify purity of the 2-Methoxytetracene source material.                                                                |

| High threshold voltage (Vth > 5V)                               | High density of interface trap states.                     | 1. Treat the dielectric surface with a self-assembled monolayer (SAM) like HMDS or OTS to passivate trap sites and improve molecular ordering. 2. Use a different gate dielectric material with a lower density of surface traps (e.g., polymers like Cytop™). |

| Device performance degrades rapidly under bias stress or in air | Traps created by environmental factors (oxygen, water).    | 1. Perform all device fabrication and measurement steps in an inert atmosphere (e.g., a nitrogen-filled glovebox). 2. Encapsulate the final device to protect it from the ambient environment.                                                                 |

| Poor film uniformity and coverage                               | Sub-optimal deposition parameters; poor substrate wetting. | Ensure the substrate is meticulously cleaned. 2.  Modify the substrate surface energy using SAMs to promote layer-by-layer growth. 3. Adjust the deposition rate and substrate temperature.                                                                    |

# **Representative Quantitative Data**

The following tables present hypothetical, yet representative, data for a functionalized tetracene like **2-Methoxytetracene** to illustrate the impact of process optimization on device performance.

Table 1: Effect of Post-Deposition Annealing Temperature

| Annealing Temp. | Film Crystallinity<br>(XRD FWHM,<br>degrees) | Trap State Density<br>(Nt) (cm <sup>-2</sup> ) | Hole Mobility (µh)<br>(cm²/Vs) |

|-----------------|----------------------------------------------|------------------------------------------------|--------------------------------|

| As-deposited    | 0.85                                         | 5 x 10 <sup>12</sup>                           | 0.05                           |

| 60              | 0.62                                         | 2 x 10 <sup>12</sup>                           | 0.25                           |

| 90              | 0.45                                         | 8 x 10 <sup>11</sup>                           | 0.70                           |

| 120             | 0.58 (Degradation)                           | 3 x 10 <sup>12</sup>                           | 0.15                           |

Table 2: Effect of Dielectric Surface Treatment

| Surface Treatment          | Water Contact<br>Angle (°) | Trap State Density<br>(Nt) (cm <sup>-2</sup> ) | Hole Mobility (µh)<br>(cm²/Vs) |

|----------------------------|----------------------------|------------------------------------------------|--------------------------------|

| Untreated SiO <sub>2</sub> | 25°                        | 6 x 10 <sup>12</sup>                           | 0.08                           |

| HMDS-Treated               | 70°                        | 1.5 x 10 <sup>12</sup>                         | 0.45                           |

| OTS-Treated                | 110°                       | 7 x 10 <sup>11</sup>                           | 0.95                           |

# **Experimental Protocols**

Protocol 1: Substrate Cleaning and Surface Treatment

- Substrate: Use heavily n-doped silicon wafers with a 300 nm thermally grown SiO<sub>2</sub> layer.

- Cleaning:

- Ultrasonically clean the substrates sequentially in deionized water, acetone, and isopropanol for 15 minutes each.

- Dry the substrates under a stream of high-purity nitrogen gas.

- Treat with UV-Ozone for 10 minutes to remove organic residues and create a hydrophilic surface.

- Surface Treatment (OTS Deposition):

- Prepare a 10 mM solution of octadecyltrichlorosilane (OTS) in anhydrous toluene.

- Immerse the cleaned substrates in the OTS solution for 40 minutes inside a nitrogen-filled glovebox.

- Rinse the substrates with fresh toluene to remove excess OTS.

- Anneal the substrates at 120°C for 1 hour to form a dense monolayer.

#### Protocol 2: Thin-Film Deposition and Device Fabrication

#### Deposition:

- Place the surface-treated substrates into a high-vacuum thermal evaporator (base pressure  $< 5 \times 10^{-7}$  Torr).

- Deposit a 50 nm thin film of 2-Methoxytetracene at a rate of 0.2 Å/s. Maintain the substrate at an elevated temperature (e.g., 60°C) during deposition to promote crystalline growth.

#### Annealing:

- Transfer the samples to a hot plate inside a nitrogen glovebox.

- Anneal the films at the optimized temperature (e.g., 90°C, determined from studies like in Table 1) for 1 hour.

- Allow the films to cool slowly to room temperature.

#### Electrode Deposition:

Define the source and drain electrodes using a shadow mask.

• Deposit 50 nm of Gold (Au) to complete the top-contact, bottom-gate OTFT structure.

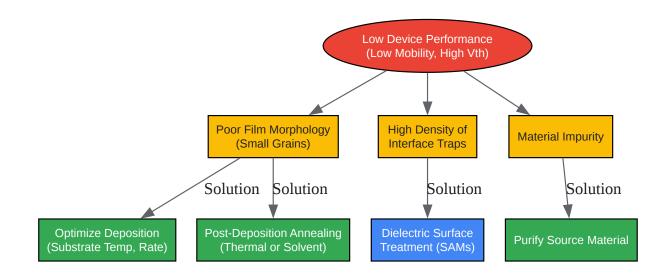

### **Visual Workflows and Relationships**

Click to download full resolution via product page

Caption: Workflow for fabricating and characterizing OTFTs to minimize trap states.

Click to download full resolution via product page

To cite this document: BenchChem. [Technical Support Center: 2-Methoxytetracene Thin Films]. BenchChem, [2025]. [Online PDF]. Available at: [https://www.benchchem.com/product/b2770009#reducing-trap-states-in-2-methoxytetracene-thin-films]

#### **Disclaimer & Data Validity:**

The information provided in this document is for Research Use Only (RUO) and is strictly not intended for diagnostic or therapeutic procedures. While BenchChem strives to provide accurate protocols, we make no warranties, express or implied, regarding the fitness of this product for every specific experimental setup.

**Technical Support:** The protocols provided are for reference purposes. Unsure if this reagent suits your experiment? [Contact our Ph.D. Support Team for a compatibility check]

Need Industrial/Bulk Grade? Request Custom Synthesis Quote

## BenchChem

Our mission is to be the trusted global source of essential and advanced chemicals, empowering scientists and researchers to drive progress in science and industry. Contact

Address: 3281 E Guasti Rd

Ontario, CA 91761, United States

Phone: (601) 213-4426

Email: info@benchchem.com