## Stannic Selenide (SnSe<sub>2</sub>) Device Integration: Technical Support Center

Author: BenchChem Technical Support Team. Date: December 2025

| Compound of Interest |                  |           |

|----------------------|------------------|-----------|

| Compound Name:       | Stannic selenide |           |

| Cat. No.:            | B1590759         | Get Quote |

This technical support center provides troubleshooting guidance and frequently asked questions (FAQs) for researchers, scientists, and professionals working on the integration of **stannic selenide** (SnSe<sub>2</sub>) in electronic and optoelectronic devices.

# Troubleshooting Guides & FAQs Category 1: Poor Device Performance

Q1: My SnSe<sub>2</sub> field-effect transistor (FET) has a very low on/off current ratio. What are the potential causes and how can I improve it?

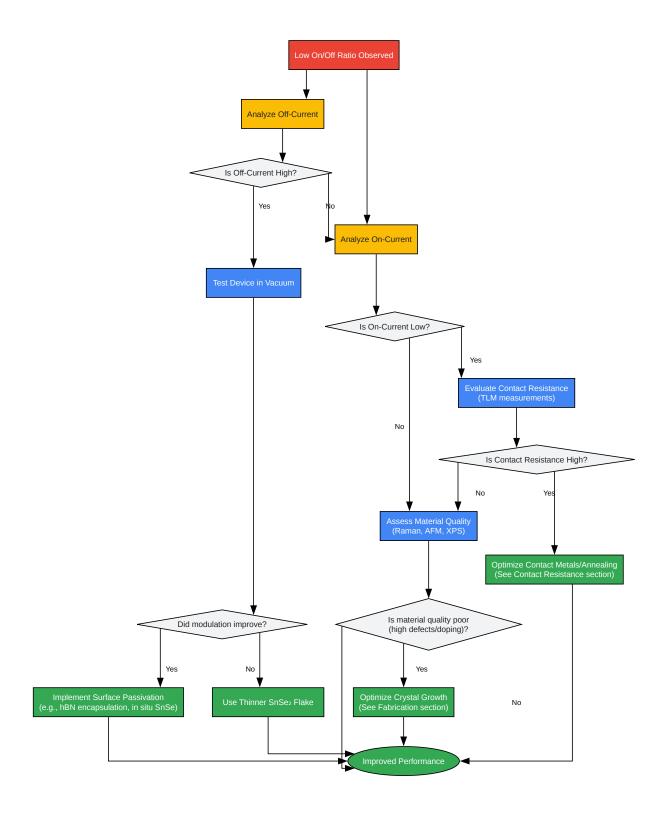

A1: A low on/off ratio in SnSe<sub>2</sub> FETs is a common issue that can stem from several factors:

- High Off-State Leakage Current: This can be caused by surface conduction or environmental

factors. Measurements in air often show poor current modulation. Performing measurements

in a vacuum can help determine if surface adsorbates are contributing to the leakage.

Improved surface passivation can also eliminate parallel conductance in ungated regions of

the device[1].

- Material Thickness: Thicker SnSe<sub>2</sub> layers can lead to poor gate modulation, as the gate has

less control over the entire channel. Using thinner SnSe<sub>2</sub> flakes is expected to improve the

on/off ratio[1].

- High Doping Density: Intrinsic or extrinsic dopants can lead to a high carrier concentration,

making the material behave more like a metal than a semiconductor and thus difficult to "turn

#### Troubleshooting & Optimization

Check Availability & Pricing

off". This can manifest as a high negative threshold voltage[2]. Improving crystal quality to reduce dopant concentration is a potential solution[2].

• Schottky Barriers: While not always significant with appropriate contact metals like Titanium (Ti)[1], a substantial Schottky barrier at the source/drain contacts can impede carrier injection, affecting the on-state current.

Troubleshooting Steps for Low On/Off Ratio:

Click to download full resolution via product page

**Caption:** Troubleshooting workflow for low on/off ratio in SnSe<sub>2</sub> devices.

#### Troubleshooting & Optimization

Q2: The carrier mobility in my SnSe<sub>2</sub> device is lower than expected. What factors limit mobility and how can I improve it?

A2: Low carrier mobility can be a significant hurdle. The primary limiting factors are:

- Phonon Scattering: At higher temperatures, phonon scattering is often the dominant factor limiting mobility in SnSe<sub>2</sub>[2]. This is an intrinsic property, but mobility can be observed to increase significantly as the temperature is lowered[1][2].

- Substrate Scattering: The interface between the SnSe<sub>2</sub> flake and the substrate (e.g., SiO<sub>2</sub>) can introduce scattering sites that degrade mobility[2]. Using high-quality substrates or encapsulating the SnSe<sub>2</sub> with materials like hexagonal boron nitride (hBN) can mitigate this issue[3].

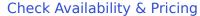

- Contact Resistance: High contact resistance can lead to an underestimation of the intrinsic mobility, especially in short-channel devices. It is crucial to de-embed the effect of contact resistance from device mobility calculations, for instance by using the transfer length method (TLM)[1][4].

- Crystal Quality: Defects and impurities within the SnSe<sub>2</sub> crystal can act as scattering centers for charge carriers, thereby reducing mobility[2][5].

#### **Category 2: High Contact Resistance**

Q1: I'm observing non-linear I-V characteristics and high contact resistance in my SnSe<sub>2</sub> devices. How can I achieve better ohmic contacts?

A1: High contact resistance (Rc) is a major challenge for 2D material-based devices[4]. It can arise from a Schottky barrier at the metal-semiconductor interface or from damage to the material during fabrication[4].

• Contact Metal Selection: The choice of metal is critical. For n-type SnSe<sub>2</sub>, metals with low work functions are preferred to minimize the Schottky barrier height. Titanium (Ti) has been shown to form contacts with a very low activation energy (as low as 5.5 meV), indicating the virtual absence of a significant Schottky barrier[1].

- Interface Engineering: Introducing an intermediate layer, such as graphene, between the contact metal and the SnSe<sub>2</sub> can improve performance. Graphene/Ti contacts on MoS<sub>2</sub> have shown significant improvements in on-resistance and contact resistance[3].

- Doping the Contact Region: Doping the semiconductor under the contact can reduce the depletion width and facilitate carrier tunneling, thereby lowering Rc[4].

- Fabrication Technique: The method of contact deposition can impact the interface. Metal evaporation can sometimes cause structural damage to atomically thin materials[4]. Alternative methods like via contacts or using pre-patterned contacts can be explored[6].

Click to download full resolution via product page

**Caption:** Logical relationship of resistance components in a 2D FET device.

#### **Category 3: Device Instability and Degradation**

#### Troubleshooting & Optimization

Q1: My SnSe<sub>2</sub> devices degrade quickly when exposed to ambient air. What causes this instability and how can it be prevented?

A1: Sn-based chalcogenides are known to be susceptible to rapid surface degradation in ambient atmospheres, primarily through oxidation[7].

- Oxidation: Exposure to oxygen and humidity leads to the formation of a tin oxide (SnO<sub>2</sub>) layer on the surface of the SnSe<sub>2</sub>[7]. While pristine SnSe<sub>2</sub> is relatively inert to water, the SnO<sub>2</sub>-SnSe<sub>2</sub> interface is highly reactive towards it, which can significantly alter device properties and impact stability[7].

- Passivation Strategies: Encapsulation is key to improving stability.

- In situ SnSe Passivation: Treating perovskite solar cells with a solution that forms a thin SnSe layer in situ has been shown to reduce surface traps and significantly protect the active layer from the environment. Devices retained 91% of their original efficiency after 10 days in ambient air without encapsulation[8][9].

- hBN Encapsulation: Fully encapsulating the 2D material channel (like SnSe) with hexagonal boron nitride (hBN) provides excellent protection from environmental factors, leading to more stable, hysteresis-free device characteristics[3].

- Defect Repair: Defects in the crystal lattice can act as sites for oxidation. An in situ selenization process can repair selenium vacancies, suppressing charge carrier recombination and reducing the likelihood of oxygen bonding to tin within the film, thereby enhancing environmental stability[5].

#### **Category 4: Fabrication and Synthesis**

Q1: What are reliable methods for synthesizing high-quality, thin SnSe<sub>2</sub> flakes for device fabrication?

A1: Several methods can be employed, with Chemical Vapor Deposition (CVD) being a prominent technique for scalable synthesis.

• Chemical Vapor Deposition (CVD): This method allows for the synthesis of single-crystalline ultrathin SnSe<sub>2</sub> nanoflakes.

- Precursors: Common precursors include high-purity selenium (Se) powder and a tin source like tin(II) selenide (SnSe) powder[10]. Using SnSe as the tin source is advantageous due to its suitable melting point, which ensures a slow evaporation rate during growth[10].

- Growth Parameters: The synthesis is typically carried out in a horizontal tube furnace. Key parameters to control include furnace temperature (e.g., 600 °C), pressure (e.g., 120 Torr), and carrier gas (e.g., Argon) flow rate[10]. Controlling these parameters is crucial for obtaining thin samples with high crystal quality[10][11].

- Mechanical Exfoliation: This method involves using tape to peel thin layers from a bulk single crystal. While it can produce very high-quality flakes, it is not as scalable as CVD[1].

Q2: Can the phase of tin selenide (SnSe vs. SnSe2) be controlled during synthesis?

A2: Yes, the phase can be controlled, primarily by temperature. Using a thermal evaporation method, the substrate temperature plays a critical role. A lower substrate temperature (e.g., ~210 °C) is beneficial for the growth of SnSe<sub>2</sub>, while a higher substrate temperature (e.g., ~380 °C) favors the growth of SnSe[11].

#### **Quantitative Data Summary**

Table 1: Performance Metrics of SnSe/SnSe<sub>2</sub>-Based Devices

| Device<br>Type/Structure                       | Key Parameter                     | Value                                                | Conditions                             | Reference |

|------------------------------------------------|-----------------------------------|------------------------------------------------------|----------------------------------------|-----------|

| SnSe <sub>2</sub> FET<br>(Substrate-<br>gated) | Drive Current                     | 160 μΑ/μm                                            | Vds = 2 V, T =<br>300 K                | [1]       |

| SnSe <sub>2</sub> FET<br>(Substrate-<br>gated) | Field-Effect<br>Mobility          | 8.6 cm²/Vs                                           | T = 300 K                              | [1]       |

| SnSe <sub>2</sub> FET<br>(Substrate-<br>gated) | Field-Effect<br>Mobility          | 28 cm²/Vs                                            | T = 77 K                               | [1]       |

| SnSe <sub>2</sub> FET<br>(Substrate-<br>gated) | Contact<br>Activation<br>Energy   | 5.5 meV                                              | Ti contacts                            | [1]       |

| SnSe <sub>2</sub> HetJ-<br>TFET<br>(Simulated) | On-State Current<br>(ION)         | 735 μA/μm                                            | VDD = 0.5 V                            | [12]      |

| SnSe <sub>2</sub> HetJ-<br>TFET<br>(Simulated) | Subthreshold<br>Swing (SS)        | 37-38 mV/dec                                         | -                                      | [12]      |

| SnSe-passivated<br>Perovskite Solar<br>Cell    | Power Conversion Efficiency (PCE) | 15.06%                                               | -                                      | [8][9]    |

| SnSe-passivated<br>Perovskite Solar<br>Cell    | Stability                         | Retained 91% of PCE                                  | After 10 days in air (30-40% humidity) | [8][9]    |

| SnSe <sub>2</sub> Thermoelectric Thin Film     | Power Factor                      | 3.69 μW cm <sup>-1</sup><br>K <sup>-2</sup>          | T = 227 °C                             | [13]      |

| SnSe <sub>2</sub> Thermoelectric Thin Film     | Carrier Mobility                  | 9.34 cm <sup>2</sup> V <sup>-1</sup> s <sup>-1</sup> | Heat treated at 350 °C                 | [13]      |

# Experimental Protocols Protocol 1: CVD Synthesis of Ultrathin SnSe<sub>2</sub> Nanoflakes

This protocol is adapted from the CVD method described for synthesizing SnSe<sub>2</sub> on mica substrates[10].

- Precursor Preparation: Place high-purity Se powder in one quartz boat and SnSe powder in a separate quartz boat.

- Furnace Setup: Position the boats inside a horizontal one-zone tube furnace with a silica tube. The substrate (e.g., mica) is placed downstream in the desired temperature zone.

- Growth Process:

- Purge the tube with Argon (Ar) gas.

- Heat the furnace to the growth temperature (e.g., 600 °C) over a short period (e.g., 12 minutes) to minimize premature source reaction.

- Maintain a constant Ar flow (e.g., 30 sccm) as the carrier gas.

- Maintain the pressure inside the tube at a low level (e.g., 120 Torr) to promote the formation of ultrathin flakes.

- Cooling: After the growth period, cool the furnace naturally to room temperature.

- Characterization: Characterize the as-grown flakes using optical microscopy, AFM, Raman spectroscopy, and XPS to confirm thickness, quality, and composition[10].

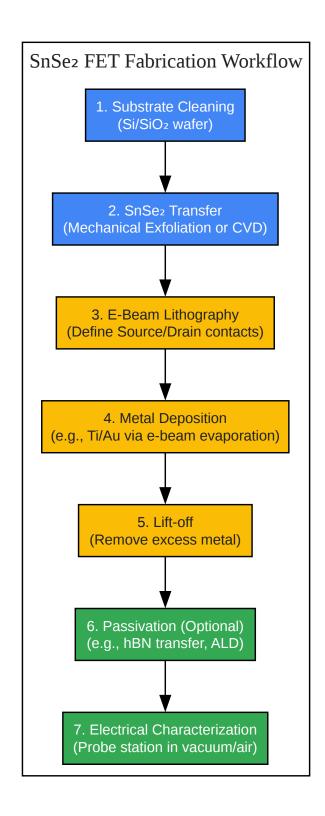

#### Protocol 2: Fabrication of a Back-Gated SnSe<sub>2</sub> FET

This is a general workflow for fabricating a simple FET device.

Click to download full resolution via product page

Caption: A typical experimental workflow for fabricating a back-gated SnSe<sub>2</sub> FET.

- Substrate: Start with a heavily doped silicon wafer with a thermally grown SiO<sub>2</sub> layer (e.g., 300 nm), which will serve as the back gate and gate dielectric, respectively.

- Material Transfer: Transfer a thin SnSe<sub>2</sub> flake onto the SiO<sub>2</sub>/Si substrate via mechanical exfoliation or direct CVD growth.

- Contact Patterning: Use standard electron-beam lithography or photolithography to define the source and drain contact patterns on top of the flake.

- Metal Deposition: Deposit contact metals using electron-beam evaporation. A common stack is Ti/Au (e.g., 10 nm Ti for adhesion and low barrier, followed by 50 nm Au to prevent oxidation)[1].

- Lift-off: Perform a lift-off process in a suitable solvent (e.g., acetone) to remove the resist and unwanted metal, leaving only the desired source and drain electrodes.

- Annealing (Optional): Anneal the device in a vacuum or inert atmosphere to improve contact quality.

- Characterization: Perform electrical measurements using a semiconductor parameter analyzer connected to a probe station. For stability and performance assessment, measurements should ideally be conducted both in air and under vacuum[1].

#### **Need Custom Synthesis?**

BenchChem offers custom synthesis for rare earth carbides and specific isotopiclabeling.

Email: info@benchchem.com or Request Quote Online.

#### References

- 1. pubs.aip.org [pubs.aip.org]

- 2. arxiv.org [arxiv.org]

- 3. researchgate.net [researchgate.net]

- 4. poplab.stanford.edu [poplab.stanford.edu]

- 5. Defect repair of tin selenide photocathode via in situ selenization: enhanced photoelectrochemical performance and environmental stability - Journal of Materials Chemistry A (RSC Publishing) [pubs.rsc.org]

- 6. researchgate.net [researchgate.net]

- 7. pubs.acs.org [pubs.acs.org]

- 8. research.rug.nl [research.rug.nl]

- 9. In situ SnSe deposition as passivation for scalable and stable quasi-2D lead—tin perovskite solar cells - Energy & Environmental Science (RSC Publishing) [pubs.rsc.org]

- 10. mdpi.com [mdpi.com]

- 11. researchgate.net [researchgate.net]

- 12. pubs.acs.org [pubs.acs.org]

- 13. pubs.aip.org [pubs.aip.org]

- To cite this document: BenchChem. [Stannic Selenide (SnSe<sub>2</sub>) Device Integration: Technical Support Center]. BenchChem, [2025]. [Online PDF]. Available at: [https://www.benchchem.com/product/b1590759#overcoming-challenges-in-stannic-selenide-device-integration]

#### **Disclaimer & Data Validity:**

The information provided in this document is for Research Use Only (RUO) and is strictly not intended for diagnostic or therapeutic procedures. While BenchChem strives to provide accurate protocols, we make no warranties, express or implied, regarding the fitness of this product for every specific experimental setup.

**Technical Support:**The protocols provided are for reference purposes. Unsure if this reagent suits your experiment? [Contact our Ph.D. Support Team for a compatibility check]

Need Industrial/Bulk Grade? Request Custom Synthesis Quote

### BenchChem

Our mission is to be the trusted global source of essential and advanced chemicals, empowering scientists and researchers to drive progress in science and industry. Contact

Address: 3281 E Guasti Rd

Ontario, CA 91761, United States

Phone: (601) 213-4426

Email: info@benchchem.com