# Reducing stacking faults during 3C-SiC heteroepitaxy

Author: BenchChem Technical Support Team. Date: December 2025

| Compound of Interest |                 |           |

|----------------------|-----------------|-----------|

| Compound Name:       | Silicon carbide |           |

| Cat. No.:            | B1214593        | Get Quote |

## **Technical Support Center: 3C-SiC Heteroepitaxy**

This technical support center provides troubleshooting guidance and frequently asked questions (FAQs) to assist researchers in reducing stacking faults during the heteroepitaxy of 3C-SiC on silicon substrates.

## **Troubleshooting Guide**

This guide addresses common issues encountered during 3C-SiC growth that lead to a high density of stacking faults.

Issue 1: High Density of Stacking Faults Originating at the 3C-SiC/Si Interface

- Question: My 3C-SiC film shows a very high density of stacking faults, particularly near the interface with the silicon substrate. What are the primary causes and how can I mitigate this?

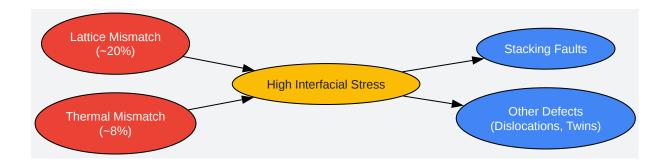

- Answer: A high density of stacking faults at the interface is primarily due to the large lattice mismatch (~20%) and the difference in thermal expansion coefficients (~8%) between 3C-SiC and silicon.[1][2] These mismatches induce significant stress, which is relieved through the formation of defects, including stacking faults (SFs), misfit dislocations, and micro-twins. [1][2][3][4]

Troubleshooting Steps:

#### Troubleshooting & Optimization

- Optimize the Carbonization Step: The initial carbonization of the Si surface is crucial for creating a template for 3C-SiC growth.[1] An improperly controlled carbonization process can lead to a rough surface and a high density of nucleation sites for defects. Ensure precise control over the temperature ramp, precursor flow rates (e.g., a carbon-rich precursor like propane), and duration of this step.[1][5] The goal is to form a thin, continuous SiC layer that effectively accommodates the misfit strain.[1]

- Employ a Buffer Layer: The use of a buffer layer can help to bridge the lattice mismatch between Si and 3C-SiC. While the initial carbonization layer acts as a buffer, more complex buffer structures can be employed. The morphology of this initial layer significantly influences the generation and propagation of stacking faults.[6]

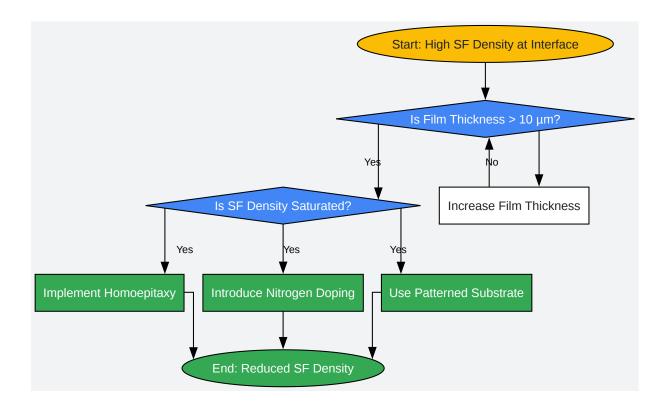

- Utilize Patterned or Compliant Substrates: Growing 3C-SiC on patterned Si substrates, such as those with undulations, pyramidal shapes, or pillars, has been shown to reduce the density of stacking faults.[1][7] These structures can guide the propagation of defects and enhance their annihilation. Similarly, compliant substrates are designed to absorb the strain from the lattice mismatch, thereby reducing defect formation in the epitaxial layer.[4]

- Consider an AlN Interlayer: The use of an Aluminum Nitride (AlN) buffer layer can be beneficial due to its better lattice match with 3C-SiC compared to silicon.[8] This can lead to a lower defect density in the subsequently grown 3C-SiC film, especially for thinner layers.[8]

Issue 2: Stacking Fault Density Does Not Decrease Significantly with Increasing Film Thickness

- Question: I am growing thick 3C-SiC layers, but the stacking fault density seems to saturate

at a high level instead of decreasing. Why is this happening and what can be done?

- Answer: While stacking fault density generally decreases as the film thickness increases due

to annihilation events where SFs on different {111} planes intersect and terminate each

other, this process can become less efficient.[3][7] At a certain point, the remaining SFs may

propagate parallel to each other without intersecting, leading to a saturation of the defect

density, often around 10<sup>4</sup> cm<sup>-1</sup>.[3]

Troubleshooting Steps:

### Troubleshooting & Optimization

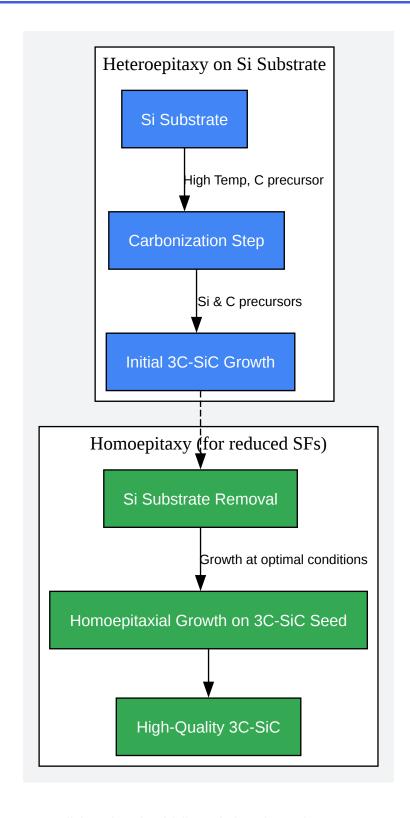

- Transition to Homoepitaxial Growth: A highly effective strategy is to remove the original silicon substrate after an initial heteroepitaxial growth and then continue with a homoepitaxial growth on the exposed 3C-SiC surface.[3] This eliminates the ongoing stress from the Si substrate and allows for growth conditions optimized for high-quality 3C-SiC, leading to a significant reduction in SF density.[3]

- Optimize Growth Rate: In homoepitaxial growth, the growth rate plays a crucial role.

Slower growth rates have been shown to favor the reduction of stacking faults.[3] This is because a lower growth rate provides more time for adatoms to find their correct lattice sites, promoting a more ordered crystal structure.[3]

- Introduce Intentional Doping (Nitrogen): The introduction of nitrogen as an n-type dopant during CVD growth has been demonstrated to be remarkably effective in inhibiting the propagation and promoting the closure of stacking faults.[9][10][11] Increasing the nitrogen concentration can lead to a substantial decrease in SF density.[10]

Issue 3: Inconsistent Crystal Quality and High Defect Density Across the Wafer

- Question: The quality of my 3C-SiC films is not uniform, with some areas showing a much higher defect density than others. What could be causing this inconsistency?

- Answer: Inconsistent crystal quality can stem from several factors related to the growth conditions and the substrate preparation.

#### Troubleshooting Steps:

- Ensure Uniform Substrate Temperature: Non-uniform temperature distribution across the substrate is a common cause of inconsistent film quality. Calibrate your heating system to ensure a uniform temperature profile. The growth temperature is a critical parameter that influences surface morphology and defect formation.[12]

- Optimize Gas Flow Dynamics: The flow of precursor gases (e.g., silane and a carbon source) and the carrier gas (e.g., hydrogen) must be uniform across the substrate surface.

[2] In a horizontal hot-wall CVD reactor, gas flow dynamics can be complex. Adjusting the reactor pressure (e.g., low pressure vs. atmospheric pressure) can alter the gas flow and boundary layer thickness, impacting growth uniformity and quality.

- Control the C/Si Ratio: The ratio of carbon to silicon precursors is a critical parameter that

affects the crystal quality. An optimal C/Si ratio needs to be determined for your specific

reactor and growth conditions.[10][13] Variations in this ratio across the wafer can lead to

inconsistencies in the grown film.

- Substrate Preparation and Cleanliness: Ensure that the silicon substrate is meticulously cleaned to remove any contaminants before loading it into the reactor. The quality of the substrate surface is paramount for high-quality epitaxial growth.[12]

# Frequently Asked Questions (FAQs)

Q1: What is the primary cause of stacking faults in 3C-SiC grown on silicon?

A1: The primary cause is the significant mismatch in lattice parameters (~20%) and thermal expansion coefficients (~8%) between 3C-SiC and the silicon substrate.[1][2] This mismatch induces stress that leads to the formation of various crystalline defects, including a high density of stacking faults, to relieve the strain.[1][2][3][4]

Q2: How does increasing the thickness of the 3C-SiC film help in reducing stacking faults?

A2: As the 3C-SiC film grows thicker, stacking faults that lie on different {111} crystallographic planes can intersect with each other.[3] This intersection can lead to their mutual annihilation, thus reducing the overall density of SFs in the upper regions of the film.[3] However, this self-annihilation mechanism becomes less effective as the SF density decreases, often leading to a saturation level.[3]

Q3: What is homoepitaxial growth and why is it effective in reducing stacking faults?

A3: Homoepitaxial growth refers to the deposition of a crystalline film on a substrate of the same material. In the context of 3C-SiC, this typically involves first growing a 3C-SiC layer on a silicon substrate, then removing the silicon substrate (e.g., by etching or melting), and subsequently using the freestanding 3C-SiC layer as a seed for further growth.[3][9] This method is highly effective because it eliminates the stress caused by the lattice and thermal mismatch with the original silicon substrate, which is the root cause of the high initial defect density.[11]

Q4: Can post-growth annealing reduce stacking faults?

A4: While the provided search results focus more on defect reduction during growth, post-deposition annealing (PDA) has been shown to be effective in passivating the electrical activity of stacking faults at the SiO<sub>2</sub>/3C-SiC interface in MOS capacitors.[14] Annealing at temperatures around 450°C in nitrogen or forming gas can reduce interface and oxide traps. [14] There is also evidence from studies on 4H-SiC that thermal annealing can induce the shrinkage of stacking faults.[15]

Q5: What is the role of nitrogen doping in reducing stacking faults?

A5: Intentionally introducing nitrogen during the CVD growth of 3C-SiC has a significant impact on reducing stacking fault density.[9][10][11] The presence of nitrogen in the crystal lattice is believed to increase the formation energy of stacking faults, thereby suppressing their propagation and promoting their closure.[9][10] Higher nitrogen concentrations have been correlated with a lower density of stacking faults.[10]

## **Quantitative Data Summary**

Table 1: Effect of Homoepitaxial Growth Rate on Stacking Fault Density

| Growth Rate (μm/h) | Stacking Fault Linear<br>Density (cm <sup>-1</sup> ) | Growth Temperature (°C) |

|--------------------|------------------------------------------------------|-------------------------|

| 30                 | Lower                                                | 1650                    |

| 60                 | Intermediate                                         | 1650                    |

| 90                 | Higher                                               | 1650                    |

Note: A qualitative trend is described where slower growth rates favor the reduction of stacking faults.[3]

Table 2: Effect of Nitrogen Doping on Stacking Fault Density in Free-Standing 3C-SiC

| Nitrogen Concentration (atoms/cm³) | SF Density at 10 $\mu$ m from interface (cm <sup>-1</sup> ) | SF Density at 70 µm from interface (cm <sup>-1</sup> ) |

|------------------------------------|-------------------------------------------------------------|--------------------------------------------------------|

| Intrinsic (~2 x 10 <sup>16</sup> ) | 1.2 x 10 <sup>4</sup>                                       | 2.1 x 10 <sup>3</sup>                                  |

| High (~5.8 x 10 <sup>19</sup> )    | 1.6 x 10 <sup>3</sup>                                       | 2.4 x 10 <sup>2</sup>                                  |

Data extracted from a study on the impact of nitrogen doping on SF density as a function of film thickness.[10]

## **Experimental Protocols**

Protocol 1: Chemical Vapor Deposition (CVD) of 3C-SiC on Si (100) with Nitrogen Doping

This protocol is based on a method described for investigating the effect of nitrogen on stacking fault reduction.[9][10]

• Substrate: Si (100) with a 4° off-axis orientation.

Reactor: Horizontal hot-wall CVD reactor.

Precursors:

Silicon source: Trichlorosilane (TCS, SiHCl₃)

Carbon source: Ethylene (C<sub>2</sub>H<sub>4</sub>)

Carrier gas: Hydrogen (H<sub>2</sub>)

Dopant gas: Nitrogen (N<sub>2</sub>)

Growth Parameters:

Pressure: 100 mbar

Temperature: 1370 °C

C/Si Ratio: Varied from 1.12 to 0.7

- Nitrogen Flow: 0 sccm (intrinsic), 300 sccm, 800 sccm, or 1600 sccm.

- Procedure: a. Load the Si (100) 4° off-axis substrate into the CVD reactor. b. Heat the substrate to the growth temperature of 1370 °C under a hydrogen atmosphere. c. Introduce the TCS and C<sub>2</sub>H<sub>4</sub> precursors along with the desired nitrogen flow to initiate the heteroepitaxial growth of 3C-SiC. d. Continue the growth to achieve the desired film thickness (e.g., 75 μm). e. For producing a free-standing 3C-SiC wafer for subsequent homoepitaxy, the silicon substrate can be melted inside the reactor at a higher temperature (e.g., 1650 °C) after the initial growth.[9]

Protocol 2: Characterization of Stacking Faults by Molten KOH Etching

This is a common method to reveal and quantify stacking faults for analysis by optical microscopy.[3]

- Etchant: Potassium Hydroxide (KOH).

- Procedure: a. Heat the KOH in a suitable crucible to a molten state. b. Immerse the 3C-SiC sample in the molten KOH for a specific duration. The etching time and temperature will determine the size of the etch pits. c. Carefully remove the sample from the molten KOH and allow it to cool down. d. Clean the sample to remove any residual KOH. e. Observe the etched surface using an optical microscope. Stacking faults will be delineated as linear etch pits or grooves on the surface. f. The linear density of stacking faults (number of SFs per unit length) can be determined by counting the etch features.

#### **Visualizations**

Click to download full resolution via product page

Caption: Workflow for reducing stacking faults via homoepitaxy.

Click to download full resolution via product page

Caption: Root causes of stacking fault formation in 3C-SiC on Si.

Click to download full resolution via product page

Caption: Troubleshooting logic for reducing stacking fault density.

#### **Need Custom Synthesis?**

BenchChem offers custom synthesis for rare earth carbides and specific isotopiclabeling.

Email: info@benchchem.com or Request Quote Online.

#### References

- 1. boa.unimib.it [boa.unimib.it]

- 2. mtikorea.co.kr [mtikorea.co.kr]

- 3. st.com [st.com]

- 4. st.com [st.com]

- 5. researchgate.net [researchgate.net]

- 6. Structural defects in (100) 3C-SiC heteroepitaxy: Influence of the buffer layer morphology on generation and propagation of stacking faults and microtwins | IMM Container [imm.cnr.it]

- 7. researchgate.net [researchgate.net]

- 8. CVD Elaboration of 3C-SiC on AlN/Si Heterostructures: Structural Trends and Evolution during Growth [mdpi.com]

- 9. pubs.acs.org [pubs.acs.org]

- 10. Impact of Nitrogen on the Selective Closure of Stacking Faults in 3C-SiC PMC [pmc.ncbi.nlm.nih.gov]

- 11. iris.unict.it [iris.unict.it]

- 12. mediatum.ub.tum.de [mediatum.ub.tum.de]

- 13. mdpi.com [mdpi.com]

- 14. pubs.aip.org [pubs.aip.org]

- 15. researchgate.net [researchgate.net]

- To cite this document: BenchChem. [Reducing stacking faults during 3C-SiC heteroepitaxy].

BenchChem, [2025]. [Online PDF]. Available at: [https://www.benchchem.com/product/b1214593#reducing-stacking-faults-during-3c-sic-heteroepitaxy]

#### **Disclaimer & Data Validity:**

The information provided in this document is for Research Use Only (RUO) and is strictly not intended for diagnostic or therapeutic procedures. While BenchChem strives to provide accurate protocols, we make no warranties, express or implied, regarding the fitness of this product for every specific experimental setup.

**Technical Support:**The protocols provided are for reference purposes. Unsure if this reagent suits your experiment? [Contact our Ph.D. Support Team for a compatibility check]

Need Industrial/Bulk Grade? Request Custom Synthesis Quote

# BenchChem

Our mission is to be the trusted global source of essential and advanced chemicals, empowering scientists and researchers to drive progress in science and industry.

#### Contact

Address: 3281 E Guasti Rd

Ontario, CA 91761, United States

Phone: (601) 213-4426

Email: info@benchchem.com