# Reducing leakage current in NbO2-based memristors

Author: BenchChem Technical Support Team. Date: December 2025

| Compound of Interest |                   |           |

|----------------------|-------------------|-----------|

| Compound Name:       | Niobium(IV) oxide |           |

| Cat. No.:            | B088533           | Get Quote |

# Technical Support Center: NbO<sub>2</sub>-Based Memristors

This technical support center provides troubleshooting guidance and frequently asked questions for researchers and scientists working with Niobium Dioxide (NbO<sub>2</sub>)-based memristors. The focus is on understanding and mitigating leakage current during experimental work.

## Frequently Asked Questions (FAQs)

Q1: What is leakage current in the context of NbO<sub>2</sub> memristors and why is it problematic?

A1: Leakage current, also known as OFF-state current, is the electrical current that flows through the memristor when it is in its high-resistance state (HRS or OFF-state) below the threshold voltage. In an ideal device, this current would be zero. It is problematic because high leakage current reduces the ON/OFF resistance ratio (selectivity), which is a critical performance metric. This can lead to read disturbances in memory arrays, increased power consumption, and a blurring of the sharp insulator-to-metal transition (IMT) that is characteristic of NbO<sub>2</sub> devices.[1][2][3][4]

Q2: What are the primary causes of high leakage current in NbO2-based memristors?

A2: High leakage current in NbO<sub>2</sub> memristors can typically be attributed to several factors:

#### Troubleshooting & Optimization

- Amorphous Matrix: The presence of an amorphous, sub-stoichiometric niobium oxide (NbO<sub>x</sub>)

matrix surrounding the desired crystalline NbO<sub>2</sub> filament can provide a parallel conduction

path for current.[1][5]

- Interface Defects: Insufficient Schottky barrier height or defects at the interface between the electrode and the NbO<sub>x</sub> layer can lead to unwanted current flow.[6]

- Filament Composition: The formation of non-volatile Nb<sub>2</sub>O<sub>5</sub> within the conductive filament during the electroforming process can contribute to leakage pathways.[5][6][7][8][9]

- Joule Heating: At lower voltages, before the main threshold switch, Joule heating can cause a gradual temperature increase, which in turn reduces the device's resistance and increases current flow.[9][10]

Q3: How does operating at cryogenic temperatures affect leakage current?

A3: Operating NbO<sub>2</sub> memristors at cryogenic temperatures (e.g., below 200 K) is an effective method to suppress leakage current.[1][5][7][8] The lower temperature reduces the conductivity of the semiconducting amorphous matrix surrounding the filament, effectively "freezing out" the leakage paths.[1][5] This forces the current to flow primarily through the crystalline NbO<sub>2</sub> filament, making the characteristic sharp insulator-to-metal transition more apparent and significantly increasing the device's resistance in the OFF-state.[1][5]

## **Troubleshooting Guide**

Q4: My as-fabricated device exhibits a very high OFF-state current at room temperature. What are the initial troubleshooting steps?

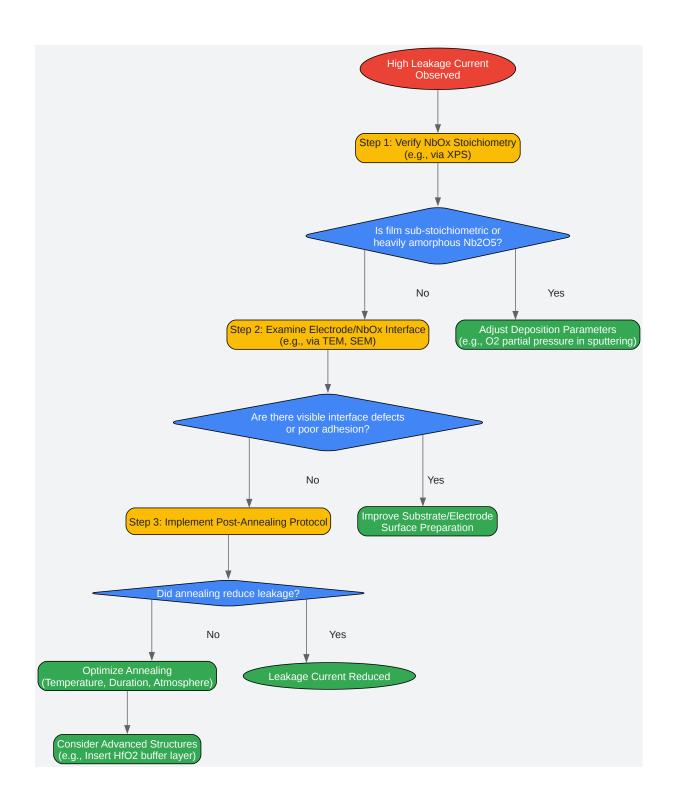

A4: High initial leakage current often points to issues in the material deposition or device fabrication. A logical troubleshooting workflow can help isolate the cause.

Click to download full resolution via product page

Caption: A troubleshooting workflow for high leakage current.

Q5: I've tried post-annealing, but the leakage current is still too high. What other fabrication strategies can I employ?

A5: If annealing alone is insufficient, consider interface engineering by inserting a thin dielectric layer between the NbO<sub>2</sub> and one of the electrodes. Materials like Hafnium Dioxide (HfO<sub>2</sub>) or a stoichiometric Nb<sub>2</sub>O<sub>5</sub> layer can be effective. This bilayer approach can address leakage by improving the interface quality and introducing a thermal confinement effect.[4][6] For instance, inserting a 10 nm HfO<sub>2</sub> layer has been shown to decrease leakage current to approximately 10 μA and increase selectivity by an order of magnitude.[4]

## **Experimental Protocols**

Protocol 1: Fabrication of a Low-Leakage NbO2/HfO2 Bilayer Memristor

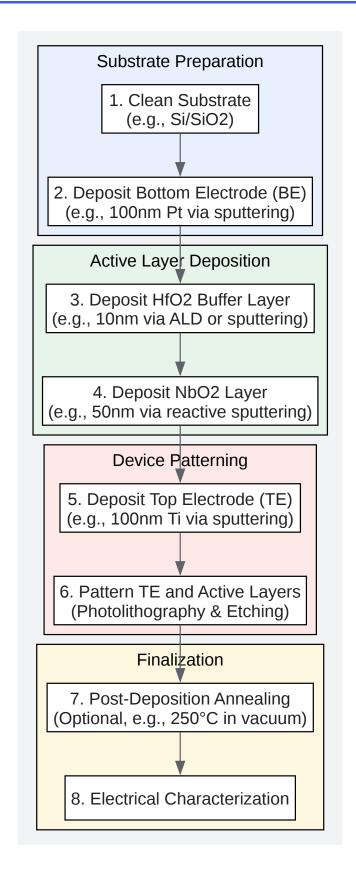

This protocol describes a typical process for fabricating a bilayer device structure to reduce leakage current.

Click to download full resolution via product page

Caption: Experimental workflow for bilayer memristor fabrication.

#### Methodology:

- Substrate and Bottom Electrode: Start with a cleaned Si/SiO<sub>2</sub> substrate. Deposit the bottom electrode, for example, 100 nm of Platinum (Pt), using a technique like magnetron sputtering.

- Buffer Layer Deposition: Insert a thin buffer layer to improve the interface and suppress leakage. Deposit a 10 nm layer of HfO<sub>2</sub> using Atomic Layer Deposition (ALD) for high uniformity or sputtering.[4]

- NbO<sub>2</sub> Deposition: Deposit the active NbO<sub>2</sub> layer. This can be done via reactive sputtering from a Nb target in an Ar/O<sub>2</sub> atmosphere. The O<sub>2</sub> gas fraction is critical and must be optimized; values around 7-12% have been reported.[9]

- Top Electrode and Patterning: Deposit the top electrode, such as Titanium (Ti).

Subsequently, use standard photolithography and etching processes to define the cross-bar device structures.

- Annealing (Optional): A post-deposition anneal, for instance at 250°C in a vacuum, may be performed to improve the crystallinity of the NbO<sub>2</sub> layer and reduce defects.[9]

- Characterization: Perform current-voltage (I-V) sweeps to characterize the device's switching behavior and measure the leakage current in the high-resistance state.

#### **Quantitative Data Summary**

The following table summarizes the impact of different techniques on NbO<sub>2</sub> memristor performance, with a focus on leakage current and selectivity.

| Technique                  | Device<br>Structure               | Key<br>Parameter<br>Change                           | Leakage<br>Current (at<br>1/2 Vth)                         | Selectivity<br>(ON/OFF<br>Ratio) | Reference |

|----------------------------|-----------------------------------|------------------------------------------------------|------------------------------------------------------------|----------------------------------|-----------|

| **Baseline<br>(No HfO2) ** | Ti/NbO <sub>2</sub> /Pt           | N/A                                                  | High (not specified)                                       | ~10                              | [4]       |

| Buffer Layer<br>Insertion  | Ti/NbO2/HfO2<br>(10 nm)/Pt        | 10 nm HfO <sub>2</sub><br>layer added                | ~10 µA                                                     | ~100                             | [4]       |

| Cryogenic<br>Operation     | Au/Ru/NbO×/<br>Pt                 | Temperature<br>decreased<br>from 300 K to<br>< 200 K | Suppressed<br>to near zero                                 | Increases to<br>10-50            | [1][5]    |

| Post-<br>Annealing         | Nb(O)/NbO <sub>×</sub> /<br>Nb(O) | Annealed at<br>250°C in<br>vacuum                    | Not specified,<br>but enables<br>forming-free<br>switching | Not specified                    | [9]       |

## **Mechanism Visualization**

The diagram below illustrates conceptually how an inserted buffer layer helps reduce leakage current.

Click to download full resolution via product page

Caption: A buffer layer blocks parallel leakage paths.

#### **Need Custom Synthesis?**

BenchChem offers custom synthesis for rare earth carbides and specific isotopiclabeling.

Email: info@benchchem.com or Request Quote Online.

#### References

- 1. pubs.aip.org [pubs.aip.org]

- 2. users.cs.utah.edu [users.cs.utah.edu]

- 3. Modelling, fabrication, and characterization of memristor for mitigating the sneak path current in a nano-crossbar memory array Nottingham ePrints [eprints.nottingham.ac.uk]

- 4. pubs.aip.org [pubs.aip.org]

- 5. Enhancement in neuromorphic NbO2 memristive device switching at cryogenic temperatures [arxiv.org]

- 6. researchgate.net [researchgate.net]

- 7. [2408.06180] Enhancement in neuromorphic NbO2 memristive device switching at cryogenic temperatures [arxiv.org]

- 8. researchgate.net [researchgate.net]

- 9. researchgate.net [researchgate.net]

- 10. Physical model of threshold switching in NbO2 based memristors RSC Advances (RSC Publishing) [pubs.rsc.org]

- To cite this document: BenchChem. [Reducing leakage current in NbO2-based memristors].

BenchChem, [2025]. [Online PDF]. Available at: [https://www.benchchem.com/product/b088533#reducing-leakage-current-in-nbo2-based-memristors]

#### **Disclaimer & Data Validity:**

The information provided in this document is for Research Use Only (RUO) and is strictly not intended for diagnostic or therapeutic procedures. While BenchChem strives to provide accurate protocols, we make no warranties, express or implied, regarding the fitness of this product for every specific experimental setup.

**Technical Support:** The protocols provided are for reference purposes. Unsure if this reagent suits your experiment? [Contact our Ph.D. Support Team for a compatibility check]

Need Industrial/Bulk Grade? Request Custom Synthesis Quote

## BenchChem

Our mission is to be the trusted global source of essential and advanced chemicals, empowering scientists and researchers to drive progress in science and industry. Contact

Address: 3281 E Guasti Rd

Ontario, CA 91761, United States

Phone: (601) 213-4426

Email: info@benchchem.com