# Optimizing charge mobility in DHDT-based OFETs

Author: BenchChem Technical Support Team. Date: December 2025

Compound of Interest

2,3-Dihydrothieno[3,4-b]

[1,4]dithiine

Cat. No.:

B180702

Get Quote

# **Technical Support Center: DHDT-Based OFETs**

Welcome to the technical support center for optimizing charge mobility in DHDT (Diketopyrrolopyrol-thieno[3,2-b]thiophene) based Organic Field-Effect Transistors (OFETs). This resource provides troubleshooting guidance and answers to frequently asked questions to assist researchers in overcoming common experimental challenges.

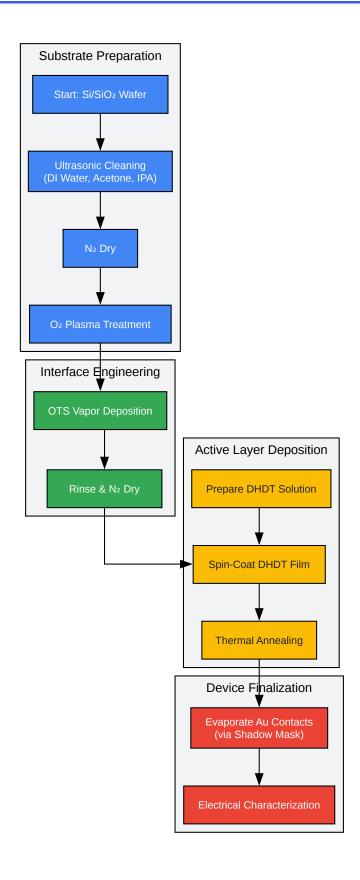

# **Troubleshooting Guide**

This section addresses specific issues you may encounter during the fabrication and characterization of DHDT-based OFETs.

Q1: My measured charge carrier mobility is significantly lower than reported values. What are the most likely causes?

A1: Low charge carrier mobility is a common issue that can stem from several factors throughout the fabrication process. The primary areas to investigate are the semiconductor film morphology, the quality of the dielectric interface, and the charge injection efficiency at the contacts.

Poor Film Morphology: The ordering and crystallinity of the DHDT polymer film are critical for efficient charge transport.[1] In solution-processed films, factors like solvent choice, deposition technique, and annealing conditions heavily influence the final morphology.[1][2]

### Troubleshooting & Optimization

- Solvent Issues: An inappropriate solvent can lead to aggregation in solution or the formation of a non-uniform, amorphous film with many grain boundaries that hinder charge transport.

- Sub-optimal Annealing: Thermal annealing is often required to improve polymer chain packing and crystallinity.[2] Both the temperature and duration are critical; insufficient annealing may not provide enough energy for molecular rearrangement, while excessive temperature can damage the film.

- Dielectric Interface Traps: Charge transport in an OFET occurs within the first few

nanometers of the semiconductor layer at the dielectric interface.[3] A high density of trap

states at this interface, often caused by hydroxyl groups (-OH) on an untreated SiO<sub>2</sub> surface,

can immobilize charge carriers and drastically reduce mobility.[3][4]

- High Contact Resistance: A large energy barrier between the source/drain electrodes and the DHDT semiconductor layer can impede charge injection, leading to an underestimation of the intrinsic material mobility.[5][6] This is known as a non-ohmic contact.[7]

Q2: I'm observing a very high OFF-current in my device, leading to a low ON/OFF ratio. What should I investigate?

A2: A high OFF-current suggests significant charge leakage. The most common culprits are the gate dielectric and potential impurities.

- Gate Dielectric Leakage: The insulating layer may not be sufficient. This can happen if the

dielectric layer is too thin (e.g., <100 nm for many solution-processed dielectrics can be

prone to pinholes) or has defects.[8] You should verify the thickness and quality of your

dielectric layer, perhaps by fabricating a simple capacitor structure (Metal-Insulator-Metal) to

measure its leakage current density independently.</li>

- Semiconductor Impurities: Residual solvents, moisture, or other contaminants in the DHDT film can act as dopants, increasing the background carrier concentration and leading to a high OFF-current. Ensure your materials are pure and that fabrication is performed in a controlled environment (e.g., a nitrogen-filled glovebox).

- Surface Contamination: Contamination on the substrate before deposition can create leakage pathways. Ensure a rigorous substrate cleaning protocol is followed.

### Troubleshooting & Optimization

Q3: The output characteristics of my OFET are not showing clear saturation. What does this indicate?

A3: A lack of current saturation is often a sign of high contact resistance.[5] In an ideal transistor, the current saturates when the conductive channel is "pinched off" near the drain electrode. However, if charge injection at the drain is inefficient (high contact resistance), the device may not exhibit ideal behavior. This effect can lead to an overestimation of mobility when calculated from the saturation regime.[7]

### • Actionable Steps:

- Evaluate Electrode Material: Ensure the work function of your source/drain metal (e.g., Gold) is well-matched with the HOMO level of the DHDT polymer for efficient hole injection.

- Contact Surface Treatment: Consider treating the contacts with a self-assembled monolayer (SAM) to reduce the injection barrier.

- Use the Transmission Line Method (TLM): Fabricate devices with varying channel lengths to explicitly measure and quantify the contact resistance.

Q4: Device-to-device performance is highly inconsistent across the same substrate. How can I improve reproducibility?

A4: Poor reproducibility points to non-uniformity in one or more of the fabrication steps.

- Spin-Coating: Ensure your spin-coater parameters (speed, acceleration, time) are optimized

to produce a uniform semiconductor film across the entire substrate. The solution viscosity

and volume are also critical.

- Annealing: Check for temperature gradients across the hotplate. A non-uniform temperature will lead to variations in film crystallinity and, consequently, mobility.

- Deposition Environment: Perform depositions in a clean, controlled atmosphere to avoid random contamination. Any dust or particles can disrupt film formation or create short circuits.

• Substrate Cleaning: Inconsistent cleaning can leave patches of residue, affecting the dielectric surface energy and leading to non-uniform film growth.

## Frequently Asked Questions (FAQs)

Q1: What is a typical range for charge carrier mobility in high-performance DHDT-based OFETs?

A1: DHDT-based polymers are known for their high performance. Hole mobilities for copolymers of thieno[3,2-b]thiophene and diketopyrrolopyrrole have been reported to reach values as high as 1.95 cm²/Vs.[10][11] Achieving such high values requires careful optimization of the molecular structure, film morphology, and device architecture.[12]

Q2: How does thermal annealing temperature affect mobility?

A2: Thermal annealing provides the energy needed for polymer chains to rearrange into more ordered, crystalline domains, which is generally favorable for charge transport.[2] As annealing temperature increases towards the material's glass transition temperature, mobility typically increases. However, exceeding an optimal temperature can lead to film dewetting or degradation, causing a sharp drop in performance.[13] The ideal temperature must be determined empirically for each specific polymer and substrate combination.

Q3: Which solvents are recommended for dissolving DHDT polymers?

A3: High-boiling-point aromatic solvents are often used for high-performance donor-acceptor polymers to allow for sufficient drying time, which promotes better molecular ordering during film formation.[14] Solvents like chlorobenzene, dichlorobenzene (DCB), or 1,2,4-trichlorobenzene (TCB) are common choices. The choice of solvent significantly impacts the polymer's solubility and the resulting thin-film morphology.[15]

Q4: Why is surface treatment of the gate dielectric important?

A4: The dielectric surface plays a critical role in OFET performance.[3][16] Treating a standard SiO<sub>2</sub> surface with a self-assembled monolayer (SAM), such as octadecyltrichlorosilane (OTS), serves two main purposes:

- Passivation: It neutralizes charge-trapping sites (like -OH groups) on the oxide surface,

reducing carrier scattering and improving mobility.[3][4]

- Morphology Control: It modifies the surface energy, promoting the growth of a more ordered,

crystalline semiconductor film, which is essential for high mobility.[4][17]

Q5: What is contact resistance and how does it affect my measurements?

A5: Contact resistance is the opposition to current flow at the interface between the metal electrode and the organic semiconductor.[7][18] It acts as a parasitic resistance in series with the channel resistance.[5] If the contact resistance is high, it can dominate the device's total resistance, especially in short-channel devices. This leads to a lower measured drain current and an artificially low calculated mobility.[9]

## **Quantitative Data Summary**

The following tables summarize the impact of various experimental parameters on the performance of DHDT-family polymer OFETs, based on literature data.

Table 1: Effect of Dielectric Surface Treatment on DPP-DTT OFET Performance

| Silylating<br>Agent                                                                                                          | Water Contact<br>Angle (°) | Average Hole<br>Mobility<br>(cm²/Vs) | ON/OFF Ratio          | Threshold<br>Voltage (Vth) |

|------------------------------------------------------------------------------------------------------------------------------|----------------------------|--------------------------------------|-----------------------|----------------------------|

| Untreated SiO <sub>2</sub>                                                                                                   | 25 ± 2                     | 0.11                                 | 3.8 x 10 <sup>5</sup> | -86.2                      |

| PTS (Phenyl)                                                                                                                 | 73 ± 1                     | 0.23                                 | 2.3 x 10 <sup>6</sup> | -60.3                      |

| OTS-8 (Octyl)                                                                                                                | 99 ± 2                     | 0.52                                 | 2.6 x 10 <sup>6</sup> | -40.5                      |

| OTS-18<br>(Octadecyl)                                                                                                        | 108 ± 1                    | 0.98                                 | 8.7 x 10 <sup>5</sup> | -28.2                      |

| (Data adapted from a study on DPP-DTT, a related high-mobility polymer, demonstrating the trend of surface modification.)[4] |                            |                                      |                       |                            |

Table 2: Effect of Annealing Temperature on OFET Performance

| Annealing<br>Temperature (°C) | Field-Effect<br>Mobility (µFE)<br>(cm²/Vs) | Threshold Voltage<br>(Vth) (V) | Subthreshold<br>Swing (SS) (V/dec) |

|-------------------------------|--------------------------------------------|--------------------------------|------------------------------------|

| No Annealing                  | ~0.018                                     | -23.4                          | N/A                                |

| 150                           | ~0.1 - 0.2                                 | Varies                         | Improves                           |

| 200                           | Up to 1.0+                                 | Varies                         | Improves                           |

| (This table provides          |                                            |                                |                                    |

( i nis table provides representative data trends for highperformance polymers like P3HT and DPPbased systems, as specific DHDT annealing series are highly dependent on the exact copolymer structure. Higher temperatures generally improve crystallinity and mobility up to an optimal point before degradation.)[2][19]

20

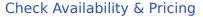

# Experimental Protocols Standard Fabrication Protocol for a BGTC DHDT-based OFET

This protocol outlines a typical procedure for fabricating a bottom-gate, top-contact (BGTC) OFET on a silicon wafer.

1. Substrate Preparation and Cleaning:

- Start with a heavily n-doped Si wafer with a 300 nm thermally grown SiO<sub>2</sub> layer (Si/SiO<sub>2</sub>). The doped Si acts as the gate electrode and the SiO<sub>2</sub> as the gate dielectric.

- Clean the substrate by sonicating sequentially in deionized water, acetone, and isopropyl alcohol (IPA) for 15 minutes each.

- Dry the substrate under a stream of nitrogen gas.

- Perform an oxygen plasma treatment or a piranha clean (use with extreme caution) to remove organic residues and hydroxylate the surface.

- 2. Dielectric Surface Modification (OTS Treatment):

- Place the cleaned substrates in a vacuum desiccator or glovebox antechamber.

- Place a small vial containing a few drops of octadecyltrichlorosilane (OTS) inside with the substrates.

- Evacuate the chamber to allow the OTS to form a vapor that will react with the substrate surface. Let the reaction proceed for 2-4 hours.

- After treatment, rinse the substrates with toluene and IPA to remove excess, unreacted OTS and dry with nitrogen.

- 3. DHDT Solution Preparation and Thin Film Deposition:

- Dissolve the DHDT polymer in a high-boiling-point solvent (e.g., 1,2-dichlorobenzene) at a concentration of 5-10 mg/mL.

- Heat the solution on a hotplate at ~80°C with stirring for at least 1 hour to ensure complete dissolution.[14]

- Filter the solution through a 0.45 μm PTFE filter to remove any aggregates.

- Spin-coat the DHDT solution onto the OTS-treated Si/SiO<sub>2</sub> substrate. Typical parameters are 1000-2000 RPM for 60 seconds. This step should be performed in an inert atmosphere (e.g., a glovebox).

### 4. Thermal Annealing:

- Transfer the coated substrate to a hotplate inside the glovebox.

- Anneal the film at a predetermined optimal temperature (e.g., 150-200°C) for 15-30 minutes to improve film crystallinity.[19]

- Allow the substrate to cool slowly to room temperature on the hotplate after turning it off.

- 5. Source-Drain Electrode Deposition:

- Using a shadow mask to define the channel length (L) and width (W), deposit 50 nm of Gold

(Au) via thermal evaporation. A thin (5 nm) adhesion layer of Chromium (Cr) or Molybdenum

Oxide (MoOx) may be used.

- The deposition rate should be slow (~0.1-0.2 Å/s) to minimize damage to the underlying organic layer.

- 6. Device Characterization:

- Transfer the completed device to a probe station connected to a semiconductor parameter analyzer.

- Measure the output (IDS vs. VDS) and transfer (IDS vs. VGS) characteristics to extract key parameters like charge carrier mobility, threshold voltage, and the ON/OFF ratio.[21]

# **Visualized Workflows and Relationships**

Click to download full resolution via product page

Caption: Workflow for fabricating a bottom-gate, top-contact (BGTC) DHDT-based OFET.

Click to download full resolution via product page

Caption: Troubleshooting flowchart for diagnosing low charge mobility in OFETs.

### **Need Custom Synthesis?**

BenchChem offers custom synthesis for rare earth carbides and specific isotopiclabeling.

Email: info@benchchem.com or Request Quote Online.

### References

- 1. Long-range polymer ordering by directional coating to remarkably enhance the charge carrier mobility in PCDTPT-based organic field-effect transistors - PMC [pmc.ncbi.nlm.nih.gov]

- 2. researchgate.net [researchgate.net]

- 3. gcris.ktun.edu.tr [gcris.ktun.edu.tr]

- 4. researchgate.net [researchgate.net]

- 5. semiengineering.com [semiengineering.com]

- 6. allaboutcircuits.com [allaboutcircuits.com]

- 7. Contact resistance in transistors Wikiversity [en.wikiversity.org]

- 8. researchgate.net [researchgate.net]

- 9. fkf.mpg.de [fkf.mpg.de]

- 10. pubs.acs.org [pubs.acs.org]

- 11. researchgate.net [researchgate.net]

- 12. Molecular Design Concept for Enhancement Charge Carrier Mobility in OFETs: A Review

PMC [pmc.ncbi.nlm.nih.gov]

- 13. mdpi.com [mdpi.com]

- 14. ossila.com [ossila.com]

- 15. s3.eu-central-1.amazonaws.com [s3.eu-central-1.amazonaws.com]

- 16. Single-crystal dielectrics for organic field-effect transistors Journal of Materials Chemistry C (RSC Publishing) [pubs.rsc.org]

- 17. researchgate.net [researchgate.net]

- 18. Contact resistance Wikipedia [en.wikipedia.org]

- 19. researchgate.net [researchgate.net]

- 20. researchgate.net [researchgate.net]

- 21. pubs.aip.org [pubs.aip.org]

- To cite this document: BenchChem. [Optimizing charge mobility in DHDT-based OFETs].

BenchChem, [2025]. [Online PDF]. Available at: [https://www.benchchem.com/product/b180702#optimizing-charge-mobility-in-dhdt-based-ofets]

#### **Disclaimer & Data Validity:**

The information provided in this document is for Research Use Only (RUO) and is strictly not intended for diagnostic or therapeutic procedures. While BenchChem strives to provide accurate protocols, we make no warranties, express or implied, regarding the fitness of this product for every specific experimental setup.

**Technical Support:**The protocols provided are for reference purposes. Unsure if this reagent suits your experiment? [Contact our Ph.D. Support Team for a compatibility check]

Need Industrial/Bulk Grade? Request Custom Synthesis Quote

## BenchChem

Our mission is to be the trusted global source of essential and advanced chemicals, empowering scientists and researchers to drive progress in science and industry. Contact

Address: 3281 E Guasti Rd

Ontario, CA 91761, United States

Phone: (601) 213-4426

Email: info@benchchem.com