# Modeling Non-Volatile Memory in GEM-5 Simulations: Application Notes and Protocols

Author: BenchChem Technical Support Team. Date: December 2025

For Researchers, Scientists, and Drug Development Professionals

### Introduction

**GEM-5** is a modular and extensible open-source full-system simulator widely used in computer architecture research. Its flexibility allows for the modeling of various hardware components, including emerging non-volatile memory (NVM) technologies. This document provides detailed application notes and protocols for modeling NVM in **GEM-5** simulations, catering to researchers and scientists who need to evaluate the impact of these next-generation memories on system performance and power. We will cover two primary methods: using **GEM-5**'s native NVM interface and integrating the more detailed NVMain memory simulator.

# Modeling NVM with GEM-5's Native NVMInterface

**GEM-5** provides a built-in NVMInterface that allows for the basic modeling of NVM devices. This interface is suitable for high-level performance analysis and for studies where the detailed internal behavior of the NVM is not the primary focus. The default NVM\_2400\_1x64 model is parameterized to mimic the behavior of Phase-Change Memory (PCM).[1]

# **Experimental Protocol: Simulating a PCM-based Main Memory**

This protocol outlines the steps to configure and run a **GEM-5** simulation with a PCM-based main memory using the native NVMInterface.

#### 1.1.1. System Configuration:

The primary modification is in the **GEM-5** Python configuration script (e.g., configs/common/FSConfig.py or a custom script). You need to replace the standard DRAM controller with the NVM controller.

- Locate the memory controller instantiation: In your configuration script, find the line where the memory controller is created. It typically looks like this:

- Replace with NVMInterface: Change this line to instantiate the NVM\_2400\_1x64 model:

This will configure the system to use a PCM-like memory with its corresponding timing parameters.

#### 1.1.2. Running the Simulation:

Execute the **GEM-5** simulation from the command line, specifying your configuration script and a benchmark to run.

#### 1.1.3. Analyzing the Output:

After the simulation completes, the results will be in the m5out/ directory. The primary file for analysis is stats.txt. Key statistics to examine for NVM performance include:

- · sim seconds: Total simulation time.

- system.cpu.numCycles: Total number of CPU cycles.

- system.mem ctrls.readRegs: Number of read requests to the memory controller.

- system.mem\_ctrls.writeReqs: Number of write requests to the memory controller.

- system.mem ctrls.avgRdQLatency: Average read queue latency.

- system.mem\_ctrls.avgWrQLatency: Average write queue latency.

### **Data Presentation: NVMInterface Parameters**

The following table summarizes the key timing parameters for the NVM\_2400\_1x64 model, which can be found and modified in src/mem/NVMInterface.py. These parameters define the latency characteristics of the simulated PCM.

| Parameter | Description                            | Value (ns) |

|-----------|----------------------------------------|------------|

| tCL       | CAS Latency                            | 16.67      |

| tRCD      | Row Address to Column<br>Address Delay | 16.67      |

| tRP       | Row Precharge Time                     | 16.67      |

| tRAS      | Row Active Time                        | 40         |

| tWR       | Write Recovery Time                    | 15         |

| tWTR      | Write to Read Delay                    | 7.5        |

# **Advanced NVM Modeling with NVMain**

For more detailed and accurate modeling of various NVM technologies like PCM, STT-MRAM, and ReRAM, integrating the NVMain memory simulator with **GEM-5** is the recommended approach.[2] NVMain provides a rich set of configurable parameters to model the specific characteristics of different NVMs, including endurance and energy consumption.

# Experimental Protocol: Simulating STT-MRAM with GEM-5 and NVMain

This protocol details the steps to set up a hybrid **GEM-5** and NVMain simulation environment to model an STT-MRAM main memory.

#### 2.1.1. Environment Setup:

Obtain GEM-5 and NVMain: Clone the GEM-5 and NVMain repositories. It is often

recommended to use a version of GEM-5 that is known to be compatible with the version of

NVMain you are using. The gem5-nvmain-hybrid-simulator repository on GitHub provides a

pre-patched and compatible version.

- Patch GEM-5 with NVMain: NVMain provides patches to integrate it with GEM-5. Apply the

patch using the patch command in the GEM-5 root directory.

- Compile GEM-5 with NVMain Support: Compile GEM-5 using scons, specifying the path to the NVMain directory.

#### 2.1.2. Configuration:

NVMain Configuration File: Create or modify an NVMain configuration file to specify the parameters for STT-MRAM. An example configuration file might look like this:

#### 2.1.3. Running the Simulation:

Execute the **GEM-5** simulation with the appropriate command-line arguments.

#### 2.1.4. Analyzing NVMain Output:

NVMain generates its own statistics, which can be found in the m5out directory, typically in a file named nvmain.stats. This file contains detailed information about the NVM's behavior, including:

- averageLatency: Average memory access latency.

- totalEnergy: Total energy consumed by the NVM.

- totalReads and totalWrites: Total number of read and write operations.

- Endurance-related statistics, if an endurance model is enabled.

# **Data Presentation: Comparative NVM Performance**

The following table presents a summary of simulated performance and energy characteristics for DRAM, PCM, and STT-MRAM, compiled from various studies using **GEM-5** and NVMain. These values are indicative and can vary based on the specific model parameters and workload.

| Memory<br>Technology | Read Latency<br>(ns) | Write Latency<br>(ns) | Dynamic Read<br>Energy (pJ/bit) | Dynamic Write<br>Energy (pJ/bit) |

|----------------------|----------------------|-----------------------|---------------------------------|----------------------------------|

| DDR3                 | 15                   | 15                    | 2                               | 2                                |

| PCM                  | 50                   | 150                   | 2.5                             | 10                               |

| STT-MRAM             | 20                   | 30                    | 1                               | 5                                |

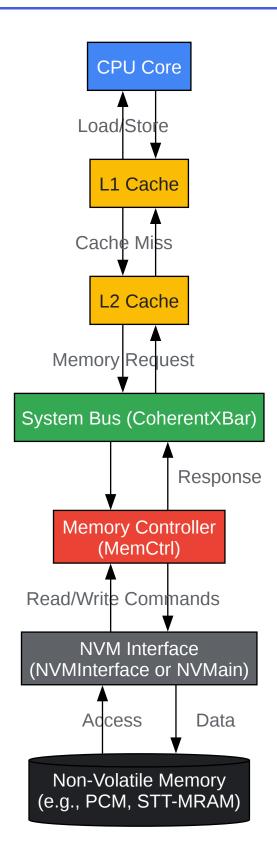

# Visualization of NVM Modeling in GEM-5 GEM-5 Memory Hierarchy with NVM

This diagram illustrates the logical flow of a memory request from the CPU to an NVM device within the **GEM-5** simulation environment.

Click to download full resolution via product page

**GEM-5** Memory Hierarchy with NVM

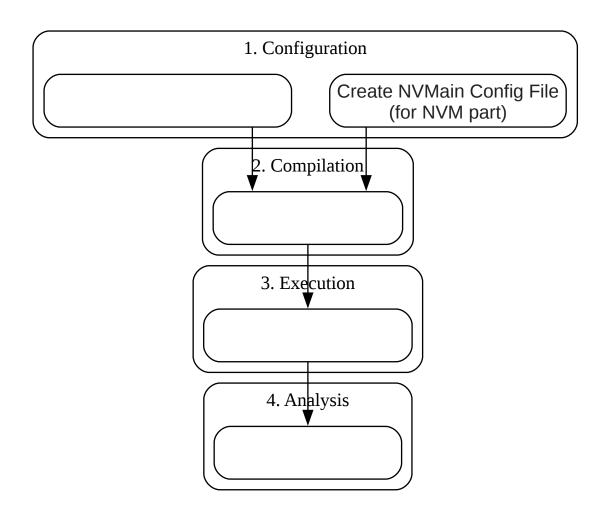

## **Hybrid Memory Simulation Workflow**

This diagram outlines the workflow for setting up and running a hybrid memory simulation in **GEM-5**, combining both DRAM and NVM.

Click to download full resolution via product page

Hybrid Memory Simulation Workflow

# Conclusion

Modeling non-volatile memory in **GEM-5** is a powerful technique for exploring the architectural implications of these emerging technologies. For high-level studies, **GEM-5**'s native NVMInterface provides a straightforward approach. For more in-depth and accurate analysis of specific NVM types, integrating NVMain is the preferred method. By following the protocols and utilizing the data presented in this document, researchers can effectively simulate and evaluate NVM-based systems to drive innovation in computer architecture and related scientific fields.

#### **Need Custom Synthesis?**

BenchChem offers custom synthesis for rare earth carbides and specific isotopiclabeling.

Email: info@benchchem.com or Request Quote Online.

#### References

- 1. Running non-volatile memory in Gem5 | by Nick Felker | Medium [fleker.medium.com]

- 2. ieeexplore.ieee.org [ieeexplore.ieee.org]

- To cite this document: BenchChem. [Modeling Non-Volatile Memory in GEM-5 Simulations: Application Notes and Protocols]. BenchChem, [2025]. [Online PDF]. Available at: [https://www.benchchem.com/product/b12410503#how-to-model-non-volatile-memory-nvm-in-gem-5-simulations]

#### **Disclaimer & Data Validity:**

The information provided in this document is for Research Use Only (RUO) and is strictly not intended for diagnostic or therapeutic procedures. While BenchChem strives to provide accurate protocols, we make no warranties, express or implied, regarding the fitness of this product for every specific experimental setup.

**Technical Support:** The protocols provided are for reference purposes. Unsure if this reagent suits your experiment? [Contact our Ph.D. Support Team for a compatibility check]

Need Industrial/Bulk Grade? Request Custom Synthesis Quote

# BenchChem

Our mission is to be the trusted global source of essential and advanced chemicals, empowering scientists and researchers to drive progress in science and industry. Contact

Address: 3281 E Guasti Rd

Ontario, CA 91761, United States

Phone: (601) 213-4426

Email: info@benchchem.com