# Minimizing hysteresis in GeAs device transfer characteristics

Author: BenchChem Technical Support Team. Date: December 2025

| Compound of Interest |                    |           |

|----------------------|--------------------|-----------|

| Compound Name:       | Germanium arsenide |           |

| Cat. No.:            | B076424            | Get Quote |

#### **Technical Support Center: GeAs Devices**

This technical support center provides troubleshooting guidance and frequently asked questions (FAQs) for researchers, scientists, and drug development professionals working with **Germanium Arsenide** (GeAs) devices. The focus is on minimizing hysteresis in the transfer characteristics of these devices during experimental procedures.

#### Frequently Asked Questions (FAQs)

Q1: What is hysteresis in the transfer characteristics of a GeAs device, and why is it problematic?

A1: Hysteresis in the transfer characteristics of a GeAs field-effect transistor (FET) refers to the discrepancy in the drain current (Ids) when the gate voltage (Vgs) is swept in the forward and reverse directions. This phenomenon can be visualized as two separate curves for the forward and reverse sweeps, creating a loop. Hysteresis is problematic because it introduces instability and unpredictability in the device's electrical behavior, making it difficult to determine a reliable threshold voltage.[1][2] This can lead to inaccurate measurements and unreliable device performance in sensing and electronic applications.

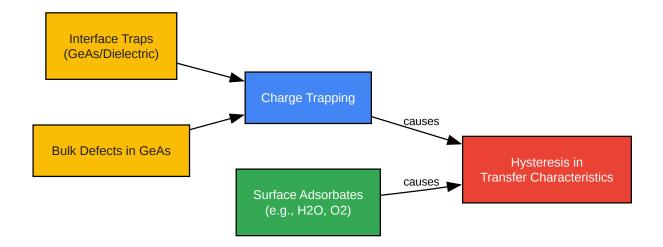

Q2: What are the primary causes of hysteresis in GeAs devices?

A2: The primary causes of hysteresis in GeAs and other semiconductor devices are generally attributed to:

#### Troubleshooting & Optimization

- Charge Trapping: Charge carriers can become trapped at the interface between the GeAs channel and the dielectric layer, or within defect states in the GeAs material itself.[3][4][5] These trapped charges create an internal electric field that affects the channel conductivity, leading to a shift in the threshold voltage.

- Surface Contamination and Adsorbates: Molecules from the ambient environment, such as

water and oxygen, can be adsorbed onto the surface of the GeAs flake.[2][6] These

molecules can act as charge traps or introduce surface dipoles that influence the device

characteristics.

- Intrinsic Defects: The GeAs crystal itself may have intrinsic defects, such as vacancies or dislocations, which can act as charge trapping centers.

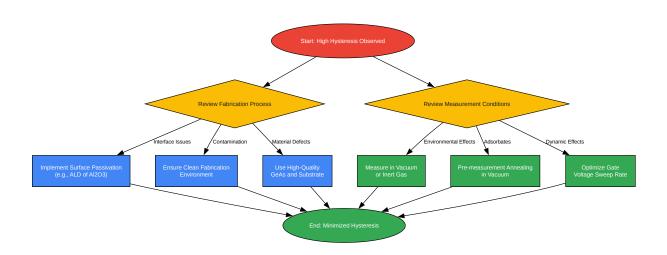

Q3: How can I minimize hysteresis in my GeAs device during fabrication?

A3: Minimizing hysteresis starts with careful device fabrication. Key strategies include:

- Surface Passivation: Applying a passivation layer, such as a high-quality dielectric like Al2O3 or SiO2, can protect the GeAs surface from atmospheric adsorbates and reduce the density of interface traps.[8][9]

- Clean Fabrication Environment: Processing devices in a cleanroom environment with controlled humidity and atmosphere can reduce surface contamination.

- High-Quality Substrate and Dielectric: Using a high-quality substrate and gate dielectric with a low density of defects is crucial for minimizing interface trapping.

Q4: Can experimental conditions during measurement affect hysteresis?

A4: Yes, the experimental setup and measurement parameters can significantly impact the observed hysteresis. Factors to consider include:

• Gate Voltage Sweep Rate: A slower sweep rate may allow more time for charge traps to fill and empty, potentially increasing the hysteresis loop. Conversely, very fast sweep rates might not reveal the full extent of trapping.

- Temperature: Temperature can affect the trapping and de-trapping rates of charge carriers. [10][11] Performing measurements at different temperatures can help to understand the nature of the trap states.

- Ambient Environment: Measuring in a vacuum or an inert gas atmosphere (like N2 or Ar) can minimize the influence of atmospheric adsorbates like water and oxygen.[2]

#### **Troubleshooting Guide**

### Troubleshooting & Optimization

Check Availability & Pricing

| Issue                                                      | Possible Causes                                                                                                                                                                                                                  | Troubleshooting Steps                                                                                                                                                                                                     |

|------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Large hysteresis loop in transfer characteristics.         | High density of interface trap states between the GeAs and the dielectric.                                                                                                                                                       | 1. Perform surface passivation with a high-quality dielectric (e.g., Al2O3) using techniques like Atomic Layer Deposition (ALD).[8][12] 2. Anneal the device in a controlled atmosphere to improve the interface quality. |

| Adsorption of molecules (e.g., water) on the GeAs surface. | 1. Perform measurements in a vacuum or an inert gas environment. 2. Gently anneal the device under vacuum before measurement to desorb adsorbates.[6]                                                                            |                                                                                                                                                                                                                           |

| Bulk defects within the GeAs material.                     | 1. Use high-quality, single-<br>crystal GeAs flakes with low<br>defect density. 2. Characterize<br>the material for defects using<br>techniques like Raman<br>spectroscopy or<br>photoluminescence before<br>device fabrication. |                                                                                                                                                                                                                           |

| Hysteresis changes with measurement time.                  | Slow charge trapping and de-<br>trapping dynamics.                                                                                                                                                                               | 1. Vary the gate voltage sweep rate to investigate the time dependence of the trapping mechanisms. 2. Allow the device to stabilize at each gate voltage point before measuring the current (pulsed I-V measurements).[2] |

| Device performance degrades over time.                     | Chemical degradation or oxidation of the GeAs surface.                                                                                                                                                                           | 1. Ensure proper encapsulation of the device to protect it from the ambient environment. 2. Store devices                                                                                                                 |

in a desiccator or an inert atmosphere.

#### **Experimental Protocols**

#### Protocol 1: Fabrication of a Low-Hysteresis GeAs Field-Effect Transistor

This protocol is based on methodologies that have been shown to produce GeAs FETs with negligible hysteresis.[7][10][11]

- Substrate Preparation:

- Begin with a highly doped silicon wafer with a thermally grown SiO2 layer (e.g., 300 nm) to serve as the back gate and gate dielectric.

- Clean the substrate sequentially with acetone, isopropanol, and deionized water in an ultrasonic bath.

- Dry the substrate with a nitrogen gun.

- Exfoliation and Transfer of GeAs:

- Mechanically exfoliate thin flakes of GeAs from a bulk crystal onto the prepared SiO2/Si substrate.

- o Identify suitable thin flakes (a few layers) using an optical microscope.

- Contact Electrode Fabrication:

- Use standard electron beam lithography (EBL) to define the source and drain contact areas.

- Deposit metal contacts (e.g., Cr/Au, 5 nm/50 nm) using electron beam evaporation.

- Perform a lift-off process in acetone to remove the excess metal and photoresist.

- Annealing:

Anneal the fabricated device in a high-vacuum chamber (e.g., < 10-5 mbar) at a moderate temperature (e.g., 150-200 °C) for several hours to improve contact quality and remove surface adsorbates.

## Protocol 2: Characterization of Hysteresis in GeAs Devices

- Measurement Setup:

- Place the device in a vacuum probe station to control the measurement environment and temperature.

- Connect the source, drain, and back gate terminals to a semiconductor parameter analyzer.

- Transfer Characteristic Measurement:

- Apply a small, constant drain-source voltage (Vds), for example, 100 mV.

- Sweep the gate-source voltage (Vgs) from a negative voltage to a positive voltage (forward sweep) and then back to the negative voltage (reverse sweep).

- Record the drain-source current (Ids) at each Vgs point for both sweep directions.

- Plot Ids as a function of Vgs to visualize the hysteresis loop.

- Parameter Extraction:

- From the transfer curves, extract key parameters such as the threshold voltage (Vth) for both sweep directions.

- $\circ$  Quantify the hysteresis as the difference in Vth between the forward and reverse sweeps ( $\Delta Vth$ ).

#### **Visualizations**

Click to download full resolution via product page

Caption: Primary causes of hysteresis in GeAs devices.

Click to download full resolution via product page

Caption: Workflow for troubleshooting and minimizing hysteresis.

#### **Need Custom Synthesis?**

BenchChem offers custom synthesis for rare earth carbides and specific isotopiclabeling.

Email: info@benchchem.com or Request Quote Online.

#### References

- 1. allaboutcircuits.com [allaboutcircuits.com]

- 2. arxiv.org [arxiv.org]

- 3. mdpi.com [mdpi.com]

- 4. [2310.05902] Impact of interface traps on charge noise, mobility and percolation density in Ge/SiGe heterostructures [arxiv.org]

- 5. Impact of interface traps on charge noise, mobility and percolation density in Ge/SiGe heterostructures (2023) | L. Massai | 5 Citations [scispace.com]

- 6. arxiv.org [arxiv.org]

- 7. researchgate.net [researchgate.net]

- 8. fastercapital.com [fastercapital.com]

- 9. arxiv.org [arxiv.org]

- 10. pubs.acs.org [pubs.acs.org]

- 11. researchgate.net [researchgate.net]

- 12. docs.lib.purdue.edu [docs.lib.purdue.edu]

- To cite this document: BenchChem. [Minimizing hysteresis in GeAs device transfer characteristics]. BenchChem, [2025]. [Online PDF]. Available at: [https://www.benchchem.com/product/b076424#minimizing-hysteresis-in-geas-devicetransfer-characteristics]

#### **Disclaimer & Data Validity:**

The information provided in this document is for Research Use Only (RUO) and is strictly not intended for diagnostic or therapeutic procedures. While BenchChem strives to provide accurate protocols, we make no warranties, express or implied, regarding the fitness of this product for every specific experimental setup.

**Technical Support:**The protocols provided are for reference purposes. Unsure if this reagent suits your experiment? [Contact our Ph.D. Support Team for a compatibility check]

Need Industrial/Bulk Grade? Request Custom Synthesis Quote

## BenchChem

Our mission is to be the trusted global source of essential and advanced chemicals, empowering scientists and researchers to drive progress in science and industry. Contact

Address: 3281 E Guasti Rd

Ontario, CA 91761, United States

Phone: (601) 213-4426

Email: info@benchchem.com