# Minimizing gate leakage in 2-n-Octylthiophene based transistors

Author: BenchChem Technical Support Team. Date: December 2025

Compound of Interest

Compound Name: 2-n-Octylthiophene

Cat. No.: B1209704

Get Quote

# Technical Support Center: 2-n-Octylthiophene Based Transistors

This technical support center provides troubleshooting guidance and frequently asked questions (FAQs) to assist researchers in minimizing gate leakage current in **2-n-Octylthiophene** based organic thin-film transistors (OTFTs).

## Frequently Asked Questions (FAQs)

Q1: What are the primary causes of high gate leakage current in my **2-n-Octylthiophene** OTFTs?

High gate leakage current in OTFTs can stem from several sources. The most common culprits include:

- Poor Dielectric Quality: Pinholes, cracks, or a high density of trap states within the gate dielectric layer can create conductive pathways.[1]

- Unpatterned Semiconductor Layer: When the active 2-n-Octylthiophene layer extends

beyond the intended channel region and overlaps with the gate electrode area outside the

source/drain contacts, it creates a parasitic conduction path.[2][3][4] This is a very common

issue on devices fabricated on common gate substrates like Si/SiO2.[4]

- Interfacial Defects: A poor interface between the semiconductor and the dielectric can lead to charge trapping and increased leakage.[3] Surface roughness of the dielectric layer can also contribute to this by creating charge trapping sites.[2]

- Fabrication-Induced Damage: Processes like dry etching to pattern device layers can cause irreversible damage to the sidewalls of the gate insulator and semiconductor, forming unintended leakage paths.[5]

- Contamination: Residues from photolithography or other processing steps can introduce mobile ions or conductive particles into the device layers.

Q2: How does the choice of gate dielectric material affect gate leakage?

The gate dielectric's properties are critical. A good dielectric should have a large bandgap, low defect density, and be sufficiently thick to prevent charge tunneling.[1] While high-k dielectrics can improve transistor performance by allowing for a lower operating voltage, they must be of high quality to prevent increased leakage.[6] If the dielectric is too thin, direct tunneling current can become a significant leakage source.[7] For stable operation, the leakage current should ideally be below  $10^{-9}$  A/cm<sup>2</sup>.[8]

Q3: Can the device architecture influence the gate leakage current?

Absolutely. In bottom-gate architectures, misalignment of the source and drain electrodes relative to the gate can cause significant leakage.[2] Furthermore, using a common gate for multiple devices on a single substrate will lead to high leakage unless the semiconductor is patterned for each individual transistor.[2][4] Patterning the active region to confine it to the channel significantly reduces non-channel leakage.[2][3]

Q4: My OFF-current is high. Is this related to gate leakage?

Yes, a high OFF-current is often directly correlated with high gate leakage. The gate leakage current contributes to the total current measured at the drain when the transistor is in its "off" state, making it difficult to achieve a low OFF-current and a high ON/OFF ratio.[2] This can distort the transistor's performance curves, particularly in the linear region.[2]

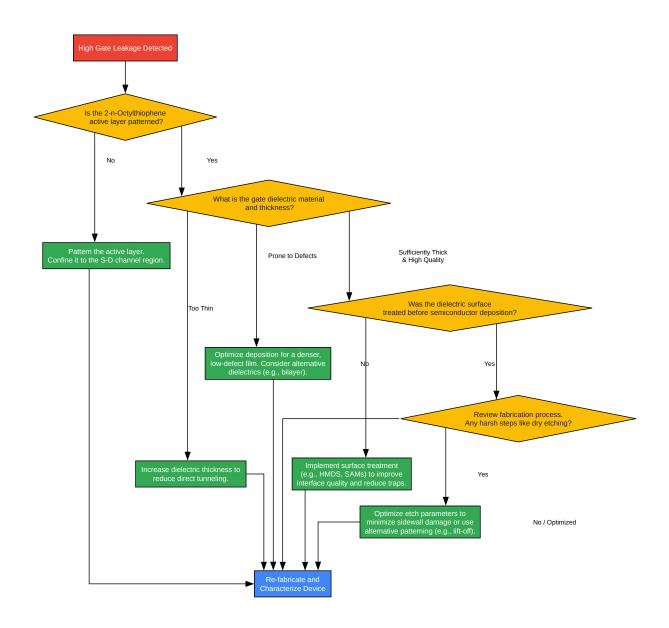

### **Troubleshooting Guide**

### Troubleshooting & Optimization

Check Availability & Pricing

Issue: Unusually High Gate Current (IG) Observed During Measurement

This guide provides a step-by-step process to diagnose and resolve high gate leakage in your **2-n-Octylthiophene** transistors.

Click to download full resolution via product page

Caption: Troubleshooting workflow for high gate leakage.

## **Data on Gate Leakage Mitigation Strategies**

The following table summarizes key quantitative findings from literature on factors influencing gate leakage in organic transistors.

| Strategy                   | Parameter<br>Modified         | Result                                                                                                 | Reference<br>Device           | Improved<br>Device                | Source |

|----------------------------|-------------------------------|--------------------------------------------------------------------------------------------------------|-------------------------------|-----------------------------------|--------|

| Active Layer<br>Patterning | Semiconduct<br>or Area        | Reduced gate leakage by confining the active layer to the channel region.                              | Unpatterned<br>Active Layer   | Patterned<br>Active Layer         | [2][3] |

| Dielectric<br>Thickness    | SiO <sub>2</sub><br>Thickness | Increased thickness reduces leakage current and prevents rapid dielectric breakdown.                   | 90 nm                         | 300 nm                            | [3]    |

| Bilayer<br>Dielectric      | Dielectric<br>Structure       | Improved ON/OFF ratio and mobility by combining a high-k layer with a low- polarity interfacial layer. | Single Layer<br>(PVA or PVP)  | Bilayer<br>(PVA/CL-<br>PVP)       | [2]    |

| Surface<br>Treatment       | SiO <sub>2</sub> Surface      | HMDS treatment improved the ON/OFF ratio significantly.                                                | Untreated<br>SiO <sub>2</sub> | HMDS-<br>Treated SiO <sub>2</sub> | [2]    |

| Interfacial<br>Layer | Metal-<br>Semiconduct<br>or Contact | Introduction of a Self- Assembled Monolayer (SAM) dipole layer suppressed minority carrier injection. | No SAM | With SAM | [9] |

|----------------------|-------------------------------------|-------------------------------------------------------------------------------------------------------|--------|----------|-----|

|----------------------|-------------------------------------|-------------------------------------------------------------------------------------------------------|--------|----------|-----|

## **Experimental Protocols**

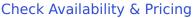

## Protocol 1: Fabrication of a Bottom-Gate, Top-Contact 2n-Octylthiophene OTFT

This protocol outlines a standard procedure for fabricating test devices to evaluate gate leakage.

Click to download full resolution via product page

Caption: Experimental workflow for OTFT fabrication.

#### Methodology:

- Substrate Preparation: Begin with a clean substrate (e.g., silicon wafer or glass). Use a standard cleaning procedure involving sonication in acetone, isopropyl alcohol (IPA), and deionized (DI) water, followed by drying with nitrogen gas.

- Gate Electrode Formation: Deposit the gate electrode material (e.g., 50 nm of Aluminum) via thermal evaporation or sputtering through a shadow mask.

- Dielectric Deposition: Deposit the gate dielectric layer. For SiO<sub>2</sub>, use Plasma-Enhanced Chemical Vapor Deposition (PECVD). For polymeric dielectrics like PMMA, use spin-coating followed by a baking step to remove the solvent. The thickness should be carefully controlled (e.g., 200-500 nm).[3]

- Surface Treatment (Optional but Recommended): To improve the semiconductor/dielectric interface, a surface treatment like vapor-phase hexamethyldisilazane (HMDS) can be applied. This makes the surface more hydrophobic and can improve molecular ordering of the semiconductor.[2]

- Semiconductor Deposition: Prepare a solution of **2-n-Octylthiophene** in a suitable solvent (e.g., toluene, chloroform). Spin-coat the solution onto the substrate to form a thin film.

- Annealing: Anneal the substrate at an optimized temperature (e.g., 100-150 °C) to improve the crystallinity and morphology of the semiconductor film.

- Source/Drain Electrode Deposition: Deposit the source and drain contacts (e.g., 50 nm of Gold) on top of the semiconductor layer using thermal evaporation through a shadow mask.

This defines the channel length and width.

- Characterization: Transfer the device to a probe station connected to a semiconductor parameter analyzer (e.g., Keithley 4200-SCS) for electrical characterization.[10]

## Protocol 2: Characterizing Gate Leakage Current Methodology:

- Setup: Place the fabricated OTFT on a probe station in a dark, shielded box to minimize light and electrical noise. Connect probes to the source, drain, and gate electrodes.

- Gate Leakage vs. Gate Voltage (IG-VG):

- Ground the source and drain electrodes (VS = VD = 0 V).

- Sweep the gate voltage (VG) across the desired operating range (e.g., from +20 V to -60 V for a p-type transistor).

- At each VG step, measure the current flowing into the gate terminal (IG).

- Plot IG versus VG. For a healthy device, this current should be in the picoampere (pA) to low nanoampere (nA) range.

- Transfer Characteristics (ID-VG):

- Apply a constant, small drain voltage (VD), typically in the linear region (e.g., -5 V).

- Sweep the gate voltage (VG) as before.

- Simultaneously measure the drain current (ID) and the gate current (IG).

- Plot both ID and IG on a logarithmic scale versus VG. In an ideal device, IG should be several orders of magnitude smaller than the OFF-state ID.[8] A high IG that tracks with ID indicates significant leakage. A proposed measurement technique to mitigate the impact of gate leakage on transfer characteristics involves sweeping both gate and drain voltages simultaneously.[10]

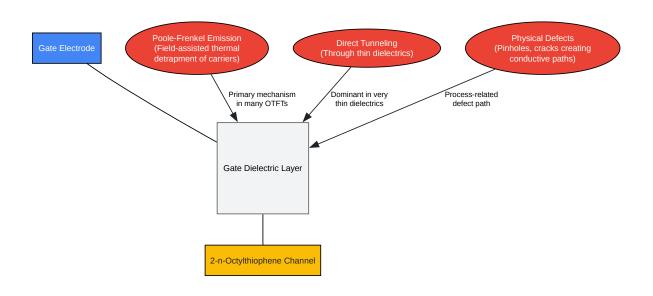

## **Understanding Gate Leakage Mechanisms**

Gate leakage in OTFTs is primarily governed by the transport of charge carriers through the dielectric layer. The dominant mechanisms depend on the quality of the dielectric, the applied electric field, and temperature.

Click to download full resolution via product page

**Caption:** Key mechanisms of gate leakage through the dielectric.

- Poole-Frenkel Emission: This is often the main gate leakage mechanism in OTFTs.[11] It

involves the field-assisted thermal excitation of trapped charge carriers from trap states

within the dielectric into the conduction band, allowing them to move through the material.

- Direct Tunneling: When the dielectric layer is very thin (typically less than a few nanometers), charge carriers can tunnel directly through the potential barrier from the gate to the semiconductor channel.[7]

- Defect-Mediated Conduction: Physical defects such as pinholes, cracks, or grain boundaries

in the dielectric can create localized conductive pathways, leading to a significant increase in

leakage current.[1] This is often a result of non-optimal deposition or processing conditions.

#### **Need Custom Synthesis?**

BenchChem offers custom synthesis for rare earth carbides and specific isotopiclabeling.

Email: info@benchchem.com or Request Quote Online.

#### References

- 1. researchgate.net [researchgate.net]

- 2. researchgate.net [researchgate.net]

- 3. mdpi.com [mdpi.com]

- 4. researchgate.net [researchgate.net]

- 5. Gate Dielectric Leakage Reduction in Hard-Mask Defined and Dry-Etch Patterned Organic TFTs Devices | IEEE Journals & Magazine | IEEE Xplore [ieeexplore.ieee.org]

- 6. ijstr.org [ijstr.org]

- 7. matec-conferences.org [matec-conferences.org]

- 8. pubs.aip.org [pubs.aip.org]

- 9. researchgate.net [researchgate.net]

- 10. research.physics.unc.edu [research.physics.unc.edu]

- 11. researchgate.net [researchgate.net]

- To cite this document: BenchChem. [Minimizing gate leakage in 2-n-Octylthiophene based transistors]. BenchChem, [2025]. [Online PDF]. Available at: [https://www.benchchem.com/product/b1209704#minimizing-gate-leakage-in-2-n-octylthiophene-based-transistors]

#### **Disclaimer & Data Validity:**

The information provided in this document is for Research Use Only (RUO) and is strictly not intended for diagnostic or therapeutic procedures. While BenchChem strives to provide accurate protocols, we make no warranties, express or implied, regarding the fitness of this product for every specific experimental setup.

**Technical Support:**The protocols provided are for reference purposes. Unsure if this reagent suits your experiment? [Contact our Ph.D. Support Team for a compatibility check]

Need Industrial/Bulk Grade? Request Custom Synthesis Quote

## BenchChem

Our mission is to be the trusted global source of essential and advanced chemicals, empowering scientists and researchers to drive progress in science and industry. Contact

Address: 3281 E Guasti Rd

Ontario, CA 91761, United States

Phone: (601) 213-4426

Email: info@benchchem.com