# Kernanliegen der Zuverlässigkeit und Ausfallmechanismen

**Author:** BenchChem Technical Support Team. **Date:** December 2025

## Compound of Interest

Compound Name: Bis(ethylmethylamino)silane

Cat. No.: B6360028

[Get Quote](#)

Die Zuverlässigkeit von Gate-Dielektrika wird durch verschiedene physikalische Mechanismen beeinträchtigt, die zu einer Verschlechterung und schließlich zum Ausfall des Bauteils führen können. Das Verständnis dieser Mechanismen ist die Grundlage für die Entwicklung robuster Testprotokolle und zuverlässiger Lebensdauervorhersagen.

- Zeitabhängiger dielektrischer Durchbruch (Time-Dependent Dielectric Breakdown, TDDB): Dies ist ein wesentlicher Ausfallmechanismus, bei dem das Gate-Oxid nach längerem Betrieb bei relativ niedrigen elektrischen Feldern durchbricht.[1] Der Durchbruch wird durch die Bildung eines leitenden Pfades durch das Oxid verursacht, der durch die Akkumulation von Defekten entsteht, die durch elektrische Belastung erzeugt werden.[2][3]

- Heißträgerinjektion (Hot Carrier Injection, HCl): Hochenergetische ("heiße") Elektronen oder Löcher können in das Gate-Dielektrikum injiziert werden und dort Defekte erzeugen, insbesondere an der Si/SiO<sub>2</sub>-Grenzfläche.[2] Dies führt zu einer Verschlechterung der Transistorparameter wie der Schwellenspannung und des Transkonduktanz.

- Negative Bias Temperature Instability (NBTI): Bei Anlegen einer negativen Spannung an das Gate bei erhöhten Temperaturen kann es zu einer signifikanten Verschiebung der Schwellenspannung kommen. Dieser Effekt ist besonders relevant in p-Kanal-MOSFETs und wird durch die Erzeugung von Grenzflächenzuständen und eingefangenen Ladungen im Dielektrikum verursacht.[4]

- Stressinduzierter Leckstrom (Stress-Induced Leakage Current, SILC): Nach elektrischer Belastung kann ein Anstieg des Leckstroms durch das Gate-Dielektrikum bei niedrigen

Spannungen beobachtet werden. Dies ist auf die Bildung von Defekten im Oxid zurückzuführen, die als "Sprungbretter" für das Tunneln von Ladungsträgern dienen.

## Experimentelle Protokolle zur Evidenzsammlung

Eine systematische Bewertung der Zuverlässigkeit erfordert präzise und wiederholbare experimentelle Messungen. Die folgenden Protokolle beschreiben die wichtigsten elektrischen Charakterisierungstechniken zur Sammlung von "Evidenz" für den Zustand des Gate-Dielektrikums.

### Protokoll 1: Kapazitäts-Spannungs-Messung (C-V)

Ziel: Bestimmung der effektiven Oxiddicke (EOT), der Dotierungskonzentration des Substrats und der Qualität der Grenzfläche zwischen Dielektrikum und Halbleiter.

Methodik:

- Probenvorbereitung: Verwendung von MOS-Kondensator-Teststrukturen mit definierten Gate-Flächen. Sicherstellung eines guten elektrischen Kontakts zum Gate und zum Substrat.

- Geräteeinrichtung: Anschluss der Teststruktur an ein Präzisions-LCR-Meter oder ein Halbleiter-Charakterisierungssystem. Die Messung erfolgt typischerweise bei einer hohen Frequenz (z. B. 1 MHz).

- Messablauf:

- Anlegen einer DC-Vorspannung an das Gate, die von der Akkumulation (z. B. negative Spannung für p-Substrat) bis zur Inversion (positive Spannung für p-Substrat) durchgefahren wird.<sup>[5]</sup>

- Überlagerung eines kleinen AC-Signals (typischerweise 15-30 mV) mit der DC-Vorspannung.

- Messung der differentiellen Kapazität als Funktion der angelegten DC-Spannung.

- Datenanalyse:

- Bestimmung der Oxidkapazität ( $C_{ox}$ ) aus dem Akkumulationsbereich der C-V-Kurve.

- Berechnung der effektiven Oxiddicke (EOT) unter Verwendung der Formel:  $EOT = (\epsilon_{SiO_2} * A) / C_{ox}$ , wobei  $\epsilon_{SiO_2}$  die Permittivität von Siliziumdioxid und A die Gate-Fläche ist.

- Extraktion der Flachbandspannung ( $V_{fb}$ ) und der Schwellenspannung ( $V_{th}$ ).

- Analyse der Form der C-V-Kurve im Verarmungsbereich zur Bestimmung der Dichte der Grenzflächenzustände ( $D_{it}$ ).

## Protokoll 2: Strom-Spannungs-Messung (I-V)

Ziel: Charakterisierung des Leckstroms durch das Gate-Dielektrikum und Bestimmung der Durchbruchspannung.

Methodik:

- Probenvorbereitung: Verwendung von MOS-Kondensator- oder Transistor-Teststrukturen.

- Geräteeinrichtung: Anschluss der Teststruktur an ein Halbleiter-Parametersystem oder eine Source-Measure Unit (SMU).

- Messablauf (Spannungsrampe):

- Anlegen einer schrittweise ansteigenden Spannung an das Gate (V-Ramp-Test).[\[6\]](#)

- Messung des resultierenden Stroms durch das Dielektrikum bei jedem Spannungsschritt.

- Die Rampe wird fortgesetzt, bis ein abrupter Anstieg des Stroms den dielektrischen Durchbruch anzeigt.

- Datenanalyse:

- Darstellung des Leckstroms (oder der Leckstromdichte  $J = I/A$ ) als Funktion der Gatespannung in einer logarithmischen Skala.

- Identifizierung verschiedener Leitungsmechanismen (z. B. Fowler-Nordheim-Tunneln, Direktes Tunneln) durch Analyse der Kurvenform.

- Bestimmung der Durchbruchspannung ( $V_{bd}$ ) als die Spannung, bei der der Strom einen vordefinierten Schwellenwert überschreitet oder ein plötzlicher Anstieg auftritt.

## Protokoll 3: Zeitabhängiger dielektrischer Durchbruch (TDDB)

Ziel: Beschleunigte Alterung des Dielektrikums zur Vorhersage seiner Lebensdauer unter normalen Betriebsbedingungen.

Methodik:

- Probenvorbereitung: Verwendung einer statistisch signifikanten Anzahl von identischen Teststrukturen.

- Geräteeinrichtung: Anschluss an ein Zuverlässigkeitstestsystem, das mehrere Bauteile parallel belasten und überwachen kann.

- Messablauf (Constant Voltage Stress, CVS):

- Anlegen einer konstanten, hohen Spannung (unterhalb der sofortigen Durchbruchspannung) an das Gate.[1]

- Kontinuierliche Überwachung des Leckstroms durch das Dielektrikum.

- Aufzeichnung der Zeit bis zum Durchbruch ( $t_{bd}$ ), die durch einen plötzlichen Anstieg des Leckstroms definiert ist.

- Wiederholung des Tests bei verschiedenen Spannungen und/oder Temperaturen an verschiedenen Bauteilgruppen.

- Datenanalyse:

- Erstellung einer Weibull-Verteilung der Zeit-bis-zum-Ausfall-Daten für jede Stressbedingung.

- Extrapolation der Daten auf niedrigere Betriebsspannungen unter Verwendung eines geeigneten Lebensdauermodells (z. B. E-Modell oder 1/E-Modell), um die Lebensdauer des Dielektrikums unter normalen Betriebsbedingungen vorherzusagen.

## Datenpräsentation

Die aus den experimentellen Protokollen gewonnenen quantitativen Daten werden zur einfachen Vergleichbarkeit und Analyse in strukturierten Tabellen zusammengefasst.

Tabelle 1: Zusammenfassung der C-V-Charakterisierung

| Parameter                          | Symbol | Typischer Wert (für<br>~2 nm SiO <sub>2</sub> ) | Einheit                           |

|------------------------------------|--------|-------------------------------------------------|-----------------------------------|

| Effektive Oxiddicke                | EOT    | 1.8 - 2.2                                       | nm                                |

| Oxidkapazität                      | C_ox   | 1.5 - 1.9                                       | μF/cm <sup>2</sup>                |

| Flachbandspannung                  | V_fb   | -0.8 - -1.0                                     | V                                 |

| Dichte der<br>Grenzflächenzustände | D_it   | 1x10 <sup>10</sup> - 5x10 <sup>11</sup>         | cm <sup>-2</sup> eV <sup>-1</sup> |

Tabelle 2: Zusammenfassung der I-V- und TDDB-Charakterisierung

| Parameter                                            | Symbol          | Typischer Wert (für<br>~2 nm SiO <sub>2</sub> ) | Einheit           |

|------------------------------------------------------|-----------------|-------------------------------------------------|-------------------|

| Leckstromdichte bei 1V                               | J_g             | 1x10 <sup>-3</sup> - 1x10 <sup>-1</sup>         | A/cm <sup>2</sup> |

| Durchbruchspannung                                   | V_bd            | 3.0 - 4.0                                       | V                 |

| Durchbruchsfeldstärke                                | E_bd            | 15 - 20                                         | MV/cm             |

| Ladung bis zum Durchbruch                            | Q_bd            | 1 - 10                                          | C/cm <sup>2</sup> |

| Charakteristische Lebensdauer (63%) bei hohem Stress | t <sub>63</sub> | 10 <sup>3</sup> - 10 <sup>5</sup>               | s                 |

| Weibull-Steigung                                     | β               | 1.5 - 2.5                                       | -                 |

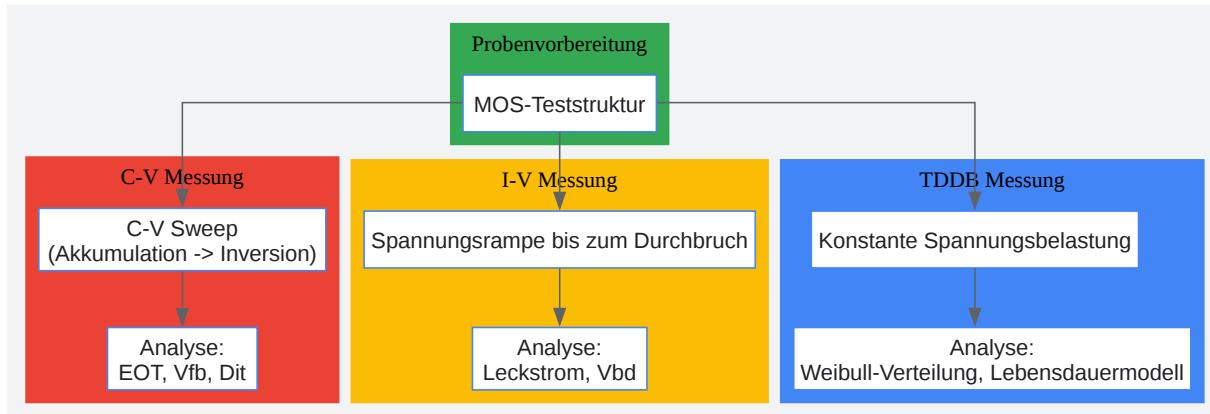

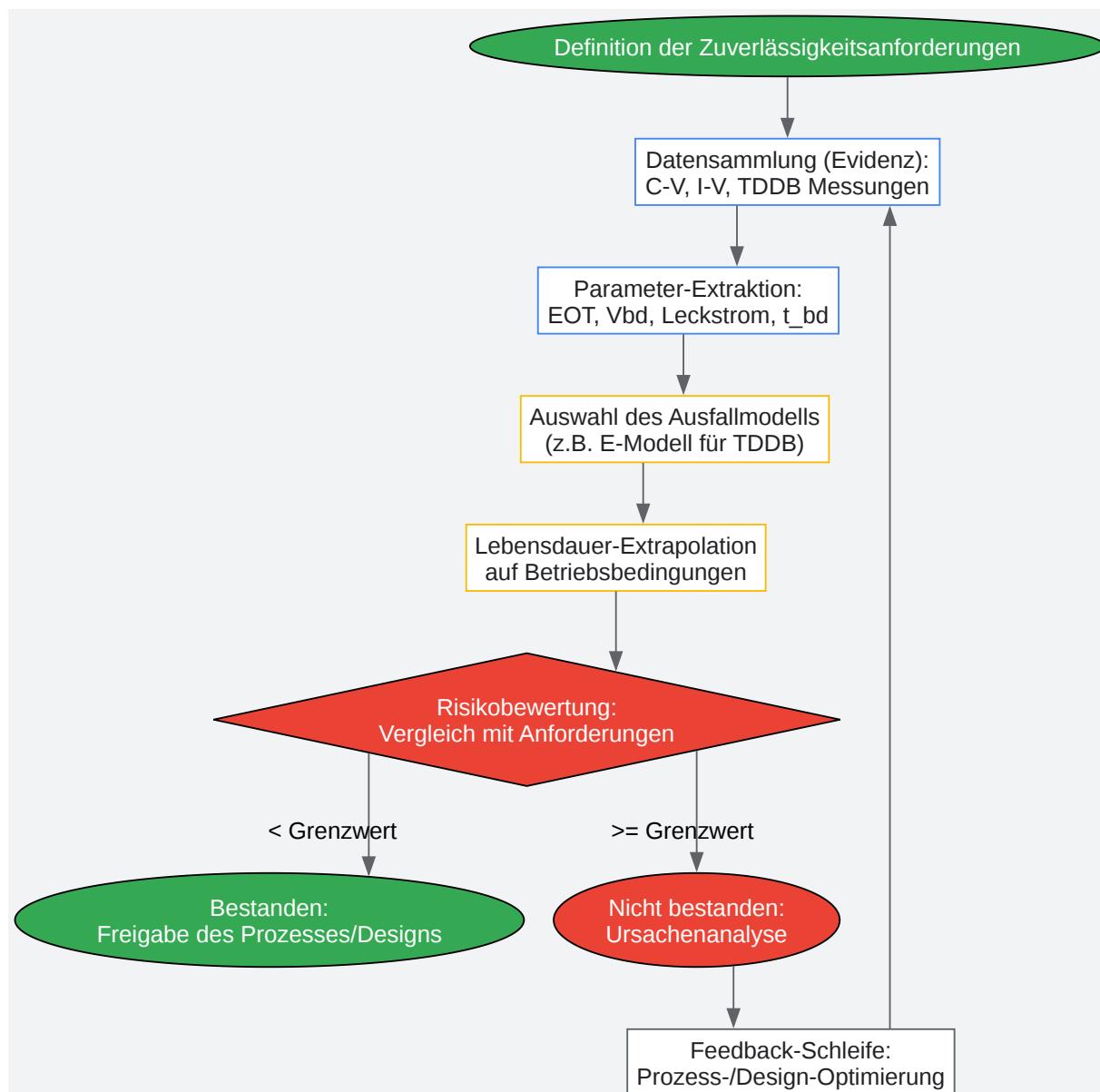

## Visualisierung von Arbeitsabläufen und logischen Beziehungen

Diagramme sind unerlässlich, um komplexe Arbeitsabläufe und Entscheidungsprozesse zu visualisieren.

[Click to download full resolution via product page](#)

Abbildung 1: Experimenteller Arbeitsablauf für die Charakterisierung von Gate-Dielektrika.

[Click to download full resolution via product page](#)

Abbildung 2: Logischer Fluss für die evidenzbasierte Bewertung der Zuverlässigkeit.

## Schlussfolgerung

Ein strukturierter, evidenzbasierter Rahmen für die Bewertung der Zuverlässigkeit von Gate-Dielektrika ist für die Entwicklung moderner Halbleitertechnologien von entscheidender Bedeutung. Durch die konsequente Anwendung standardisierter experimenteller Protokolle, die sorgfältige Sammlung und Analyse quantitativer Daten und die Verwendung validierter Ausfallmodelle können fundierte Entscheidungen über die Prozessqualifizierung und die Designrobustheit getroffen werden. Dieser Ansatz ermöglicht nicht nur die Vorhersage der Produktlebensdauer, sondern schafft auch eine Wissensbasis für kontinuierliche Verbesserungen und die Entwicklung zukünftiger, noch zuverlässigerer mikroelektronischer Bauelemente.

### Need Custom Synthesis?

BenchChem offers custom synthesis for rare earth carbides and specific isotopic labeling.

Email: [info@benchchem.com](mailto:info@benchchem.com) or [Request Quote Online](#).

## References

- 1. Time-dependent gate oxide breakdown - Wikipedia [en.wikipedia.org]

- 2. semitracks.com [semitracks.com]

- 3. pubs.aip.org [pubs.aip.org]

- 4. Gate dielectric reliability and instability in GaN metal-insulator-semiconductor high-electron-mobility transistors for power electronics | Journal of Materials Research | Cambridge Core [cambridge.org]

- 5. ttu-ir.tdl.org [ttu-ir.tdl.org]

- 6. tek.com [tek.com]

- To cite this document: BenchChem. [Kernanliegen der Zuverlässigkeit und Ausfallmechanismen]. BenchChem, [2025]. [Online PDF]. Available at: [<https://www.benchchem.com/product/b6360028#bemas-for-gate-dielectrics-in-microelectronics>]

---

### Disclaimer & Data Validity:

The information provided in this document is for Research Use Only (RUO) and is strictly not intended for diagnostic or therapeutic procedures. While BenchChem strives to provide accurate protocols, we make no warranties, express or implied, regarding the fitness of this product for every specific experimental setup.

**Technical Support:** The protocols provided are for reference purposes. Unsure if this reagent suits your experiment? [[Contact our Ph.D. Support Team for a compatibility check](#)]

**Need Industrial/Bulk Grade?** [Request Custom Synthesis Quote](#)

## BenchChem

Our mission is to be the trusted global source of essential and advanced chemicals, empowering scientists and researchers to drive progress in science and industry.

### Contact

Address: 3281 E Guasti Rd

Ontario, CA 91761, United States

Phone: (601) 213-4426

Email: [info@benchchem.com](mailto:info@benchchem.com)