# Indium Phosphide (InP) Wafer Manufacturing: Technical Support Center

Author: BenchChem Technical Support Team. Date: December 2025

| Compound of Interest |         |           |  |  |

|----------------------|---------|-----------|--|--|

| Compound Name:       | Indium  |           |  |  |

| Cat. No.:            | B141171 | Get Quote |  |  |

This technical support center provides troubleshooting guidance and frequently asked questions (FAQs) to assist researchers, scientists, and drug development professionals in overcoming common challenges encountered during **indium** phosphide (InP) wafer manufacturing and experimentation.

### **Troubleshooting Guides**

This section provides solutions to specific problems that may arise during InP wafer manufacturing processes.

Question: What are the primary causes of crystal twinning during InP single crystal growth?

Answer: Crystal twinning is a common defect during the growth of InP single crystals, particularly when using methods like the Vertical Gradient Freeze (VGF) and Vertical Bridgman (VB). The primary causes include:

- Improper Seed Crystal Orientation: Twinning is more likely to occur if the seed crystal is not perfectly oriented. A <111> growth orientation has been used to prevent twinning, but this is not ideal for producing (100) substrates.

- Thermal Stress: High thermal gradients in the crystal growth furnace can induce stress, leading to the formation of twins. The VGF and VB methods are preferred for achieving low dislocation densities because they allow for smaller axial temperature gradients (5-20 °C/cm) near the solid-liquid interface.[1]

### Troubleshooting & Optimization

• Constitutional Supercooling: Non-uniform distribution of dopants in the melt can lead to constitutional supercooling at the growth interface, which can initiate twinning.

### **Troubleshooting Steps:**

- Verify Seed Crystal Orientation: Ensure the use of a high-quality, accurately oriented <100> seed crystal.

- Optimize Thermal Gradient: Adjust the furnace temperature profile to minimize thermal stress on the growing crystal. A lower temperature gradient is generally preferable.

- Control Dopant Concentration: Ensure uniform mixing of dopants in the InP melt to prevent segregation and constitutional supercooling.

Question: My polished InP wafers exhibit high surface roughness. What are the likely causes and how can I improve the surface finish?

Answer: Achieving a low surface roughness (typically <0.5 nm) is critical for subsequent epitaxial growth and device performance.[2] High surface roughness after polishing can be attributed to several factors:

- Inappropriate Polishing Slurry: The choice of polishing slurry is crucial. Some slurries can be overly aggressive or lead to the formation of residues. For instance, H3PO4-H2O2-SiO2based slurries can form silica gel on the wafer surface that is difficult to remove.[2]

- Incorrect Polishing Pad: The combination of slurry and polishing pad affects the material removal rate and final surface quality.

- Subsurface Damage: Damage from preceding steps like sawing and grinding can manifest as surface roughness if not completely removed during polishing.[2]

- Contamination: Particles from the polishing slurry, pad debris, or the cleaning process can cause micro-scratches.[3]

**Troubleshooting Steps:**

### Troubleshooting & Optimization

- Select an Appropriate Slurry: Consider using a Chemical Mechanical Polishing (CMP) slurry specifically designed for InP that minimizes phosphine gas formation and achieves a damage-free, low-roughness surface.[4]

- Optimize Polishing Parameters: Adjust parameters such as polishing pressure, platen speed, and slurry flow rate to achieve the desired removal rate without introducing excessive mechanical stress.

- Ensure Proper Pre-polishing Steps: Thoroughly remove subsurface damage from grinding and lapping before the final polishing step.

- Implement a Robust Cleaning Process: Follow polishing with a multi-stage cleaning process to remove all slurry residues and particulate contamination.

Question: I am observing a high density of threading dislocations in my epitaxially grown InP layers. What strategies can be employed to reduce these defects?

Answer: Threading dislocations are detrimental to device performance. A high density of these defects often originates from the lattice mismatch between the InP epitaxial layer and the substrate (e.g., when growing on GaAs or Si). Several techniques can be used to mitigate this issue:

- Graded Buffer Layers: The use of a compositionally graded buffer layer, such as InGaAs, can help to gradually accommodate the lattice mismatch, thereby reducing the formation of threading dislocations.

- Strained-Layer Superlattices (SLSs): Inserting SLSs, for example InAsP/InP or InGaAs/InP,

can effectively filter dislocations by bending them towards the edges of the wafer.

- Two-Step Growth Process: A common method involves growing an initial InP layer at a low temperature followed by a second layer at a higher temperature. This can improve the crystal quality.

- Thermal Annealing: Post-growth annealing can also help to reduce the dislocation density.

Combining these methods, such as using a graded buffer with a two-step growth process and post-annealing, has been shown to significantly reduce the threading dislocation density. For

instance, a two-step InP growth on a thin InGaAs linearly graded buffer has been shown to reduce the threading dislocation density to  $2.3 \times 10^8$  cm<sup>-2</sup>.[5]

## Frequently Asked Questions (FAQs)

What are the primary challenges in InP wafer manufacturing?

The manufacturing of InP wafers presents several significant challenges:

- Crystal Growth: InP has a low melting point and high phosphorus vapor pressure, making single crystal growth complex.

- Mechanical Fragility: InP wafers are brittle and prone to cracking during handling, cutting, and polishing.

- Toxicity: The precursors used in InP synthesis and epitaxy, such as phosphine (PH₃), are highly toxic.

- Lattice Matching: Achieving precise lattice matching during the epitaxial growth of heterostructures is critical to avoid strain and defects.

- Thermal Conductivity: InP has lower thermal conductivity compared to silicon, which can be a challenge for heat dissipation in high-power devices.

- Cost: The raw materials for InP are relatively expensive, contributing to the higher cost of InP wafers compared to silicon.

What are the common methods for growing InP single crystals?

The most common methods for growing InP single crystals are:

- Liquid Encapsulated Czochralski (LEC): This is a widely used method for producing largediameter InP crystals. However, it can result in higher dislocation densities due to thermal stress.

- Vertical Gradient Freeze (VGF): The VGF method generally produces crystals with lower dislocation densities due to a smaller thermal gradient.

- Vertical Bridgman (VB): Similar to VGF, the VB method is known for producing high-quality crystals with low defect densities.

- Horizontal Gradient Freeze (HGF): This method is also used for InP crystal growth.

What are typical dislocation densities in InP wafers?

Dislocation density, often measured as Etch Pit Density (EPD), is a critical quality metric for InP wafers. Typical values vary depending on the growth method and dopant:

| Growth Method | Dopant            | Typical EPD (cm <sup>-2</sup> ) |

|---------------|-------------------|---------------------------------|

| VGF           | Undoped           | < 500                           |

| PC-LEC        | Fe-doped (3-inch) | < 500                           |

| PC-LEC        | Fe-doped (4-inch) | < 5 x 10 <sup>3</sup>           |

| VGF-VB        | -                 | ≤ 300 at the tail               |

Data compiled from multiple sources.[7][8][9]

What is the expected surface roughness of a high-quality InP wafer?

For applications requiring epitaxial growth, the surface roughness of the InP wafer is a critical parameter. The generally accepted specification for surface roughness (Ra) is less than 0.5 nm.[2][10]

# **Quantitative Data Summary**

Table 1: Thermal Properties of Indium Phosphide

| Property                        | Value                   | Unit                                |

|---------------------------------|-------------------------|-------------------------------------|

| Melting Point                   | 1060                    | °C                                  |

| Thermal Conductivity (at 300 K) | 0.68                    | W cm <sup>-1</sup> °C <sup>-1</sup> |

| Thermal Expansion Coefficient   | 4.60 x 10 <sup>-6</sup> | °C-1                                |

| Bulk Modulus                    | 7.1 x 10 <sup>11</sup>  | dyn cm <sup>-2</sup>                |

Data compiled from multiple sources.[11][12][13]

Table 2: Typical InP Wafer Polishing and Thinning Parameters

| Process Step      | Initial Thickness<br>(µm) | Final Thickness<br>(µm) | Polishing Rate<br>(µm/min) |

|-------------------|---------------------------|-------------------------|----------------------------|

| Physical Grinding | 300 - 500                 | 180 - 240               | -                          |

| Rough Polishing   | -                         | -                       | 0.10 - 0.15                |

| Fine Polishing    | -                         | -                       | 0.3 - 0.6                  |

Data compiled from multiple sources.[2][14]

# **Experimental Protocols**

Protocol 1: Standard InP Wafer Cleaning (RCA Clean)

This protocol is a widely used method for removing organic and inorganic contaminants from wafer surfaces.

#### Materials:

- Deionized (DI) water

- Ammonium hydroxide (NH<sub>4</sub>OH)

- Hydrogen peroxide (H<sub>2</sub>O<sub>2</sub>)

- Hydrochloric acid (HCl)

- Wafer carrier (e.g., PEEK)

- Heated quartz baths

- Quick Dump Rinser (QDR)

- Spin Rinse Dryer (SRD)

#### Procedure:

- SC-1 (Standard Clean 1) Organic Removal: a. Prepare a fresh solution of DI water, NH<sub>4</sub>OH, and H<sub>2</sub>O<sub>2</sub> in a 6:1:1 ratio in a heated quartz bath.[15] b. Heat the solution to 70°C. [15] c. Immerse the InP wafers in the SC-1 solution for 10 minutes.[15] d. Rinse the wafers thoroughly in a QDR with DI water.

- SC-2 (Standard Clean 2) Metallic Ion Removal: a. Prepare a fresh solution of DI water, HCl, and H<sub>2</sub>O<sub>2</sub> in a 6:1:1 ratio in a separate heated quartz bath.[15] b. Heat the solution to 70°C.

[15] c. Immerse the wafers in the SC-2 solution for 10 minutes.[15] d. Rinse the wafers thoroughly in a QDR with DI water.

- Drying: a. Transfer the wafer carrier to an SRD. b. Start the spin rinse and dry cycle.

Safety Precautions: Always wear appropriate personal protective equipment (PPE), including chemical-resistant gloves, apron, and face shield, when handling the chemicals used in this procedure. Perform all steps in a certified fume hood.

Protocol 2: Wet Etching of InP for Defect Analysis

This protocol describes a method for wet etching InP to reveal crystal defects such as dislocations.

#### Materials:

- Hydrobromic acid (HBr)

- Hydrochloric acid (HCl)

- Hydrogen peroxide (H<sub>2</sub>O<sub>2</sub>)

- Deionized (DI) water

- Glass beakers (Pyrex)

- Magnetic stirrer or glass stirring rod

- Profilometer or microscope for analysis

#### Procedure:

- Etchant Preparation: a. In a fume hood, pour 50 parts of DI water into a Pyrex beaker. b. Add 10 parts of HBr, 5 parts of HCl, and finally 1 part of H<sub>2</sub>O<sub>2</sub> in order of decreasing volume.[16] c. Stir the mixture thoroughly. d. Continue mixing until the solution turns pale yellow.[16] e. Cover the beaker and let it age for 30 minutes to allow for the formation of Br<sub>2</sub>.[16]

- Etching: a. Maintain the etchant temperature at approximately 25°C.[16] b. Carefully immerse the InP sample into the aged solution. c. Gently agitate the beaker to ensure uniform etching. d. The etch rate is sensitive to the HBr and H<sub>2</sub>O<sub>2</sub> concentrations. It is recommended to first etch a dummy wafer to determine the etch rate. e. Etch for the calculated time to achieve the desired depth.

- Post-Etch Processing: a. Immediately remove the wafer from the etchant and rinse it

thoroughly in a QDR with DI water.[16] b. Dry the sample using a spin dryer or nitrogen gun.

c. Inspect the etched surface under a microscope or use a profilometer to analyze the

revealed defects.

Safety Precautions: HBr, HCl, and  $H_2O_2$  are corrosive and should be handled with extreme care in a fume hood with appropriate PPE.

### **Visualizations**

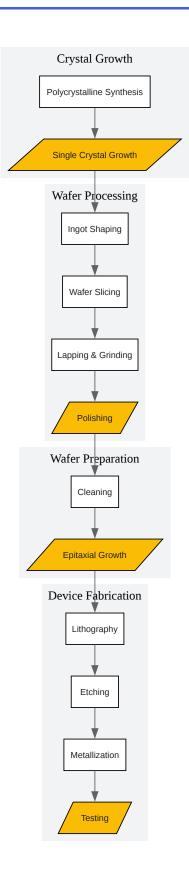

Click to download full resolution via product page

Caption: Overview of the InP wafer manufacturing workflow.

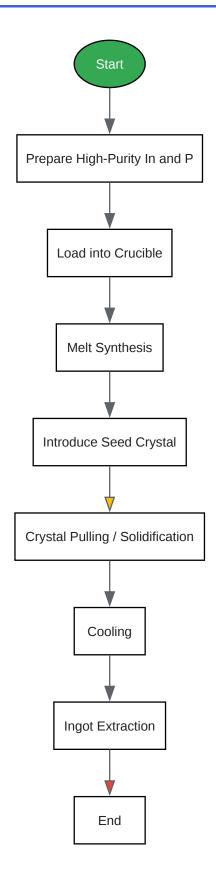

Click to download full resolution via product page

Caption: Simplified InP single crystal growth process flow.

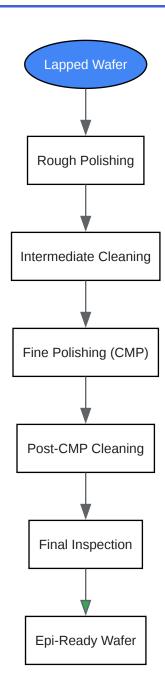

Click to download full resolution via product page

Caption: Workflow for InP wafer polishing and cleaning.

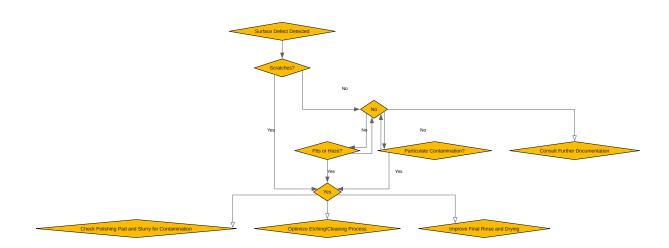

Click to download full resolution via product page

Caption: Troubleshooting logic for common InP surface defects.

### **Need Custom Synthesis?**

BenchChem offers custom synthesis for rare earth carbides and specific isotopiclabeling.

Email: info@benchchem.com or Request Quote Online.

## References

### Troubleshooting & Optimization

- 1. csmantech.org [csmantech.org]

- 2. Indium Phosphide Chip Polishing Slurry [grish.com]

- 3. researchgate.net [researchgate.net]

- 4. engis.com [engis.com]

- 5. mdpi.com [mdpi.com]

- 6. Properties of InP Wafers | Wafer World [waferworld.com]

- 7. powerwaywafer.com [powerwaywafer.com]

- 8. researchgate.net [researchgate.net]

- 9. wiki.nanofab.ucsb.edu [wiki.nanofab.ucsb.edu]

- 10. INDIUM PHOSPHIDE WAFER HAVING PITS ON THE BACK SIDE, METHOD AND ETCHING SOLUTION FOR MANUFACTURING THE SAME | TREA [trea.com]

- 11. Thermal properties of Indium Phosphide (InP) [ioffe.ru]

- 12. everythingrf.com [everythingrf.com]

- 13. azom.com [azom.com]

- 14. CN106346318A InP (indium phosphide) wafer thinning and polishing method and chemical corrosion device Google Patents [patents.google.com]

- 15. louisville.edu [louisville.edu]

- 16. louisville.edu [louisville.edu]

- To cite this document: BenchChem. [Indium Phosphide (InP) Wafer Manufacturing: Technical Support Center]. BenchChem, [2025]. [Online PDF]. Available at: [https://www.benchchem.com/product/b141171#overcoming-challenges-in-indium-phosphide-wafer-manufacturing]

### **Disclaimer & Data Validity:**

The information provided in this document is for Research Use Only (RUO) and is strictly not intended for diagnostic or therapeutic procedures. While BenchChem strives to provide accurate protocols, we make no warranties, express or implied, regarding the fitness of this product for every specific experimental setup.

**Technical Support:**The protocols provided are for reference purposes. Unsure if this reagent suits your experiment? [Contact our Ph.D. Support Team for a compatibility check]

### Need Industrial/Bulk Grade? Request Custom Synthesis Quote

# BenchChem

Our mission is to be the trusted global source of essential and advanced chemicals, empowering scientists and researchers to drive progress in science and industry. Contact

Address: 3281 E Guasti Rd

Ontario, CA 91761, United States

Phone: (601) 213-4426

Email: info@benchchem.com