# Gating Techniques for Tuning Carrier Density in WT<sub>2</sub>: Application Notes and Protocols

Author: BenchChem Technical Support Team. Date: December 2025

For Researchers, Scientists, and Drug Development Professionals

This document provides detailed application notes and protocols for tuning the carrier density in the transition metal dichalcogenide Tungsten Ditelluride (WTe<sub>2</sub>). The ability to precisely control carrier concentration is crucial for investigating its unique electronic properties, including its large non-saturating magnetoresistance and potential as a type-II Weyl semimetal.[1][2] The following sections detail various gating methodologies, present key quantitative data in a comparative format, and provide standardized experimental protocols.

## **Overview of Gating Techniques**

Electrostatic gating is a powerful, non-invasive technique to modulate the carrier density in WTe<sub>2</sub> thin flakes. By applying a voltage to a nearby gate electrode, an electric field is generated that penetrates the WTe<sub>2</sub> channel, accumulating or depleting charge carriers (electrons and holes). This allows for the continuous tuning of the Fermi level and, consequently, the carrier concentration. Several gating configurations are commonly employed, each with distinct advantages and capabilities.

Three primary methods for gating WTe2 are:

Solid-State Back Gating: The most straightforward method, utilizing the silicon substrate as a global back gate.

- Ionic Liquid Gating: Employs an ionic liquid as the gate dielectric, enabling extremely high carrier density modulation due to the formation of an electric double layer.[3][4]

- Dual Gating: A more advanced configuration with both top and bottom gates, offering independent control over carrier density and displacement field.[5]

## **Comparative Data of Gating Techniques**

The choice of gating technique significantly impacts the achievable carrier density range and other electronic properties of WTe<sub>2</sub>. The following table summarizes key quantitative parameters from literature for different gating methods.

| Gating<br>Technique        | Gate Dielectric              | Achievable<br>Carrier Density<br>(cm <sup>-2</sup> ) | Typical Gate<br>Voltage Range | Key Features<br>& Benefits                                                                     |

|----------------------------|------------------------------|------------------------------------------------------|-------------------------------|------------------------------------------------------------------------------------------------|

| Solid-State Back<br>Gating | SiO2/Si                      | ~10 <sup>13</sup>                                    | ±80 V                         | Simple fabrication; compatible with standard lithography.                                      |

| Ionic Liquid<br>Gating     | Various Ionic<br>Liquids     | > 1014                                               | ±3 to ±4 V                    | High capacitance; enables access to exotic electronic phases.[3][6]                            |

| Dual Gating                | h-BN (top), SiO₂<br>(bottom) | ~10 <sup>13</sup> (top gate)                         | Varies                        | Independent control of carrier density and displacement field; improved device performance.[5] |

Note: The achievable carrier density can vary depending on the thickness of the WTe<sub>2</sub> flake and the quality of the gate dielectric.

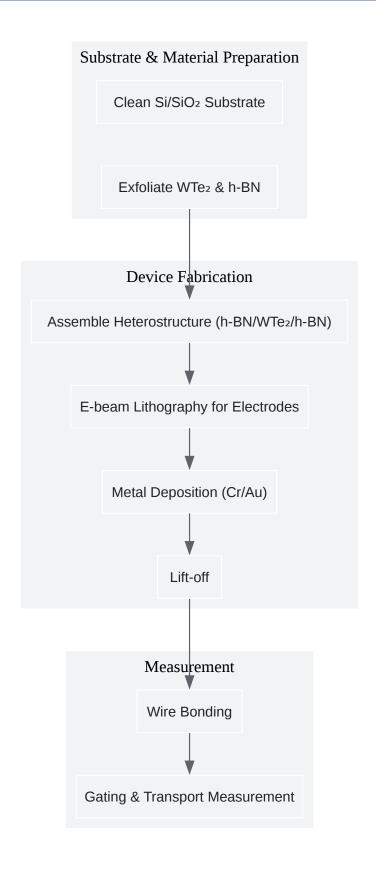

# Experimental Protocols Device Fabrication (General Protocol)

The fabrication of WTe<sub>2</sub> field-effect transistor (FET) devices is a multi-step process requiring a cleanroom environment. The following protocol outlines the general steps for creating a device suitable for gating experiments.

#### Materials and Equipment:

- WTe<sub>2</sub> bulk crystals

- Si/SiO<sub>2</sub> substrates (with a thermally grown oxide layer, typically 285-300 nm)

- Hexagonal boron nitride (h-BN) crystals (for encapsulation)

- Polydimethylsiloxane (PDMS) stamps

- Optical microscope

- Mechanical exfoliator (e.g., scotch tape)

- Electron beam lithography (EBL) system

- Metal evaporator (for depositing contacts, e.g., Cr/Au)

- · Lift-off solution (e.g., acetone)

- Inert atmosphere glovebox

#### Protocol:

- Substrate Preparation: Clean the Si/SiO<sub>2</sub> substrate using a standard cleaning procedure (e.g., sonication in acetone and isopropanol).

- Exfoliation of WTe2 and h-BN:

- Mechanically exfoliate thin flakes of WTe2 and h-BN from their bulk crystals onto separate

PDMS stamps using scotch tape.[7]

- Identify suitable thin flakes (monolayer to few-layers) using an optical microscope based on their color contrast.

- Heterostructure Assembly (for encapsulated devices):

- In an inert atmosphere, transfer a thin flake of h-BN onto the Si/SiO<sub>2</sub> substrate.

- Align and transfer the WTe<sub>2</sub> flake on top of the bottom h-BN.

- Transfer a second h-BN flake on top of the WTe2 to fully encapsulate it. This encapsulation protects the WTe2 from degradation in ambient conditions.[8]

- Electrode Patterning:

- Spin-coat a layer of electron beam resist (e.g., PMMA) onto the substrate.

- Use EBL to define the electrode pattern (e.g., Hall bar geometry).

- Metal Deposition:

- Develop the resist to create openings for the metal contacts.

- Immediately transfer the sample to a metal evaporator and deposit contact metals (e.g., 5 nm Cr followed by 50 nm Au).

- Lift-off:

- Immerse the sample in a lift-off solution (e.g., acetone) to remove the excess metal and resist, leaving behind the patterned electrodes.

- Annealing (Optional): Anneal the device in a vacuum or inert atmosphere to improve contact quality.

## **Gating Measurement Protocols**

### Methodological & Application

This is the most common configuration where the doped silicon substrate acts as the back gate and the SiO<sub>2</sub> layer as the gate dielectric.

#### Procedure:

- Mount the fabricated WTe<sub>2</sub> device in a cryostat for low-temperature measurements.

- Wire bond the source, drain, and gate contacts of the device to the measurement setup.

- Apply a DC voltage (V\_sd) across the source and drain electrodes and measure the resulting current (I\_sd) to determine the channel resistance.

- Sweep the back-gate voltage (V\_bg) and record the change in channel resistance or conductivity.

- To determine the carrier density, perform Hall measurements by applying a perpendicular magnetic field and measuring the Hall voltage as a function of the back-gate voltage.

Ionic liquid gating allows for much higher carrier densities due to the formation of an electric double layer at the WTe<sub>2</sub>/ionic liquid interface.

#### Materials:

- Fabricated WTe2 device

- Ionic liquid (e.g., DEME-TFSI)

- Gate electrode (e.g., a small piece of metal wire)

- Vacuum probe station or cryostat

#### Protocol:

- Place the WTe<sub>2</sub> device in a vacuum chamber.

- Carefully drop a small amount of ionic liquid onto the device, ensuring it covers the channel and a gate electrode placed nearby.

- Slowly pump down the chamber to remove any absorbed water from the ionic liquid.

- Apply a gate voltage between the gate electrode and the source contact of the WTe2 device.

- Sweep the gate voltage slowly (typically a few mV/s) to allow for the formation of the electric double layer and to avoid electrochemical reactions.

- Perform transport measurements (resistance, Hall effect) at each gate voltage step.

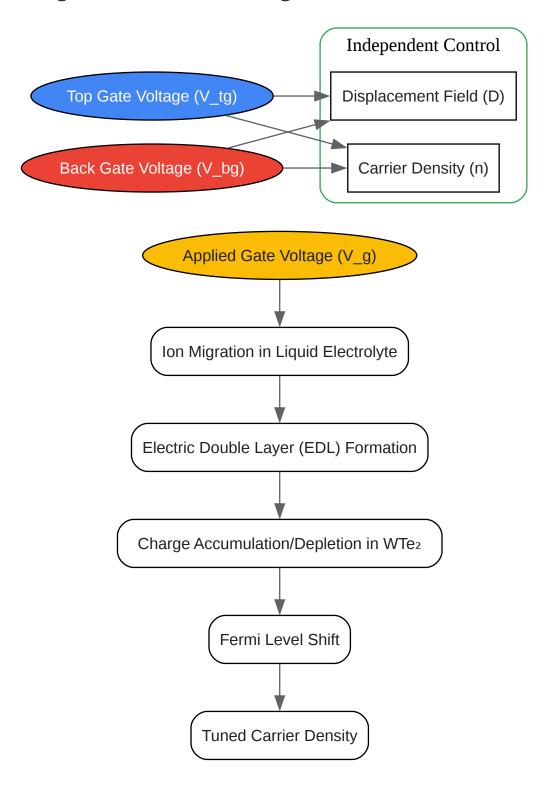

This technique provides independent control over the carrier density and the perpendicular electric field.

#### Procedure:

- Fabricate a WTe<sub>2</sub> device with both a top gate and a back gate. The top gate is typically a metal electrode deposited on top of a thin h-BN dielectric layer.

- Wire bond all the contacts: source, drain, back gate, and top gate.

- The carrier density can be tuned by varying both the top gate voltage (V\_tg) and the back gate voltage (V\_bg). The total induced charge density is a linear combination of the two gate voltages.

- The perpendicular displacement field can be controlled by varying V\_tg and V\_bg in opposite directions while keeping the carrier density constant.

- Perform systematic transport measurements by sweeping both gate voltages independently or in combination.

# Visualizations

## **Experimental Workflow for Device Fabrication**

Click to download full resolution via product page

Caption: Workflow for WTe2 device fabrication and measurement.

## **Logic Diagram of Dual Gating**

Click to download full resolution via product page

#### **Need Custom Synthesis?**

BenchChem offers custom synthesis for rare earth carbides and specific isotopiclabeling.

Email: info@benchchem.com or Request Quote Online.

### References

- 1. Tuning the magnetoresistance of ultrathin WTe2 sheets by electrostatic gating Nanoscale (RSC Publishing) [pubs.rsc.org]

- 2. arxiv.org [arxiv.org]

- 3. Ionic-Liquid Gating in Two-Dimensional TMDs: The Operation Principles and Spectroscopic Capabilities PMC [pmc.ncbi.nlm.nih.gov]

- 4. research.rug.nl [research.rug.nl]

- 5. arxiv.org [arxiv.org]

- 6. Lithium-ion-based solid electrolyte tuning of the carrier density in graphene PMC [pmc.ncbi.nlm.nih.gov]

- 7. arxiv.org [arxiv.org]

- 8. arxiv.org [arxiv.org]

- To cite this document: BenchChem. [Gating Techniques for Tuning Carrier Density in WT<sub>2</sub>:

Application Notes and Protocols]. BenchChem, [2025]. [Online PDF]. Available at:

[https://www.benchchem.com/product/b082480#gating-techniques-for-tuning-carrier-density-in-wte2]

#### **Disclaimer & Data Validity:**

The information provided in this document is for Research Use Only (RUO) and is strictly not intended for diagnostic or therapeutic procedures. While BenchChem strives to provide accurate protocols, we make no warranties, express or implied, regarding the fitness of this product for every specific experimental setup.

**Technical Support:**The protocols provided are for reference purposes. Unsure if this reagent suits your experiment? [Contact our Ph.D. Support Team for a compatibility check]

Need Industrial/Bulk Grade? Request Custom Synthesis Quote

# BenchChem

Our mission is to be the trusted global source of essential and advanced chemicals, empowering scientists and researchers to drive progress in science and industry. Contact

Address: 3281 E Guasti Rd

Ontario, CA 91761, United States

Phone: (601) 213-4426

Email: info@benchchem.com