## Gate degradation mechanisms in GaN HEMTs under stress.

Author: BenchChem Technical Support Team. Date: December 2025

# GaN HEMT Gate Degradation: Technical Support Center

This technical support center provides researchers and scientists with troubleshooting guides and frequently asked questions (FAQs) regarding gate degradation mechanisms in **Gallium Nitride** (GaN) High Electron Mobility Transistors (HEMTs) under electrical and thermal stress.

### Frequently Asked Questions (FAQs)

Q1: What are the primary mechanisms responsible for gate degradation in GaN HEMTs?

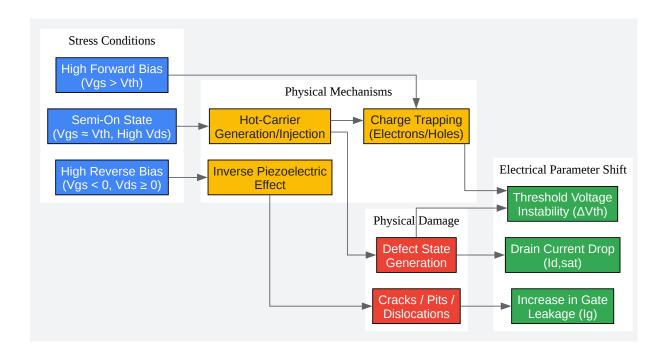

A1: Gate degradation in GaN HEMTs is a complex process driven by several mechanisms, often acting in concert. The primary drivers include:

- Inverse Piezoelectric Effect: High electric fields, particularly under reverse bias, induce mechanical stress in the AlGaN barrier layer. This stress can lead to the formation of crystallographic defects, such as cracks and dislocations, creating leakage paths.[1][2][3]

- Hot-Carrier Effects: Electrons accelerated by high electric fields in the channel (so-called "hot electrons") can gain enough energy to be injected into the barrier layer or generate defects.[2][4][5][6] This is particularly prevalent in the "semi-on" state.[4][6]

- Trapping Effects: Charge carriers (electrons or holes) can become trapped in pre-existing or newly generated defects within the gate stack (e.g., in the p-GaN layer, AlGaN barrier, or

#### Troubleshooting & Optimization

dielectric interfaces).[2][7][8] This trapping alters the device's electrostatics, leading to threshold voltage instability.

Time-Dependent Dielectric Breakdown (TDDB): For MIS-HEMTs, the gate dielectric can degrade over time under high electric field stress, leading to a sudden and permanent failure of the gate.[9][10][11][12]

Q2: How does stress polarity (forward vs. reverse bias) affect gate degradation?

A2: The polarity of the gate stress significantly influences the degradation mechanism:

- Reverse Bias Stress (Vgs < 0): This condition creates a high electric field at the drain-side edge of the gate. The dominant degradation mechanism is often the inverse piezoelectric effect, leading to a sudden, irreversible increase in gate leakage current once a critical voltage is surpassed.[1][2]

- Forward Bias Stress (Vgs > 0): In p-GaN gate HEMTs, forward bias can lead to both electron and hole trapping.[7][13] At low forward bias, electron trapping may cause a positive threshold voltage (Vth) shift.[7][13] At higher forward bias, hole trapping can dominate, causing a negative Vth shift.[7][13][14]

Q3: What is "Threshold Voltage Instability" and what causes it?

A3: Threshold voltage (Vth) instability refers to the shift in the gate voltage required to turn the transistor on after a period of stress. It is primarily caused by charge trapping in various locations within the device structure.

- A positive Vth shift is generally attributed to electron trapping in the AlGaN barrier, p-GaN layer, or underlying buffer layers.[4][7][13]

- A negative Vth shift is often caused by the trapping of holes, which can be generated by impact ionization in high-field regions.[7][14][15]

Q4: What is the role of temperature in gate degradation?

A4: Temperature acts as an accelerating factor for many degradation mechanisms. High temperatures can:

- Promote the generation of defects.[15]

- Facilitate the diffusion of metal from the gate contact into the semiconductor.

- Increase the probability of carriers overcoming energy barriers, enhancing trapping/detrapping phenomena.[13]

- Accelerate Time-Dependent Dielectric Breakdown (TDDB) in MIS-HEMTs.[10]

## **Troubleshooting Guides**

This section addresses common issues observed during GaN HEMT stress experiments.

## Troubleshooting & Optimization

Check Availability & Pricing

| Observed Issue                                                        | Potential Cause(s)                                                                                                                                              | Troubleshooting / Next Steps                                                                                                                                                                                                                                               |  |

|-----------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Sudden, large, and irreversible increase in gate leakage current (Ig) | Inverse Piezoelectric Effect: A critical voltage has likely been exceeded, causing physical defect formation in the AlGaN barrier.[1][16]                       | 1. Confirm the critical voltage by performing a step-stress experiment. 2. Use physical failure analysis techniques like TEM or photon emission microscopy to identify defects.  [17] 3. Consider device designs with field plates to reduce the peak electric field.  [2] |  |

| Gradual increase in gate<br>leakage current (Ig)                      | Defect-Assisted Tunneling: Stress may be generating new defects that assist carrier tunneling through the Schottky barrier.[18]                                 | 1. Perform temperature- dependent I-V measurements to analyze the leakage mechanism (e.g., Poole- Frenkel emission).[3] 2. Conduct constant voltage stress tests to monitor the time-evolution of the leakage.                                                             |  |

| Threshold voltage (Vth) shifts positive after stress                  | Electron Trapping: Hot electrons or electrons injected from the gate are being trapped in the gate stack (e.g., AlGaN barrier, p-GaN, or dielectric).[4][7][13] | 1. Perform stress-and-recovery experiments to determine if the trapping is reversible. 2. Use pulsed I-V measurements to characterize the time constants of the trapping effects.[4]                                                                                       |  |

| Threshold voltage (Vth) shifts negative after stress                  | Hole Trapping: Holes generated by impact ionization may be trapped in the gate region.[7][14][15] This is common in p-GaN HEMTs under high forward gate bias.   | 1. Correlate the Vth shift with gate current measurements; an increase in gate current can indicate hole injection.[7] 2. Investigate the effect of temperature, as de-trapping rates are thermally activated.                                                             |  |

| Drain current (Id) decreases,<br>and On-resistance (Ron)<br>increases | Hot-Carrier Induced Trapping: Hot electrons generated during stress can be trapped, depleting the 2DEG channel. [4][5] Surface Pitting: High- temperature stress can cause physical damage to the semiconductor surface.[19][20]    | 1. Use pulsed I-V measurements (gate and drain lag) to probe for trapping effects.[4][21] 2. For suspected physical damage, perform post-stress failure analysis (e.g., SEM, AFM).                                           |

|-----------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Catastrophic gate failure (short circuit)                             | Time-Dependent Dielectric Breakdown (TDDB): In MIS- HEMTs, the gate insulator has broken down.[9][10] Electromigration/Contact Degradation: At high temperatures, metal from the gate contact may have migrated, shorting the gate. | For TDDB, perform constant voltage stress tests on multiple devices to obtain Weibull statistics and estimate lifetime.  [11] 2. Analyze the failed device with microscopy to check for gate metal deformation or diffusion. |

### **Quantitative Data Summary**

The following tables summarize typical degradation behaviors reported in the literature under different stress conditions.

Table 1: Threshold Voltage (Vth) Shift Under Gate Stress

| Device Type           | Stress<br>Condition       | Stress<br>Duration | Vth Shift<br>(ΔVth)                   | Probable<br>Mechanism              | Reference |

|-----------------------|---------------------------|--------------------|---------------------------------------|------------------------------------|-----------|

| p-GaN HEMT            | Vg = 2-6 V                | 4000 s             | Positive,<br>increases<br>with Vg     | Electron<br>Trapping               | [7]       |

| p-GaN HEMT            | Vg = 7-9.5 V              | 4000 s             | Positive, but<br>decreases<br>with Vg | Competing Electron & Hole Trapping | [7]       |

| p-GaN HEMT            | Vg.stress < 2<br>V (RT)   | Step-stress        | Positive                              | Electron<br>Trapping               | [13]      |

| p-GaN HEMT            | Vg.stress > 4<br>V (RT)   | Step-stress        | Negative                              | Hole<br>Trapping                   | [13]      |

| Schottky<br>Gate HEMT | Semi-on state<br>(Vd=40V) | 1000s of sec       | Positive (~0.5<br>V)                  | Hot-Electron<br>Trapping           | [4]       |

Table 2: Gate Leakage Current (Ig) Increase Under Reverse Bias Stress

| Device Type                             | Stress<br>Method                                    | Critical<br>Voltage (Vc) | lg Increase<br>Factor | Probable<br>Mechanism              | Reference |

|-----------------------------------------|-----------------------------------------------------|--------------------------|-----------------------|------------------------------------|-----------|

| AlGaN/GaN<br>HEMT                       | Step-stress<br>(Vgs stepped<br>from -10 to<br>-50V) | Varies with step time    | > 1000x               | Inverse<br>Piezoelectric<br>Effect | [1]       |

| Gated TLM<br>HEMT                       | Step-stress                                         | -10 V to > -60<br>V      | Up to<br>10,000x      | Inverse<br>Piezoelectric<br>Effect | [16]      |

| AlGaN/GaN<br>HEMT (No<br>Field Plate)   | Step-stress<br>(Vgs,<br>Vds=5V)                     | ~ -40 V                  | Sudden<br>increase    | Inverse<br>Piezoelectric<br>Effect | [2]       |

| AlGaN/GaN<br>HEMT (With<br>Field Plate) | Step-stress<br>(Vgs,<br>Vds=5V)                     | ~ -65 V                  | Sudden<br>increase    | Inverse<br>Piezoelectric<br>Effect | [2]       |

### **Experimental Protocols**

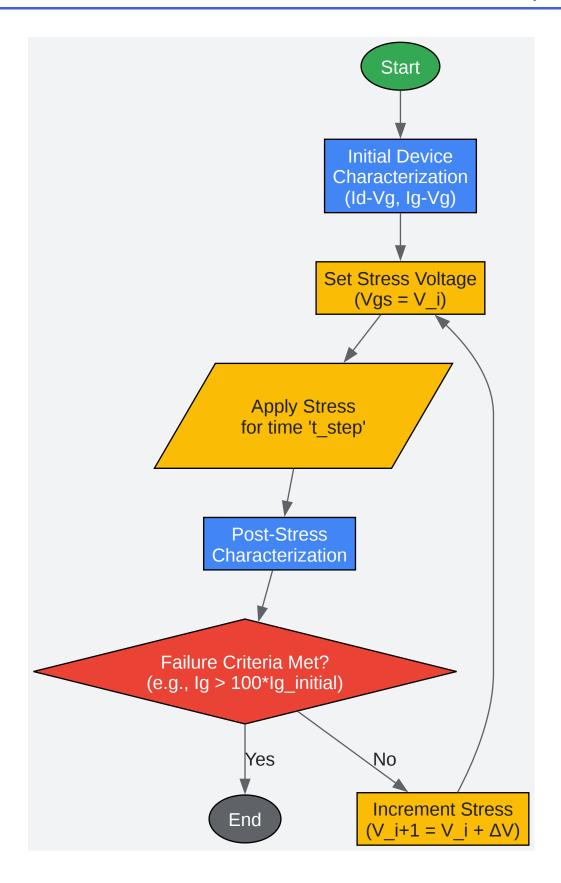

Protocol 1: Step-Stress Test for Determining Critical Voltage

This protocol is used to identify the critical voltage at which sudden, permanent degradation (e.g., due to the inverse piezoelectric effect) occurs.

- Initial Characterization: Perform a full suite of DC I-V measurements (Id-Vg, Id-Vd, Ig-Vg) on the fresh device. Ensure characterization sweeps do not themselves cause degradation.[1]

- Stress Application:

- Set a constant drain voltage (e.g., Vds = 0 V or a low application-relevant voltage).

- Apply a reverse gate voltage (Vgs) starting from a safe level (e.g., -5 V).

- Hold the stress for a fixed duration (the "step time," e.g., 60 seconds).[1]

- Intermediate Characterization: After each stress step, repeat the full DC I-V characterization to monitor changes in Vth, Id, Ron, and Ig.

- Stepping: Increase the magnitude of the reverse gate voltage by a fixed increment (e.g., 1

V).[1]

- Repeat: Repeat steps 2-4 until a predefined failure criterion is met, such as a 100x increase in gate leakage current.

- Analysis: Plot the change in key parameters (e.g., Ig) versus the stress voltage. The voltage at which a sharp, irreversible increase occurs is the critical voltage.

Protocol 2: Constant Voltage Stress (CVS) Test for Vth Instability

This protocol is used to evaluate time-dependent shifts in threshold voltage due to charge trapping.

- Initial Characterization: Measure the initial Id-Vg transfer curve of the device and extract the baseline Vth.

- Stress Application:

- Apply a constant DC gate voltage (Vgs,stress) and drain voltage (Vds,stress). The bias

point should be chosen to target specific mechanisms (e.g., Vds=0V for gate-only stress,

or a semi-on state for hot-carrier stress).

- Maintain this stress for a prolonged period, with periodic interruptions for measurement.

- Measurement Interruption:

- At predefined time intervals (e.g., 1s, 10s, 100s, 1000s), interrupt the stress.

- Quickly sweep the Id-Vg curve to measure the new Vth. Minimize measurement time to avoid recovery effects.

- Resumption of Stress: Re-apply the stress conditions immediately after the measurement.

Analysis: Plot the threshold voltage shift (ΔVth) as a function of stress time. This can reveal the dynamics of charge trapping.[7]

#### **Visualizations**

Click to download full resolution via product page

Caption: Logical flow from stress conditions to degradation mechanisms and observable parameter shifts.

Click to download full resolution via product page

Caption: Experimental workflow for a typical gate step-stress reliability test.

#### **Need Custom Synthesis?**

BenchChem offers custom synthesis for rare earth carbides and specific isotopiclabeling.

Email: info@benchchem.com or Request Quote Online.

#### References

- 1. mtlsites.mit.edu [mtlsites.mit.edu]

- 2. Degradation Mechanisms for GaN and GaAs High Speed Transistors PMC [pmc.ncbi.nlm.nih.gov]

- 3. pubs.aip.org [pubs.aip.org]

- 4. pdfs.semanticscholar.org [pdfs.semanticscholar.org]

- 5. researchgate.net [researchgate.net]

- 6. IEEE Xplore Login [ieeexplore.ieee.org]

- 7. pubs.aip.org [pubs.aip.org]

- 8. Degradation Behavior and Mechanism of GaN HEMTs With P-Type Gate in the Third Quadrant Under Repetitive Surge Current Stress | IEEE Journals & Magazine | IEEE Xplore [ieeexplore.ieee.org]

- 9. [PDF] OFF-state TDDB in high-voltage GaN MIS-HEMTs | Semantic Scholar [semanticscholar.org]

- 10. dspace.mit.edu [dspace.mit.edu]

- 11. cpb.iphy.ac.cn [cpb.iphy.ac.cn]

- 12. mtlsites.mit.edu [mtlsites.mit.edu]

- 13. mdpi.com [mdpi.com]

- 14. Degradation Mechanisms of GaN HEMTs With p-Type Gate Under Forward Gate Bias Overstress | IEEE Journals & Magazine | IEEE Xplore [ieeexplore.ieee.org]

- 15. Threshold Voltage Instability in GaN HEMTs With p-Type Gate: Mg Doping Compensation | IEEE Journals & Magazine | IEEE Xplore [ieeexplore.ieee.org]

- 16. researchgate.net [researchgate.net]

- 17. Effects of forward gate bias stressing on the leakage current of AlGaN/GaN high electron mobility transistors: Abstract, Citation (BibTeX) & Reference | Bohrium [bohrium.com]

- 18. Gate Leakage Current in GaN HEMTâ Approach [article.sapub.org]

- 19. Impact of high temperature reverse bias (HTRB) stress on the degradation of AlGaN/GaN HEMTs | Semantic Scholar [semanticscholar.org]

- 20. researchgate.net [researchgate.net]

- 21. researchgate.net [researchgate.net]

- To cite this document: BenchChem. [Gate degradation mechanisms in GaN HEMTs under stress.]. BenchChem, [2025]. [Online PDF]. Available at: [https://www.benchchem.com/product/b1216216#gate-degradation-mechanisms-in-gan-hemts-under-stress]

#### **Disclaimer & Data Validity:**

The information provided in this document is for Research Use Only (RUO) and is strictly not intended for diagnostic or therapeutic procedures. While BenchChem strives to provide accurate protocols, we make no warranties, express or implied, regarding the fitness of this product for every specific experimental setup.

**Technical Support:** The protocols provided are for reference purposes. Unsure if this reagent suits your experiment? [Contact our Ph.D. Support Team for a compatibility check]

Need Industrial/Bulk Grade? Request Custom Synthesis Quote

### BenchChem

Our mission is to be the trusted global source of essential and advanced chemicals, empowering scientists and researchers to drive progress in science and industry.

#### Contact

Address: 3281 E Guasti Rd

Ontario, CA 91761, United States

Phone: (601) 213-4426

Email: info@benchchem.com