# Gallium Arsenide (GaAs) Solar Cell Efficiency: Technical Support Center

Author: BenchChem Technical Support Team. Date: December 2025

This technical support center provides researchers, scientists, and drug development professionals with troubleshooting guides and frequently asked questions (FAQs) to address common challenges encountered during the fabrication and characterization of **gallium arsenide** (GaAs) solar cells.

## **Troubleshooting Guide**

This guide provides solutions to common problems that can arise during the experimental process of fabricating and testing GaAs solar cells.

Check Availability & Pricing

| Problem/Observation               | Potential Cause                                                                                                                                                                                                                                                                                                                                        | Suggested Solution                                                                                                                                                                                                                                                                                                                                                                                                                  |

|-----------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

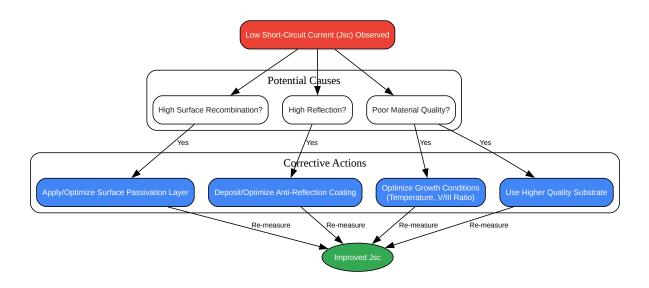

| Low Short-Circuit Current (Jsc)   | 1. High Surface Recombination: Surface defects and dangling bonds can act as recombination centers.[1][2] 2. Inadequate Light Absorption: The active layer may be too thin, or there could be high reflection from the cell surface.[3][4][5] 3. Material Defects: Crystal defects such as dislocations can reduce minority carrier lifetime.[6][7][8] | 1. Surface Passivation: Apply a passivation layer such as AlGaAs, silicon nitride, or employ sulfur passivation techniques.[1][9] 2. Anti-Reflection Coating (ARC): Deposit a single or double-layer ARC (e.g., SiO2, TiO2, or nanostructured coatings) to minimize reflection.[3][10][11] Optimize the thickness of the active layer. 3. Substrate Optimization: Use high-quality substrates with low dislocation densities.[6][7] |

| Low Open-Circuit Voltage<br>(Voc) | 1. High Dislocation Density: Dislocations can create shunt paths and increase recombination.[12][13] 2. Interface Defects: Defects at the heterointerfaces can lead to increased recombination. 3. Contamination: Impurities introduced during fabrication can act as traps.[14]                                                                       | 1. Buffer Layer Growth: Grow a buffer layer between the substrate and the active layers to reduce threading dislocations. 2. Growth Optimization: Optimize MOVPE/MOCVD growth parameters (temperature, V/III ratio) to improve crystal quality. [15][16] 3. Cleanroom Practices: Adhere to strict cleanroom protocols to minimize contamination.                                                                                    |

| Low Fill Factor (FF)              | High Series Resistance:     Poor ohmic contacts or high     resistance in the emitter or     base layers.[17][18][19] 2.     Shunt Resistance: Presence of     shunt paths due to material     defects or fabrication issues.                                                                                                                          | Contact Annealing: Optimize the annealing process for ohmic contacts to reduce contact resistance.[17] 2.  Mesa Etching: Ensure complete isolation of individual cells through proper mesa                                                                                                                                                                                                                                          |

|                                              | [12] 3. Non-ideal Diode Behavior: High ideality factor due to recombination in the depletion region.                                                              | etching to prevent shunt paths.  3. Material Quality: Improve the quality of the p-n junction to reduce recombination.                                                |

|----------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Visible Surface Defects (e.g., oval defects) | Growth Conditions: Non-<br>optimal growth parameters<br>during Molecular Beam Epitaxy<br>(MBE) or MOVPE, or<br>contamination on the wafer<br>surface.[20]         | Substrate Preparation and Growth Optimization: Thoroughly clean the substrate before growth. Optimize growth rate, substrate temperature, and element flux ratio.[20] |

| Poor Anti-Reflection Performance             | Incorrect ARC Thickness or<br>Refractive Index: The<br>thickness and refractive index<br>of the ARC layer are not<br>optimized for the solar<br>spectrum.[10][11] | ARC Simulation and Optimization: Use simulation software to design the optimal single or double-layer ARC with appropriate materials and thicknesses.[10]             |

# Frequently Asked Questions (FAQs)

A curated list of frequently asked questions to provide quick answers to common queries regarding the enhancement of GaAs solar cell efficiency.

1. How can I reduce surface recombination in my GaAs solar cells?

Surface recombination is a significant loss mechanism in GaAs solar cells. Effective strategies to mitigate this include:

- Surface Passivation: Applying a thin layer of a wider bandgap material, such as Aluminum

Gallium Arsenide (AlGaAs), can create a potential barrier that confines minority carriers

away from the surface.[9] Other common passivation materials include silicon nitride and

techniques like sulfur passivation.[1]

- Window Layer: A high-quality, wide-bandgap window layer, typically AlGaAs, is crucial in heteroface structures to passivate the emitter surface.

2. What are the most effective anti-reflection coatings (ARCs) for GaAs solar cells?

To maximize light absorption, it is essential to minimize reflection. Effective ARC strategies include:

- Single-Layer ARC: Materials like Silicon Nitride (SiN<sub>x</sub>), Titanium Dioxide (TiO<sub>2</sub>), and Zinc Oxide (ZnO) are commonly used. The optimal thickness is typically a quarter-wavelength of the peak of the solar spectrum.[11]

- Double-Layer ARC: A combination of two materials with different refractive indices (e.g., SiO₂/ZnSe or Al₂O₃/ZrO₂) can provide broader-band anti-reflection, further enhancing light absorption across the solar spectrum.[10]

- Nanostructured ARCs: Recent research has shown that nanostructured coatings, such as those based on thermally oxidized gallium nanoparticles, can reduce reflectance by approximately 30% across the solar spectrum.[3]

- 3. What is the impact of threading dislocations on cell performance, and how can they be minimized?

Threading dislocations act as recombination centers, which can significantly reduce the minority carrier lifetime, short-circuit current (Jsc), and open-circuit voltage (Voc).[6][7][13] To minimize their impact:

- High-Quality Substrates: Start with substrates that have a low dislocation density.

- Buffer Layers: Grow a graded buffer layer, such as InGaP, between the substrate and the active layers of the solar cell to help filter out threading dislocations.

- Optimized Growth Conditions: Fine-tuning the growth parameters during MOVPE or MBE, such as temperature and V/III ratio, can improve the crystal quality and reduce the formation of dislocations.[15]

- 4. What are the key parameters to optimize during MOVPE/MOCVD growth for high-efficiency GaAs solar cells?

Optimizing the Metal-Organic Vapor Phase Epitaxy (MOVPE) or Metal-Organic Chemical Vapor Deposition (MOCVD) process is critical for achieving high-quality GaAs films. Key parameters include:

- Growth Temperature: This affects surface morphology and dopant incorporation. For GaSbon-GaAs, a growth temperature of around 525°C has been shown to yield high mobility and low background doping.[16]

- V/III Ratio: The ratio of Group V to Group III precursors influences the crystal quality and defect density.[15]

- Growth Rate: While higher growth rates can reduce production costs, they may also lead to a decrease in minority carrier lifetime. However, efficiencies of 24.5% have been achieved with growth rates as high as 120 µm/h.[21][22]

- Dopant Precursors and Flow Rates: The choice and flow rates of dopant precursors determine the carrier concentration in the emitter and base layers.

- 5. How do I choose the right characterization techniques for my GaAs solar cells?

A combination of optical, electrical, and structural characterization techniques is necessary to fully evaluate your solar cells:

- Current-Voltage (I-V) Measurement: This is the primary method to determine the key performance parameters: Voc, Jsc, FF, and efficiency.

- Quantum Efficiency (QE): This measurement reveals the cell's response to different wavelengths of light and can help identify losses due to reflection, recombination, or incomplete absorption.

- Scanning Electron Microscopy (SEM) and Atomic Force Microscopy (AFM): These techniques are used to examine the surface morphology and identify any growth defects.

- Photoluminescence (PL) and Electroluminescence (EL): These are powerful techniques for assessing material quality and identifying regions with high defect densities.

Deep-Level Transient Spectroscopy (DLTS): This technique can be used to characterize electronic defects and traps within the bandgap.[24]

## **Experimental Protocols**

Detailed methodologies for key experiments are provided below.

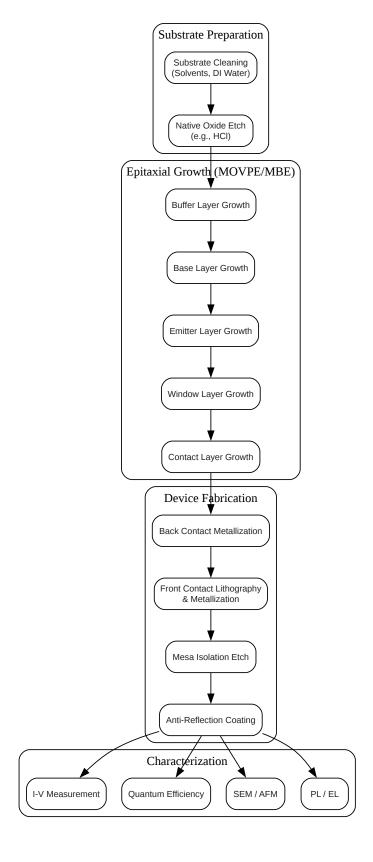

## Protocol 1: Fabrication of a Basic GaAs Solar Cell

This protocol outlines the fundamental steps for fabricating a p-n junction GaAs solar cell using MOVPE.

## 1. Substrate Preparation:

- Start with a high-quality n-type GaAs substrate.

- Degrease the substrate using a sequence of solvents (e.g., acetone, isopropanol, deionized water) in an ultrasonic bath.

- Perform a native oxide etch using a solution such as HCl:H2O (1:1) for 1-2 minutes.

- Rinse thoroughly with deionized water and dry with nitrogen gas.

#### 2. Epitaxial Growth (MOVPE):

- Load the substrate into the MOVPE reactor.

- Grow an n-type GaAs buffer layer to improve crystal quality.

- Grow the n-type GaAs base layer (typically 2-3 μm thick).

- Grow the p-type GaAs emitter layer (typically 0.1-0.5 μm thick).

- Grow a p-type AlGaAs window layer to passivate the emitter surface.

- Grow a heavily doped p-type GaAs contact layer.

#### 3. Metallization:

- Back Contact: Deposit an n-type ohmic contact (e.g., AuGe/Ni/Au) on the backside of the substrate using e-beam evaporation. Anneal to form the ohmic contact.

- Front Contact: Use photolithography to define the front grid pattern. Deposit a p-type ohmic contact (e.g., Ti/Pt/Au) using e-beam evaporation. Perform liftoff.

#### 4. Mesa Isolation:

Use photolithography to define the device area.

- Etch down to the n-type base layer using a wet chemical etch (e.g., H₃PO₄:H₂O₂:H₂O) to isolate individual cells.

- 5. Anti-Reflection Coating (ARC) Deposition:

- Deposit a single or double-layer ARC using plasma-enhanced chemical vapor deposition (PECVD) or a similar technique.

## Protocol 2: Current-Voltage (I-V) Characterization

This protocol describes the procedure for measuring the I-V characteristics of a fabricated GaAs solar cell.

#### 1. Equipment:

- Solar simulator with a calibrated AM1.5G spectrum.

- Source measure unit (SMU).

- Probe station with micro-manipulators.

- Temperature-controlled stage.

#### 2. Procedure:

- Place the fabricated solar cell on the temperature-controlled stage and maintain a constant temperature (e.g., 25°C).

- Contact the front and back metal contacts of the solar cell with the probes from the SMU.

- Illuminate the solar cell with the solar simulator at 1 sun intensity (100 mW/cm<sup>2</sup>).

- Sweep the voltage across the solar cell from a negative bias (reverse bias) to a voltage slightly above the expected Voc, and measure the corresponding current.

- · Record the I-V curve.

- From the I-V curve, extract the key parameters: Voc (the voltage at zero current), Jsc (the current at zero voltage, normalized to the cell area), and the maximum power point (Pmax).

- Calculate the Fill Factor (FF) using the formula: FF = Pmax / (Voc \* Isc).

- Calculate the power conversion efficiency ( $\eta$ ) using the formula:  $\eta$  = (Voc \* Jsc \* FF) / Pin, where Pin is the incident power density.

## **Data Presentation**

**Table 1: Impact of Anti-Reflection Coatings on GaAs**

**Solar Cell Performance**

| ARC Type           | Material(s)                               | Thickness<br>(nm) | Average<br>Reflectance<br>(%) | Efficiency<br>Improveme<br>nt (%) | Reference |

|--------------------|-------------------------------------------|-------------------|-------------------------------|-----------------------------------|-----------|

| Single-Layer       | TiO <sub>2</sub>                          | 62                | 9.5                           | -                                 | [11]      |

| Double-Layer       | SiO <sub>2</sub> /ZnSe                    | -                 | ~2                            | 49.81                             | [10]      |

| Nanostructur<br>ed | Thermally<br>Oxidized Ga<br>Nanoparticles | -                 | -                             | ~10 (in EQE<br>and Jsc)           | [3]       |

**Table 2: Effect of MOVPE Growth Rate on GaAs Solar**

**Cell Efficiency**

| Growth Rate (µm/h) | Efficiency (%) | Notes                                                          | Reference |

|--------------------|----------------|----------------------------------------------------------------|-----------|

| 56                 | -              | 4% degradation compared to baseline                            | [22]      |

| 60                 | -              | 0.8% absolute<br>efficiency degradation<br>compared to 14 μm/h | [15]      |

| 120                | 24.48          | Minority hole lifetime shortened                               | [21]      |

# **Visualizations**

Click to download full resolution via product page

GaAs Solar Cell Fabrication and Characterization Workflow

Click to download full resolution via product page

Troubleshooting Logic for Low Short-Circuit Current (Jsc)

#### **Need Custom Synthesis?**

BenchChem offers custom synthesis for rare earth carbides and specific isotopiclabeling.

Email: info@benchchem.com or Request Quote Online.

## References

- 1. fastercapital.com [fastercapital.com]

- 2. lup.lub.lu.se [lup.lub.lu.se]

- 3. pv-magazine.com [pv-magazine.com]

- 4. Anti Reflective Coating For GaAs Solar Cell [gaas.he-mu.com]

- 5. Efficiency Enhancement in GaAs Ultra-Thin Solar Cell Using Anti-Reflection Coating |

IEEE Conference Publication | IEEE Xplore [ieeexplore.ieee.org]

- 6. pubs.aip.org [pubs.aip.org]

- 7. [PDF] Impact of Threading Dislocations on the Design of GaAs and InGaP/GaAs Solar Cells on Si Using Finite Element Analysis | Semantic Scholar [semanticscholar.org]

- 8. Impact of threading dislocations on both n/p and p/n single junction GaAs cells grown on Ge/SiGe/Si substrates | IEEE Conference Publication | IEEE Xplore [ieeexplore.ieee.org]

- 9. Design of a Surface Passivation Scheme for Gallium Arsenide Nanowire Solar Cells [opg.optica.org]

- 10. Reflectance Minimization of GaAs Solar Cell with Single- and Double-Layer Anti-Reflection Coatings: A Simulation Study [mdpi.com]

- 11. pubs.aip.org [pubs.aip.org]

- 12. The effect of dislocations on the open-circuit voltage of gallium arsenide solar cells | Semantic Scholar [semanticscholar.org]

- 13. The effect of dislocations on the performance of gallium arsenide solar cells | IEEE Conference Publication | IEEE Xplore [ieeexplore.ieee.org]

- 14. ntrs.nasa.gov [ntrs.nasa.gov]

- 15. tnsc-innovation.com [tnsc-innovation.com]

- 16. pubs.aip.org [pubs.aip.org]

- 17. acta.uni-obuda.hu [acta.uni-obuda.hu]

- 18. [PDF] Contact Problems in GaAs-based Solar Cells | Semantic Scholar [semanticscholar.org]

- 19. researchgate.net [researchgate.net]

- 20. researchgate.net [researchgate.net]

- 21. tnsc-innovation.com [tnsc-innovation.com]

- 22. researchgate.net [researchgate.net]

- 23. dspace.vut.cz [dspace.vut.cz]

- 24. pubs.aip.org [pubs.aip.org]

- To cite this document: BenchChem. [Gallium Arsenide (GaAs) Solar Cell Efficiency: Technical Support Center]. BenchChem, [2025]. [Online PDF]. Available at: [https://www.benchchem.com/product/b074776#improving-the-efficiency-of-gallium-arsenide-solar-cells]

## **Disclaimer & Data Validity:**

The information provided in this document is for Research Use Only (RUO) and is strictly not intended for diagnostic or therapeutic procedures. While BenchChem strives to provide accurate protocols, we make no warranties, express or implied, regarding the fitness of this product for every specific experimental setup.

**Technical Support:** The protocols provided are for reference purposes. Unsure if this reagent suits your experiment? [Contact our Ph.D. Support Team for a compatibility check]

Need Industrial/Bulk Grade? Request Custom Synthesis Quote

# BenchChem

Our mission is to be the trusted global source of essential and advanced chemicals, empowering scientists and researchers to drive progress in science and industry.

#### Contact

Address: 3281 E Guasti Rd

Ontario, CA 91761, United States

Phone: (601) 213-4426

Email: info@benchchem.com