# GEM-5 Simulation Accuracy: A Comparative Analysis of ARM and x86 Architectures

Author: BenchChem Technical Support Team. Date: December 2025

| Compound of Interest |           |           |

|----------------------|-----------|-----------|

| Compound Name:       | GEM-5     |           |

| Cat. No.:            | B12410503 | Get Quote |

A detailed guide for researchers and scientists on the simulation fidelity of the **GEM-5** simulator for ARM and x86 instruction set architectures, supported by experimental data and standardized testing protocols.

The **GEM-5** simulator is a powerful and widely used tool in computer architecture research, enabling detailed performance and power analysis of various system designs. However, the accuracy of simulation results is paramount for drawing valid scientific conclusions. This guide provides an objective comparison of **GEM-5**'s accuracy when simulating ARM versus x86 architectures, drawing upon published validation studies. This analysis is intended to help researchers, scientists, and drug development professionals make informed decisions when using **GEM-5** for their simulation needs.

## **Comparative Accuracy Assessment**

Validation studies of **GEM-5** against real hardware have revealed varying levels of accuracy for ARM and x86 architectures. Generally, **GEM-5** has demonstrated a higher out-of-the-box accuracy for ARM-based systems, while achieving comparable fidelity for x86 architectures often requires significant configuration tuning and simulator modifications.

### **Quantitative Performance Metrics**

The following tables summarize the reported accuracy of **GEM-5** for both ARM and x86 architectures based on various performance metrics. The error rates are typically presented as

the Mean Absolute Percentage Error (MAPE) or Mean Percentage Error (MPE) when comparing simulated results to real hardware measurements.

Table 1: **GEM-5** Accuracy for ARM Architecture Simulation

| Hardware<br>Platform              | CPU Model                 | Benchmark<br>Suite               | Mean Absolute Percentage Error (Runtime)          | Mean<br>Percentage<br>Error<br>(Runtime) | Average Microarchit ectural Statistics Error |

|-----------------------------------|---------------------------|----------------------------------|---------------------------------------------------|------------------------------------------|----------------------------------------------|

| ARM Versatile Express TC2         | ARM Cortex-<br>A15        | SPEC<br>CPU2006                  | 13%[1]                                            | 5%[1]                                    | Within 20% for most statistics[1]            |

| ARM Versatile Express TC2         | ARM Cortex-<br>A15        | PARSEC<br>(single-core)          | 16%[1]                                            | -11%[1]                                  | Not Specified                                |

| ARM Versatile Express TC2         | ARM Cortex-<br>A15        | PARSEC<br>(dual-core)            | 17%[1]                                            | -12%[1]                                  | Not Specified                                |

| ARM Cortex-<br>A9 based<br>system | ARM Cortex-<br>A9         | SPLASH-2,<br>ALPBench,<br>STREAM | 1.39% to<br>17.94%[2]                             | Not Specified                            | Not Specified                                |

| Not Specified                     | In-order/Out-<br>of-order | 10<br>benchmarks                 | ~7% (in-<br>order), ~17%<br>(out-of-order)<br>[3] | Not Specified                            | Not Specified                                |

Table 2: **GEM-5** Accuracy for x86 Architecture Simulation

| Hardware<br>Platform       | CPU Model  | Benchmark<br>Suite           | Mean<br>Absolute<br>Percentage<br>Error (IPC) | Mean<br>Percentage<br>Error (IPC) | Notes                                                                               |

|----------------------------|------------|------------------------------|-----------------------------------------------|-----------------------------------|-------------------------------------------------------------------------------------|

| Intel Core-i7<br>(Haswell) | Custom OoO | Microbenchm<br>arks          | < 6%[4][5][6]                                 | Not Specified                     | After significant simulator modifications and tuning. Initial error was 136%.[4]    |

| Intel Core-i7<br>(Haswell) | Custom OoO | Embedded<br>Benchmarks       | 37.6%[7]                                      | Not Specified                     | Comparison with other simulators (Sniper: 20.6%, MARSSx86: 33.03%, ZSim: 24.3%) [7] |

| Intel Core-i7<br>(Haswell) | Custom OoO | Integer<br>Benchmarks        | 37.1%[7]                                      | Not Specified                     | Comparison with other simulators (Sniper: 17.6%, MARSSx86: 22.16%, ZSim: 22.59%)[7] |

| Intel Core-i7<br>(Haswell) | Custom OoO | Floating Point<br>Benchmarks | 35.4%[7]                                      | Not Specified                     | Comparison with other simulators (Sniper: 24.8%,                                    |

MARSSx86: 32.0%, ZSim: 27.5%)[7]

## **Experimental Protocols**

The accuracy of **GEM-5** is highly dependent on the experimental methodology used for validation. The key steps involved in a typical validation study are outlined below.

### **Hardware and Software Configuration**

A crucial first step is to configure the **GEM-5** simulator to match the target hardware as closely as possible. This includes:

- CPU Modeling: Selecting the appropriate CPU model (e.g., O3CPU for out-of-order processors) and configuring its parameters, such as pipeline stages, issue width, and instruction buffer sizes.

- Memory System: Modeling the cache hierarchy (L1, L2, L3 caches), including their sizes, associativities, and latencies, as well as the main memory system.

- Operating System and Kernel: In full-system simulation, using the same operating system and kernel version as the target hardware.

#### **Data Collection from Real Hardware**

To establish a ground truth for comparison, performance data is collected from the physical hardware. This is typically done using:

- Hardware Monitoring Counters (HMCs): Modern processors provide performance counters

that can be used to measure a wide range of microarchitectural events, such as instructions

retired, cache misses, and branch mispredictions.

- Performance Profiling Tools: Tools like perf in Linux are used to access and record the data from HMCs.[8]

## **Simulation and Data Analysis**

Once the simulator is configured and real hardware data is collected, the same benchmarks are run in **GEM-5**. The simulation output is then compared against the hardware measurements to calculate the error rates. Discrepancies are analyzed to identify the sources of inaccuracy in the simulation model.

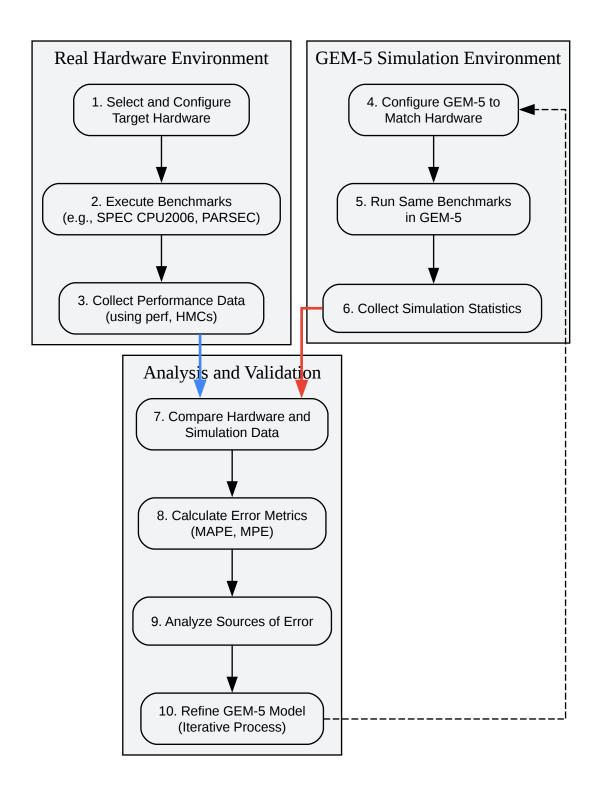

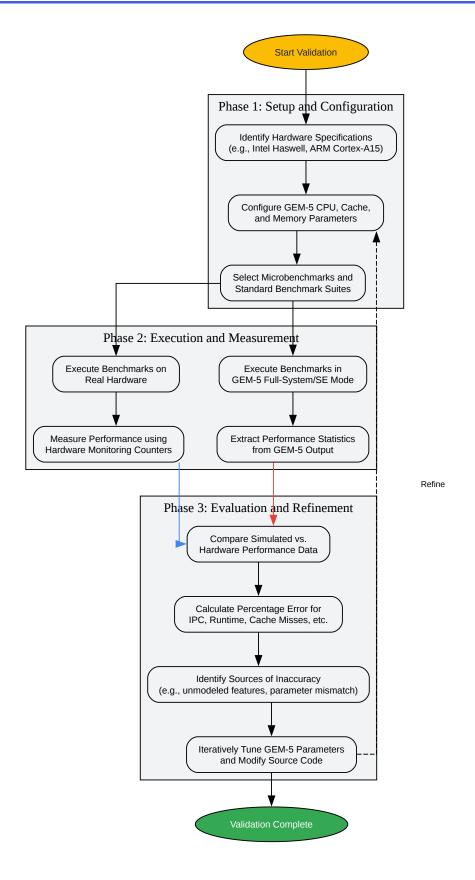

## **Visualization of Experimental Workflow**

The following diagrams illustrate the typical workflows for validating **GEM-5**'s accuracy.

Click to download full resolution via product page

Caption: A high-level overview of the **GEM-5** validation workflow.

Click to download full resolution via product page

Caption: A detailed methodology for **GEM-5** validation and accuracy assessment.

#### Conclusion

**GEM-5** is a versatile and powerful simulator for both ARM and x86 architectures. However, achieving high accuracy, particularly for complex out-of-order x86 processors, often requires a rigorous validation and tuning process. While **GEM-5** has shown good accuracy for ARM simulations in multiple studies, users should be aware of the potential for higher initial error rates when modeling x86 systems. By following a detailed experimental protocol, researchers can significantly improve the fidelity of their **GEM-5** simulations and gain greater confidence in their results. It is recommended to consult recent validation studies and, if possible, perform a custom validation against the specific hardware of interest to ensure the highest level of accuracy for your research.

#### **Need Custom Synthesis?**

BenchChem offers custom synthesis for rare earth carbides and specific isotopiclabeling.

Email: info@benchchem.com or Request Quote Online.

### References

- 1. tnm.engin.umich.edu [tnm.engin.umich.edu]

- 2. scholarworks.wmich.edu [scholarworks.wmich.edu]

- 3. youngcius.github.io [youngcius.github.io]

- 4. sc19.supercomputing.org [sc19.supercomputing.org]

- 5. Validation of the gem5 Simulator for x86 Architectures | IEEE Conference Publication | IEEE Xplore [ieeexplore.ieee.org]

- 6. scribd.com [scribd.com]

- 7. sc16.supercomputing.org [sc16.supercomputing.org]

- 8. conferences.computer.org [conferences.computer.org]

- To cite this document: BenchChem. [GEM-5 Simulation Accuracy: A Comparative Analysis of ARM and x86 Architectures]. BenchChem, [2025]. [Online PDF]. Available at: [https://www.benchchem.com/product/b12410503#assessing-the-accuracy-of-gem-5-for-arm-vs-x86-architecture-simulation]

#### **Disclaimer & Data Validity:**

The information provided in this document is for Research Use Only (RUO) and is strictly not intended for diagnostic or therapeutic procedures. While BenchChem strives to provide accurate protocols, we make no warranties, express or implied, regarding the fitness of this product for every specific experimental setup.

**Technical Support:** The protocols provided are for reference purposes. Unsure if this reagent suits your experiment? [Contact our Ph.D. Support Team for a compatibility check]

Need Industrial/Bulk Grade? Request Custom Synthesis Quote

## BenchChem

Our mission is to be the trusted global source of essential and advanced chemicals, empowering scientists and researchers to drive progress in science and industry. Contact

Address: 3281 E Guasti Rd

Ontario, CA 91761, United States

Phone: (601) 213-4426

Email: info@benchchem.com