# **GEM-5 Ruby Cache Coherence Simulation: Technical Support Center**

Author: BenchChem Technical Support Team. Date: December 2025

| Compound of Interest |           |           |

|----------------------|-----------|-----------|

| Compound Name:       | GEM-5     |           |

| Cat. No.:            | B12410503 | Get Quote |

This technical support center provides troubleshooting guidance and answers to frequently asked questions to assist researchers, scientists, and drug development professionals in optimizing their Ruby cache coherence protocol simulations within the **GEM-5** simulator.

## Frequently Asked Questions (FAQs)

Q1: What is the Ruby Memory Model and when should I use it over the "Classic" model?

A1: Ruby is a detailed memory system simulator within **GEM-5**, designed for the intricate modeling of cache coherence protocols and interconnection networks.[1][2] It provides a modular and flexible framework for exploring novel cache hierarchy designs and coherence protocols.[3][4] You should use Ruby when your research has a primary focus on the memory subsystem, such as evaluating changes to a coherence protocol or when the protocol's behavior could have a first-order impact on your results.[1][2] The "Classic" cache model, in contrast, implements a simpler, less flexible MOESI protocol and is suitable when detailed cache coherence is not a central aspect of the investigation.[2][5]

Q2: What are the fundamental components of a Ruby simulation?

A2: A Ruby simulation is constructed from several key components that interact to model the memory system. These include:

Controllers (State Machines): Defined using SLICC (Specification Language for Implementing Cache Coherence), these manage the state of cache blocks according to the

specific coherence protocol.[4][6]

- Sequencers: These act as the interface between the CPU and the Ruby cache hierarchy, issuing memory requests into the Ruby system.[3]

- Cache Memory: This component models the actual data and state storage of the caches.[7]

- Network: The interconnection network models the topology (e.g., Mesh, Crossbar) and links that connect the different cache and directory controllers.[3]

- Directory: In directory-based coherence protocols, the directory maintains the state of memory blocks and the identities of caches sharing them.

Q3: How do I select an appropriate cache coherence protocol for my simulation?

A3: The choice of protocol depends on your specific research goals and the system you are modeling. **GEM-5** includes several pre-defined protocols, such as MESI and MOESI, in both two-level and three-level cache hierarchies. For many-core systems, directory-based protocols (e.g., MOESI\_CMP\_directory) are generally more scalable than snoopy protocols. If you are designing a new protocol, you will need to define it using SLICC.[6] The key is to choose a protocol that accurately represents the class of system you are studying.

Q4: What is SLICC and why is it important for Ruby?

A4: SLICC, which stands for Specification Language for Implementing Cache Coherence, is a domain-specific language used to define the behavior of cache and directory controllers in Ruby.[4][6] It allows you to specify the states a cache block can be in, the events that can cause state transitions (e.g., a processor load, a snoop request), and the actions to be taken during these transitions.[4] Essentially, any cache coherence protocol simulated in Ruby is implemented as a set of SLICC state machine files.[3]

## Troubleshooting and Optimization Guides Issue: Simulation Performance is Unacceptably Slow

Q5: My Ruby simulation is taking too long to complete. What are the first steps to optimize its performance?

A5: Slow simulation speed is a common challenge. Performance can often be improved by tuning various simulation parameters, though this may involve a trade-off with simulation accuracy. The goal is to identify bottlenecks and reduce unnecessary detail where it doesn't impact your research outcomes.

Experimental Protocol: Performance Parameter Tuning

- Establish a Baseline: Run your simulation with a default configuration and record the execution time and key performance metrics (e.g., cache miss rates, average latency). This will serve as your baseline for comparison.

- Identify Bottlenecks: Use profiling tools if available, or analyze **GEM-5** statistics to determine where the simulation is spending the most time. Common bottlenecks include the network model and detailed CPU models.

- Iterative Parameter Adjustment: Modify one parameter at a time from the table below. Re-run the simulation and compare the execution time and results against your baseline.

- Analyze Trade-offs: Evaluate whether the gain in simulation speed justifies any potential loss

in accuracy for your specific experiment. For example, using a simpler network model might

be acceptable if you are not studying the interconnect itself.

- Document Changes: Keep a clear record of all parameter changes and their impact on both performance and results.

Table 1: Key Parameters for Performance Optimization

| Parameter<br>Category | Option/Parame<br>ter | Description                                                 | Impact on<br>Performance                                                    | Impact on<br>Accuracy                                                                       |

|-----------------------|----------------------|-------------------------------------------------------------|-----------------------------------------------------------------------------|---------------------------------------------------------------------------------------------|

| CPU Model             | cpu-type             | The model used for the processor cores.                     | TimingSimpleCP U is faster than the out-of-order O3CPU.                     | Lower fidelity with simpler models. O3CPU is more realistic for modern processors.          |

| Network Model         | network              | The interconnection network model.                          | simple is<br>significantly<br>faster than<br>garnet2.0.                     | garnet2.0 provides a detailed flit-level model, while simple uses fixed latencies.          |

| Cache Sizes           | l1d_size, l2_size    | The size of the<br>L1 data and L2<br>caches.                | Smaller caches can sometimes simulate faster due to fewer states to manage. | Directly impacts cache hit/miss rates and overall system performance.                       |

| Simulation<br>Warm-up | warmup-insts         | Number of instructions to simulate before collecting stats. | A shorter warm-<br>up reduces total<br>simulation time.                     | An insufficient warm-up may lead to inaccurate results as caches are not in a steady state. |

| Checkpointing         | take-checkpoint      | Saving the simulation state.                                | Taking<br>checkpoints adds<br>overhead.                                     | Restoring from a checkpoint can save significant time by skipping initialization phases.    |

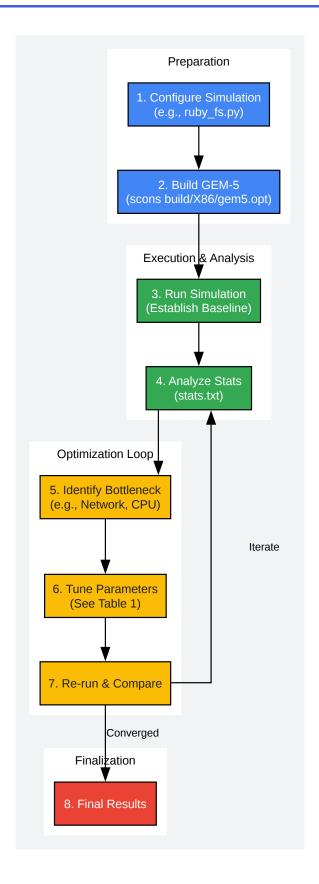

## **Workflow: Basic Simulation and Optimization**

A typical workflow for setting up and optimizing a **GEM-5** Ruby simulation involves configuration, execution, analysis, and iterative refinement.

Click to download full resolution via product page

Caption: A high-level workflow for **GEM-5** Ruby simulation and optimization.

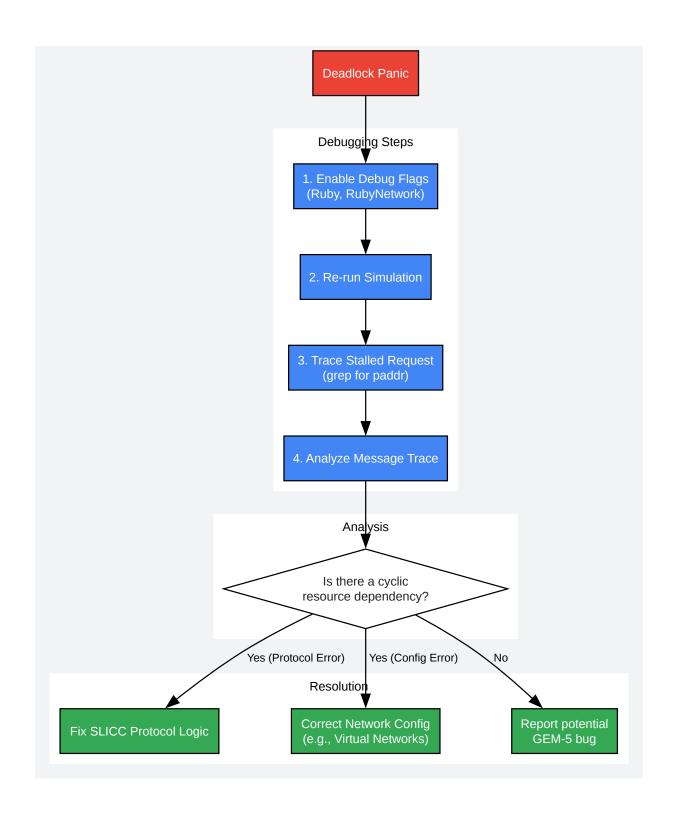

### Issue: Simulation Terminates with a Deadlock Panic

Q6: My simulation panicked with a "Possible Deadlock detected" error. What causes this and how can I debug it?

A6: Deadlocks in Ruby are often caused by cyclic dependencies in the network, where messages are waiting for resources that will never become available.[8] This can stem from errors in the SLICC protocol definition, incorrect network configuration, or bugs in the simulator itself.[8] Debugging deadlocks requires a methodical approach to trace the stalled messages and identify the resource dependency cycle.

Troubleshooting Steps for Deadlocks:

- Examine the Panic Message: The panic message often provides the time of the deadlock, the component where it was detected (e.g., a Sequencer), and the address of the problematic request.[8]

- Enable Ruby Debug Flags: Re-run the simulation with debug flags to get a detailed trace of protocol messages. Key flags include Ruby, RubyNetwork, and RubySlicc.

- --debug-flags=Ruby,RubyNetwork

- Trace the Stalled Request: Use the address from the panic message and grep the debug output to trace the lifecycle of the request. Identify which controller is holding the request and what resource it is waiting for.

- Visualize the Dependency: Manually draw out the message flow between the involved controllers (L1 caches, Directory, etc.). This will often reveal a circular wait condition, which is the hallmark of a deadlock. For example, Controller A is waiting for a message from B, while B is waiting for a message from A.

- Check Virtual Networks: Ensure that different message types (e.g., requests, responses) are mapped to different virtual networks to prevent head-of-line blocking, which is a common cause of deadlocks.

Click to download full resolution via product page

Caption: A structured workflow for troubleshooting deadlocks in Ruby.

## Issue: Simulation Crashes with a Fatal Error or Segfault

Q7: My simulation is crashing with a "fatal" error or a segmentation fault. What should I do?

A7: These errors typically point to an invalid simulation configuration or a bug in the C++ source code.[9]

- Fatal Errors: A fatal error is an explicit stop issued by **GEM-5** when it detects an unrecoverable problem, such as an unconnected port or an invalid parameter.[9] The error message usually indicates the source file and line number where the error was triggered, which is the best place to start your investigation.[9]

- Segmentation Faults: A segfault indicates an illegal memory access. These are often harder to debug but can be traced using a debugger like GDB. Running **GEM-5** with GDB will allow you to get a backtrace at the point of the crash to identify the faulty code path.[9]

#### General Debugging Protocol:

- Isolate the Change: Identify the most recent change you made to your configuration script or the GEM-5 source. Revert it to see if the error disappears.

- Check Configuration Scripts: Carefully review your Python configuration files. The most common cause of fatal errors is an incorrect setup, such as mismatched component interfaces or invalid parameters passed to a SimObject.[9]

- Use a Debugger (for Segfaults): Launch GEM-5 within GDB: gdb --args build/X86/gem5.opt

Once it crashes, use the bt (backtrace) command to see the function call stack that led to the error.

- Consult the Community: Search the gem5-users mailing list archives. It is likely that another user has encountered a similar issue.

#### **Need Custom Synthesis?**

BenchChem offers custom synthesis for rare earth carbides and specific isotopiclabeling.

Email: info@benchchem.com or Request Quote Online.

### References

- 1. gem5: Adding cache to configuration script [gem5.org]

- 2. Adding cache to the configuration script gem5 Tutorial 0.1 documentation [courses.grainger.illinois.edu]

- 3. gem5: Introduction [gem5.org]

- 4. gem5: Introduction to Ruby [gem5.org]

- 5. Analyzing the Benefits of More Complex Cache Replacement Policies in Moderns GPU LLCs | NSF Public Access Repository [par.nsf.gov]

- 6. project-archive.inf.ed.ac.uk [project-archive.inf.ed.ac.uk]

- 7. youtube.com [youtube.com]

- 8. Deadlock problem with Ruby in the newest Gem5 [gem5-users.gem5.narkive.com]

- 9. gem5: Common errors within gem5 [gem5.org]

- To cite this document: BenchChem. [GEM-5 Ruby Cache Coherence Simulation: Technical Support Center]. BenchChem, [2025]. [Online PDF]. Available at: [https://www.benchchem.com/product/b12410503#optimizing-ruby-cache-coherence-protocol-simulations-in-gem-5]

#### **Disclaimer & Data Validity:**

The information provided in this document is for Research Use Only (RUO) and is strictly not intended for diagnostic or therapeutic procedures. While BenchChem strives to provide accurate protocols, we make no warranties, express or implied, regarding the fitness of this product for every specific experimental setup.

**Technical Support:**The protocols provided are for reference purposes. Unsure if this reagent suits your experiment? [Contact our Ph.D. Support Team for a compatibility check]

Need Industrial/Bulk Grade? Request Custom Synthesis Quote

## BenchChem

Our mission is to be the trusted global source of essential and advanced chemicals, empowering scientists and researchers to drive progress in science and industry. Contact

Address: 3281 E Guasti Rd

Ontario, CA 91761, United States

Phone: (601) 213-4426

Email: info@benchchem.com