# Benchmarking TeO Thin-Film Transistor Performance: A Comparative Guide

Author: BenchChem Technical Support Team. Date: December 2025

In the rapidly evolving field of large-area electronics, the demand for high-performance, low-cost, and stable thin-film transistors (TFTs) is paramount. While n-type metal oxide semiconductors like indium-gallium-zinc-oxide (IGZO) have dominated the market, the development of efficient p-type counterparts has been a significant challenge, hindering the advancement of low-power complementary metal-oxide-semiconductor (CMOS) technology.[1] Recently, tellurium oxide (TeO) has emerged as a promising p-type semiconductor, demonstrating competitive performance characteristics. This guide provides a comprehensive comparison of TeO TFTs with established technologies, supported by experimental data and detailed methodologies, to aid researchers, scientists, and drug development professionals in evaluating its potential.

## **Performance Benchmarking**

The performance of a TFT is evaluated based on several key metrics. The following tables summarize the reported performance of various TeO-based TFTs and compare them with leading alternative technologies.

Table 1: Performance Metrics of TeO-based Thin-Film Transistors

| Semicondu<br>ctor                              | Deposition<br>Method | Mobility<br>(cm²/Vs) | On/Off<br>Ratio        | Threshold<br>Voltage (V) | Subthresho<br>Id Swing<br>(mV/dec) |

|------------------------------------------------|----------------------|----------------------|------------------------|--------------------------|------------------------------------|

| α-TeO <sub>2</sub>                             | Evaporation          | ~35                  | ~104                   | ~0                       | 108                                |

| Te (with Al₂O₃<br>encapsulation<br>)           | Sputtering           | 30.9                 | 5.8 x 10⁵              | -                        | -                                  |

| Te (with organic-inorganic hybrid passivation) | Sputtering           | 13.6                 | 1.35 x 10 <sup>4</sup> | -                        | 6150                               |

| TeO <sub>×</sub> (Heat-treated)                | Sputtering           | -                    | >106                   | < -2                     | -                                  |

Table 2: Performance Comparison with Alternative TFT Technologies

| Semicondu<br>ctor | Туре          | Mobility<br>(cm²/Vs) | On/Off<br>Ratio                   | Processing<br>Temperatur<br>e | Key<br>Advantages                                         |

|-------------------|---------------|----------------------|-----------------------------------|-------------------------------|-----------------------------------------------------------|

| TeO-based         | p-type        | 13.6 - 35            | 10 <sup>4</sup> - 10 <sup>6</sup> | Room Temp.<br>- 250°C         | High p-type<br>mobility, low<br>processing<br>temperature |

| a-Si:H            | n-type        | 0.1 - 1              | ~106                              | ~250-350°C                    | Low cost,<br>mature<br>technology                         |

| LTPS              | n-type/p-type | 20 - 500             | >106                              | >450°C                        | High mobility<br>and<br>resolution                        |

| IGZO              | n-type        | 10 - 50              | >107                              | Room Temp.<br>- 300°C         | High<br>uniformity,<br>low off-<br>current                |

## **Experimental Protocols**

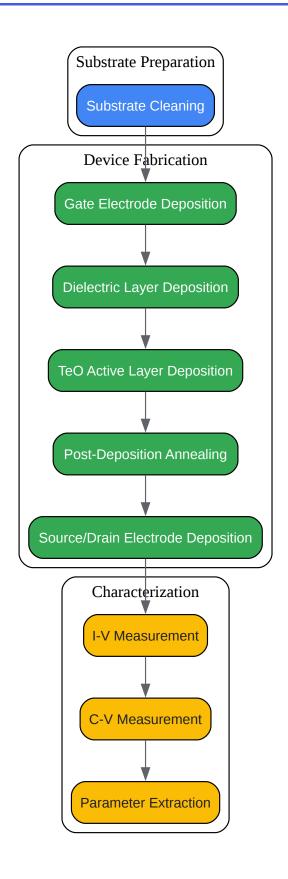

Detailed methodologies are crucial for reproducing and building upon existing research. This section outlines the typical fabrication and characterization procedures for TeO TFTs.

## **Fabrication of TeO Thin-Film Transistors**

A common method for fabricating TeO TFTs is through physical vapor deposition (PVD), such as thermal evaporation or sputtering. A typical bottom-gate, top-contact device structure is fabricated as follows:

• Substrate Cleaning: The process begins with the thorough cleaning of a substrate, typically glass or a silicon wafer with a SiO<sub>2</sub> layer. Standard cleaning procedures involve sequential ultrasonication in acetone, isopropyl alcohol, and deionized water, followed by drying with nitrogen gas.

- Gate Electrode Deposition: A gate electrode, commonly made of metals like chromium (Cr) or aluminum (Al), is deposited onto the substrate using thermal evaporation or sputtering and patterned using photolithography and lift-off or etching.

- Dielectric Layer Deposition: A gate dielectric layer, such as aluminum oxide (Al<sub>2</sub>O<sub>3</sub>) or hafnium oxide (HfO<sub>2</sub>), is deposited over the gate electrode. Atomic layer deposition (ALD) is often preferred for this step as it allows for the formation of high-quality, pinhole-free insulating layers at relatively low temperatures.

- TeO Active Layer Deposition: The p-type TeO semiconductor layer is deposited.

- Thermal Evaporation: High-purity TeO<sub>2</sub> powder is used as the source material. The substrate is placed in a high-vacuum chamber, and the source is heated until it sublimes, depositing a thin film of TeO onto the substrate. The substrate temperature during deposition is a critical parameter that influences the film's properties.

- Sputtering: A tellurium (Te) or tellurium oxide (TeO<sub>2</sub>) target is used. The deposition is

carried out in a controlled atmosphere of argon (Ar) and oxygen (O<sub>2</sub>). The ratio of Ar to O<sub>2</sub>

and the sputtering power are key parameters to control the stoichiometry and quality of the

deposited film.

- Post-Deposition Annealing: The fabricated device is often annealed in a controlled atmosphere (e.g., air, oxygen, or nitrogen) at temperatures typically ranging from 150°C to 250°C. This step is crucial for improving the film quality, reducing defects, and enhancing the electrical performance of the TFT.

- Source/Drain Electrode Deposition: Finally, source and drain electrodes, typically made of gold (Au) or nickel (Ni), are deposited and patterned on top of the TeO layer to complete the TFT structure.

## **Electrical Characterization**

The performance of the fabricated TeO TFTs is evaluated by measuring their electrical characteristics using a semiconductor parameter analyzer in a shielded probe station to minimize electrical noise.

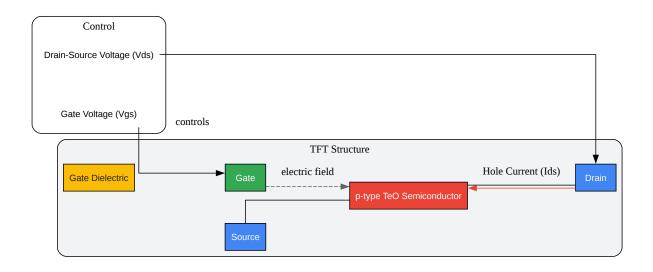

Current-Voltage (I-V) Characteristics:

- Output Characteristics (IDS-VDS): The drain current (IDS) is measured as a function of the drain-source voltage (VDS) for various gate-source voltages (VGS). These curves provide information about the transistor's operating mode (linear and saturation regions) and contact resistance.

- Transfer Characteristics (IDS-VGS): The drain current (IDS) is measured as a function of the gate-source voltage (VGS) at a constant drain-source voltage (VDS). From this measurement, key performance metrics are extracted:

- Field-Effect Mobility (μ): Calculated from the transconductance in the linear region.

- On/Off Ratio: The ratio of the maximum on-state current to the minimum off-state current.

- Threshold Voltage (Vth): The gate voltage at which the transistor begins to conduct.

- Subthreshold Swing (SS): The change in gate voltage required to change the drain current by one decade in the subthreshold region.

- Capacitance-Voltage (C-V) Characteristics:

- The capacitance between the gate and the source/drain terminals is measured as a function of the gate voltage. C-V measurements are used to determine the gate dielectric capacitance, which is necessary for accurate mobility calculations, and to probe the density of interface traps.

## **Mandatory Visualizations**

To further elucidate the experimental workflow and the fundamental operation of a TFT, the following diagrams are provided.

Click to download full resolution via product page

TFT Fabrication and Characterization Workflow

Click to download full resolution via product page

#### TFT Operation Principle

#### **Need Custom Synthesis?**

BenchChem offers custom synthesis for rare earth carbides and specific isotopiclabeling.

Email: info@benchchem.com or Request Quote Online.

## References

- 1. pubs.acs.org [pubs.acs.org]

- To cite this document: BenchChem. [Benchmarking TeO Thin-Film Transistor Performance: A Comparative Guide]. BenchChem, [2025]. [Online PDF]. Available at: [https://www.benchchem.com/product/b13737309#benchmarking-teo-thin-film-transistor-performance]

#### **Disclaimer & Data Validity:**

The information provided in this document is for Research Use Only (RUO) and is strictly not intended for diagnostic or therapeutic procedures. While BenchChem strives to provide accurate protocols, we make no warranties, express or implied, regarding the fitness of this product for every specific experimental setup.

**Technical Support:** The protocols provided are for reference purposes. Unsure if this reagent suits your experiment? [Contact our Ph.D. Support Team for a compatibility check]

Need Industrial/Bulk Grade? Request Custom Synthesis Quote

# BenchChem

Our mission is to be the trusted global source of essential and advanced chemicals, empowering scientists and researchers to drive progress in science and industry. Contact

Address: 3281 E Guasti Rd

Ontario, CA 91761, United States

Phone: (601) 213-4426

Email: info@benchchem.com