# Applications of Phosphorus Oxides in Semiconductor Manufacturing: Application Notes and Protocols

Author: BenchChem Technical Support Team. Date: December 2025

| Compound of Interest |                      |           |

|----------------------|----------------------|-----------|

| Compound Name:       | phosphorus(IV) oxide |           |

| Cat. No.:            | B1197065             | Get Quote |

For Researchers, Scientists, and Drug Development Professionals

This document provides detailed application notes and experimental protocols for the use of phosphorus oxides and their derivatives in semiconductor manufacturing. The primary applications covered are the n-type doping of silicon substrates and the deposition of phosphosilicate glass (PSG) as a dielectric layer. While diphosphorus tetroxide (P<sub>2</sub>O<sub>4</sub>) is a specific oxide of phosphorus, in semiconductor processing, phosphorus is typically introduced using more common and controllable sources like phosphorus oxychloride (POCl<sub>3</sub>) and solid planar dopant sources containing phosphorus pentoxide (P<sub>2</sub>O<sub>5</sub>). These precursors lead to the formation of phosphorus-rich layers that are essential for creating n-type regions in silicon wafers.

# N-Type Doping of Silicon using Phosphorus Oxychloride (POCl<sub>3</sub>)

The introduction of phosphorus atoms into the silicon crystal lattice creates n-type semiconductor material by providing an excess of free electrons.[1][2] This process, known as doping, is fundamental to the fabrication of various electronic devices, including transistors and solar cells.[3] A widely used and highly controllable method for phosphorus doping is thermal diffusion using a liquid POCl<sub>3</sub> source.[1][4]

The process generally involves two key steps: a pre-deposition step where a phosphosilicate glass (PSG) layer is formed on the silicon surface, and a drive-in step where the phosphorus from the PSG layer diffuses into the silicon wafer.[5][6]

#### Experimental Protocol: POCl3 Diffusion

This protocol describes a typical two-step diffusion process for creating an n-type emitter in a ptype silicon wafer in a horizontal tube furnace.

- 1. Wafer Preparation:

- Start with clean, p-type silicon wafers.

- Perform a standard pre-diffusion clean to remove any organic and inorganic contaminants from the wafer surface.

- 2. Furnace Preparation:

- The diffusion furnace should be profiled to ensure a stable and uniform temperature across the process zone.

- A typical diffusion process is carried out at temperatures ranging from 800°C to 1000°C.[1][5]

- 3. Pre-deposition Step:

- Load the silicon wafers into a quartz boat and insert them into the diffusion tube.

- Stabilize the furnace at the desired deposition temperature (e.g., 840°C).[7]

- Introduce a carrier gas, typically nitrogen (N₂), through a bubbler containing liquid POCl₃

maintained at a constant temperature.

- Simultaneously, introduce oxygen (O<sub>2</sub>) into the furnace tube.

- The reaction of POCl₃ and O₂ at high temperatures forms phosphorus pentoxide (P₂O₅) on the silicon wafer surface, which then reacts with the silicon to form a phosphosilicate glass (PSG) layer.[7]

- The duration of this step is typically between 15 to 30 minutes.[7]

- 4. Drive-in Step:

- After the pre-deposition, the POCl<sub>3</sub> source is turned off.

- The temperature of the furnace is often ramped up to a higher temperature (e.g., 850°C to 1050°C) for the drive-in.[5][8]

- An inert gas (N<sub>2</sub>) and a controlled amount of oxygen are maintained in the furnace.

- The drive-in step allows the phosphorus atoms from the PSG layer to diffuse deeper into the silicon substrate. The duration of this step can range from 30 to 60 minutes, depending on the desired junction depth.[8]

- 5. Deglaze:

- After the drive-in process, the wafers are slowly pulled from the furnace.

- The PSG layer formed on the surface is typically removed using a hydrofluoric acid (HF) solution (e.g., 10:1 diluted HF).[6]

# Data Presentation: Impact of POCl₃ Diffusion Parameters

The following table summarizes the qualitative and quantitative effects of key process parameters on the resulting n-type doped layer.

| Process Parameter          | Typical Range                | Effect on Doping Profile                                                                                                                                                                    | Resulting<br>Properties                                                                                                                                               |

|----------------------------|------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Deposition<br>Temperature  | 795°C - 880°C                | Higher temperature increases the solid solubility of phosphorus in silicon, leading to a higher surface concentration.                                                                      | Increasing temperature from 795°C to 880°C can decrease sheet resistance and increase junction depth.[4]                                                              |

| Drive-in Temperature       | 850°C - 1050°C               | Higher drive-in temperatures increase the diffusion coefficient of phosphorus, resulting in a deeper junction.                                                                              | A longer drive-in at a higher temperature leads to a lower sheet resistance and a deeper emitter profile.                                                             |

| POCl₃:O₂ Gas Flow<br>Ratio | 350:600 to 450:600<br>(sccm) | A higher POCl <sub>3</sub> :O <sub>2</sub> ratio during deposition results in a higher phosphorus concentration in the PSG layer, leading to a higher surface concentration on the silicon. | Increasing the POCl <sub>3</sub> :O <sub>2</sub> ratio from 350:600 to 450:600 can decrease sheet resistance from 83 $\Omega/\text{sq}$ to 68 $\Omega/\text{sq}$ .[4] |

| Drive-in Duration          | 40 - 80 minutes              | A longer drive-in time allows for deeper diffusion of phosphorus into the silicon.                                                                                                          | Increasing the drive-in time from 40 to 80 minutes can increase the junction depth from 0.35 µm to 0.45 µm.[4]                                                        |

## **Process Flow Diagram: N-Type Doping with POCl₃**

Click to download full resolution via product page

N-type doping process flow using POCl<sub>3</sub>.

### **Phosphosilicate Glass (PSG) Deposition**

Phosphosilicate glass (PSG) is a form of silicon dioxide that contains phosphorus. It is widely used in semiconductor manufacturing as a dielectric layer for insulation between metal layers, for surface passivation, and as a gettering agent to trap mobile ionic contaminants.[9] PSG can be deposited using various chemical vapor deposition (CVD) techniques, including atmospheric pressure CVD (APCVD), low-pressure CVD (LPCVD), and plasma-enhanced CVD (PECVD). [10]

#### **Experimental Protocol: PECVD of PSG using TEOS**

This protocol outlines the deposition of a PSG film using a plasma-enhanced chemical vapor deposition (PECVD) system with tetraethylorthosilicate (TEOS) as the silicon source and trimethylphosphite (TMP) as the phosphorus source.

- 1. System Preparation:

- Ensure the PECVD chamber is clean and has been properly conditioned.

- Set the substrate holder to the desired deposition temperature, typically between 300°C and 400°C.[11]

- 2. Wafer Loading:

- Place the silicon wafer on the substrate holder in the PECVD chamber.

- Evacuate the chamber to the base pressure.

- 3. Deposition Process:

- Introduce the precursor gases into the chamber. The gas flow rates are critical for controlling the film's stoichiometry.

- TEOS is typically delivered by bubbling an inert carrier gas (e.g., Helium) through the liquid precursor.

- TMP is also delivered using a carrier gas.

- Oxygen (O<sub>2</sub>) is used as the oxidant.

- Set the process pressure, typically in the range of 1 to 10 Torr.[11]

- Ignite the plasma by applying RF power to the electrodes. The RF power density influences

the film's properties.

- The deposition time will determine the final thickness of the PSG film.

- 4. Post-Deposition:

- After the desired thickness is achieved, turn off the RF power and the gas flows.

- Purge the chamber with an inert gas like nitrogen.

- Allow the wafer to cool before removing it from the chamber.

#### **Data Presentation: PECVD PSG Deposition Parameters**

The following table provides typical process parameters for the PECVD of PSG and their influence on film properties.

| Process Parameter        | Typical Range                                        | Effect on Film Properties                                                                                                              |

|--------------------------|------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------|

| Substrate Temperature    | 300°C - 400°C                                        | Affects film density and stress.  Higher temperatures generally lead to denser films.                                                  |

| RF Power                 | 300 - 500 W                                          | Influences the deposition rate and film uniformity.                                                                                    |

| Pressure                 | 1 - 10 Torr                                          | Affects the plasma chemistry and the conformality of the deposited film.                                                               |

| TEOS Flow Rate           | Varies with bubbler temperature and carrier gas flow | Primarily controls the silicon dioxide deposition rate.                                                                                |

| TMP Flow Rate            | Varies with bubbler temperature and carrier gas flow | Controls the phosphorus concentration in the PSG film. Increasing TMP flow increases the phosphorus content.[12]                       |

| O <sub>2</sub> Flow Rate | Varies                                               | Ensures complete oxidation of<br>the precursors. The O <sub>2</sub> :TEOS<br>ratio can affect the film's<br>electrical properties.[11] |

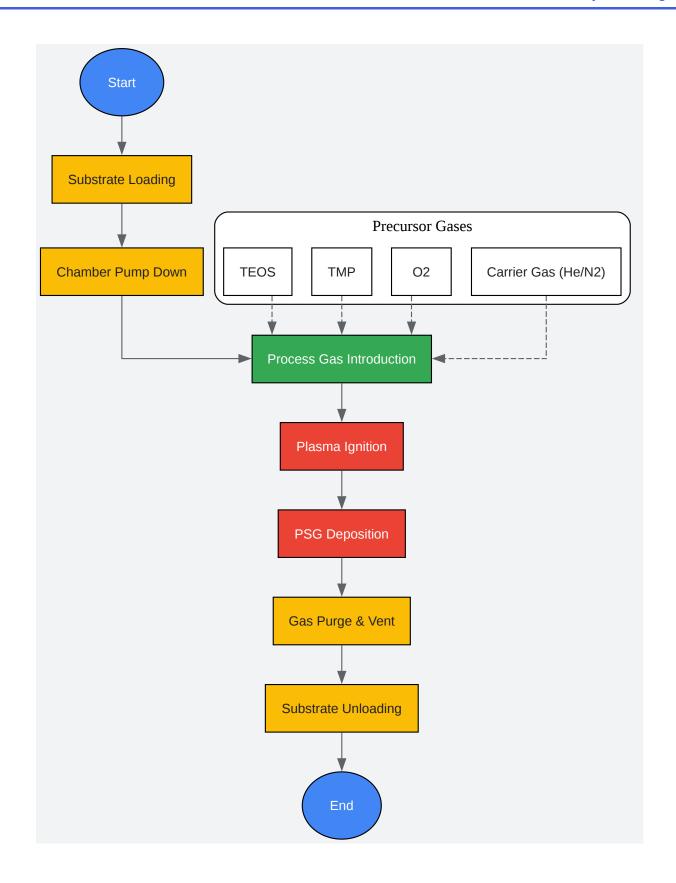

### **Process Flow Diagram: PECVD of PSG**

Click to download full resolution via product page

PECVD process for PSG deposition.

#### **Need Custom Synthesis?**

BenchChem offers custom synthesis for rare earth carbides and specific isotopiclabeling.

Email: info@benchchem.com or Request Quote Online.

#### References

- 1. The Complete Guide to Doping in Semiconductors: What Is it and Why Is it Necessary? [waferworld.com]

- 2. quora.com [quora.com]

- 3. researchgate.net [researchgate.net]

- 4. 2024.sci-hub.se [2024.sci-hub.se]

- 5. Efficiency Improvement of Industrial Silicon Solar Cells by the POCI3 Diffusion Process PMC [pmc.ncbi.nlm.nih.gov]

- 6. ECE Illinois ece444: Phosphosilicate Glass Etch Process [fabweb.ece.illinois.edu]

- 7. d-nb.info [d-nb.info]

- 8. onsemi.com [onsemi.com]

- 9. Phosphosilicate glass Wikipedia [en.wikipedia.org]

- 10. cns1.rc.fas.harvard.edu [cns1.rc.fas.harvard.edu]

- 11. Electrical characterization of doped and undoped PECVD TEOS oxides | IEEE Conference Publication | IEEE Xplore [ieeexplore.ieee.org]

- 12. "Synthesis and characterization of phosphosilicate glass films by LPCVD" by Hui Wu [digitalcommons.njit.edu]

- To cite this document: BenchChem. [Applications of Phosphorus Oxides in Semiconductor Manufacturing: Application Notes and Protocols]. BenchChem, [2025]. [Online PDF].

Available at: [https://www.benchchem.com/product/b1197065#applications-of-p204-in-semiconductor-manufacturing]

#### **Disclaimer & Data Validity:**

The information provided in this document is for Research Use Only (RUO) and is strictly not intended for diagnostic or therapeutic procedures. While BenchChem strives to provide

accurate protocols, we make no warranties, express or implied, regarding the fitness of this product for every specific experimental setup.

**Technical Support:** The protocols provided are for reference purposes. Unsure if this reagent suits your experiment? [Contact our Ph.D. Support Team for a compatibility check]

Need Industrial/Bulk Grade? Request Custom Synthesis Quote

#### BenchChem

Our mission is to be the trusted global source of essential and advanced chemicals, empowering scientists and researchers to drive progress in science and industry. Contact

Address: 3281 E Guasti Rd

Ontario, CA 91761, United States

Phone: (601) 213-4426

Email: info@benchchem.com